Запоминающее устройство

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК 5114 G ll С 7700

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМ У СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3633242/24-24 (22) 09.08.83 (46) 07.01.86. Бюл. № 1 (72) С. М. Игнатьев, Н. В. Бабенко, О. А. Мызгин, В. А. Неклюдов и А. Э. Нестеров (53) 681.327.66 (088.8) (56) Патент США № 4.122.542, кл. 365 — 156, опублик. 24.10.78.

IEEE international Solid — State Civcuits

С on feren se, 1980, р. 222, 223. (54) (57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее матрицу элементов памяти, входы элементов памяти каждой строки ко; эрой являются входами выборки устрой тва, усилители считывания, каждый из которых состоит из первого и второго транзисторов, базы которых подключены соответственно к первым и вторым выходам

„„SU„„1203592 A элементов памяти соответствующего столбца матрицы, а коллекторы являются соответственно первым и вторым выходами устройства, первый и второй дегпифраторы выборки столбцов, входы которых являются адресными входами устройства, источник тока, первый вывод которого соединен с шиной питания, отличающееся тем, что, с целью упрощения схемы, эмиттеры транзисторов усилителей считывания подключены к второму выводу источника тока, выходы первого и второго дешифраторов выборки столбцов подключены соответственно к базам первых и вторых транзисторов усилителей считывания, а дополнительные входы первого и второго дешифраторов выборки столбцов являются соответственно прямым и инверсным информационными входами устройства.

1203592

Изобретение относится к вычислительной технике и предназначено для использования в биполярных статических оперативных запоминающих устройствах.

Целью изобретения является упрощение схемы запоминающего устройства за счет совмещения функций выборки информации и записи в двух дешифраторах выборки столбцов матрицы элементов памяти.

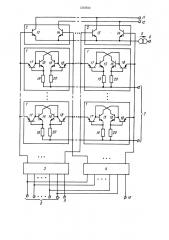

На чертеже изображена электрическая схема запоминающего устройства. 10

Запоминающее устройство содержит матрицу элементов 1 памяти, усилители 2 считывания, первый 3 и второй 4 дешифраторы выборки столбцов источник 5 тока, первый вывод которого соединен с шиной

6 напряжения питания. Входы элементов 15 памяти, составляющих строку матрицы, являются входами 7 выборки устройства. Входы первого 3 и второго 4 дешифраторов выборки столбцов являются адресными входами 8 устройства, а их дополнительные входы соответственно прямым 9 и инверсным 10 информационными входами устройства. Первый и второй выходы усилителей 2 считывания являются первыми 11 и вторыми 12 выходами запоминающего устройства соответственно. Каждый усилитель 2 считывания состоит из первого 13 и второго 14 транзисторов, базы которых подключены соответственно к первым и вторым выходам элементов 1 памяти соответствующего столбца матрицы, коллекторы являются соответственно первым и вторым выходами 30 устройства, а эмиттеры соединены с вторым выводом источника 5 тока. Выходы первого 3 и второго 4 дешифраторов выборки столбцов подключены соответственно к базам первых 13 и вторых 14 транзисторов усилителей считывания. 35

В качестве элемента 1 памяти в запоминающем устройстве может быть использован триггер ИЛИ типа, состоящий из первого 15 и второго 16 транзисторов первого типа проводимости с перекрестно связанными базовыми и коллекторными выводами, третьего 7 и четвертого 18 транзисторов второго типа проводимости и первого 19 и второго 20 резисторов, первые выводы которых являются входом элемента памяти.

Второй вывод резистора 19 подклк>чен к эмиттеру транзистора 15 и к базе транзистора 17, а второй вывод резистора 20 соединен с эмиттером транзистора 16 и с базой транзистора 18. Эмиттеры транзисторов 17 и 18 соответственно являются первым и вторым выходами элемента памя- 50 ти, а коллекторы подключены к базам транзисторов 15 и 16.

Устройство работает следующим образом.

В режиме хранения информации на входах 7 выборки установлены одинаковые напряжения низкого логического уровня, 2 а на всех выходах дешифраторов 3 и 4 выборки столбцов — одинаковые напряжения высокого логического уровня. При этом эмиттеры у всех транзисторов 17 и 18 элементов 1 памяти открыты. Транзисторы

17 и 18 выполняют функцию генераторов тока, а транзисторы 15 и 16 являются электронными ключами с перекрестно связанными входами и выходами.

В элементе памяти, в зависимости от его состояния, один из транзисторов 15, 16 закрыт, а другой находится в режиме насыщения и его базовым и коллекторным токами являются коллекторные токи транзисторов 17 и 18.

В режиме считывания информации для выборки нужного элемента памяти на всех входах 7 выборки, соответствующих невыбранным строкам матрицы, установлены высокие логические уровни, а на всех выходах дешифраторов выборки столбцов, соответствующих невыбранным столбцам — низкие логические уровни. При этом во всех невыбранных элементах памяти эмиттеры транзисторов 17 и 18 оказываются закрытыми и ток в коллекторах транзисторов

17 и 18 отсутствует, состояние элементов памяти сохраняется за счет сохранения напряжений на емкостях р-п переходов транзисторов. Выбранным является элемент памяти, который одновременно находится в выбранном столбце и в выбранной строке матрицы.

Выбранный элемент памяти продолжает работать так же, как в режиме хранения, а его состояние идентифицируется по соотношению потенциалов на вторых выходах резисторов 19 и 20, различие токов через которые определяется разностью эмиттерных токов транзисторов 15 и 16.

Разность напряжений на резисторах 19 и 20 транслируется через эмиттерные р-и переходы транзисторов 17 и 18 на базы транзисторов 13 и 14 усилителя 2 сравнения, соответствующего выбранному столбцу матрицы, уровни на базах транзисторов 13 и 14 других усилителей считывания лежат ниже и не препятствуют включению источника 5 тока в один из выходов 11 и 12 запоминающего устройства в соответствии с состоянием выбранного элемента памяти.

В режиме записи информации выборка элемента памяти осуществляется так же, как в режиме считывания, но, в соответствии с информацией, поступающей на входы 9 и 10, устройства у одного из дешифраторов 3, 4 выборки столбцов, на всех выходах установлен низкий логический уровень. В результате в выбранном элементе памяти один из транзисторов

17, 18 оказывается закрытым, что приводит к переключению элемента памяти в требуемое состояние.

1203592