Устройство для защиты памяти

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„Я0„„1203601

15И 4 б 11 С 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ CvCP

00 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ д/

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (54) (57) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ

ПАМЯТИ, содержащее регистр адреса, первый и второй дешифраторы, регистр кода защиты, блок управления, первый блок элементов И, элемент ИЛИ, причем один вход блока управления является первым входом устройства, другие входы блока управления подключены к выходам регистра кода защиты, входы которого соединены с выходами (2!) 3766236/24-24 (22) 02.07.84 (46) 07.01.86. Бюл. № 1 (72) Т. М. Семавина и Г. А. Семавин (53) 681.327.66 (088.8) (56) Авторское свидетельство СССР № 552641, кл. G ll С 29/00, 1978.

Авторское свидетельство СССР № 747342, кл. G 1 1 С 29/00, 1980.

Авторское свидетельство СССР № 1003673, кл. G 11 С 29/00, 1983. первого дешифратора, выходы блока управления подключены к одним входам первого блока элементов И, другие входы которого соединены с выходами второго дешифратора, вход которого подключен к одному входу регистра адреса и является вторым входом устройства, выходы второго блока элементов

И соединены с входами элемента ИЛИ, выход которого подключен к другому входу регистра адреса, выход которого является выходом устройства, отличающееся тем, что, с целью повышения его надежности, оно содержит второй блок элементов И, дополнительный регистр, вход которого подключен к одному входу блока управления, выходы дополнительного регистра соединены с одними входами второго блока элементов И, выходы которого подключены к входам первого Е дешифратора, другие входы второго блока у элементов И являются третьим входом уст- фф J ройства.

1203601

Устройство относится к вычислительной технике и может быть использовано для за1циты памяти.

Целью изобретения является повышение надежности защиты информации.

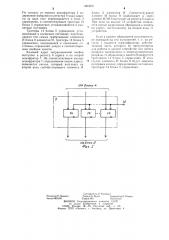

На фиг. 1 дана схема устройства; на фи1. 2 — схема блока управления.

Устройство содержит дополнительный регистр 1, второй блок 2 элементов И, первый дешифратор 3, регистр 4 кода защиты, блок 5 управления, регистр 6 адреса, второй дешифратор 7, первый блок 8 элементов И, элемент ИЛИ 9, первый вход 10 устройства, второй вход !! устройства, третий вход 12 устройства, выход 13 устройства, триггеры 14.

Регистр 1 предназначен для приема идентификатора, подаюгцегося на первый вход 10 устройства. Разрядность регистра 1 равна

К разрядов. При этом часть разрядов регистра 1 предназначена для записи действительного идентификатора, а часть — для записи мнимого идентификатора. Мнимая часть разрядов идентификатора может быть совершенно произвольной, а действительная часть строго определенной. Те разряды регистра 1, в которые записывается действительная часть идентификатора, знает только пользователь, которому разрешено оорагцаться к памяти.

Структура регистра 1 может быть следугошеи:

1 2 3 ... К вЂ” К

При этом, например, разряды 3, 5, К- 1 предназначены для записи действительного идентификатора, а остальные — для записи мнимого идентификатора.

Блок 2 элементов И предназначен для выдачи действительной частг идентификатора на первый дешифратор 3. Блок 2 элементов И состоит из К элементов И. На первые входы каждого элемента И подаются одноименные разряды идентификатора из регистра 1. На вторые входы каждого элемента И подаются разрешающие или запрегцаюгцие сигналы от центрального устройства управления (третьи входы 12 устройства), Разрешающие сигналы подаются только на вторые входы тех элементов И, номера которых соответствуют номерам тех разрядов регистра приема идентификатора, в которые была записана действительная часть идентификатора. В данном случае это элементы И с номерами 3, 5, К -1. Запре1цак1шие сигналы подаются на вторые входы всех остальных элементов И. Таким образом, на выходе блока 2 элементов И будет присутствовать действительный идентификатор.

Регистр 4 кода защиты предназначен для хранения кодов допуска к ячейкам памяти, причем каждый регистр содержит код, определяющий допуск для определенного пользователя.

Блок 5 управления предназначен для выдачи единичных сигналов на соответствуюшие входы элементов И блока 8 эле5

?0

55 ментов И. Блок 5 управления представляет собой блок триггеров 14. Единичные входы триггеров 14 подключены к выходам регистра 4 кода защиты, а нулевые входы— к первому входу 10 устройства, единичные выходы триггеров 14 соединены с первыми входами элементов И блока 8 элементов И.

Регистр 6 адреса предназначен для приема кода адреса, по которому пришел запрос на обращение, а также для выдачи сигнала разре1иения или запрещения на обращение к памяти в центральное устройство управления.

На первый вход !0 устройства подается идентификатор пользователя.

На второй вход 11 устройства подается код адреса, »о которому запрашивается обрашение к памяти.

На третьи входы 12 устройства подаются из центрального устройства управления разрешающие сигналы, которые подаются только на те элементы И блока 2, номера которых соответствуют номерам разрядов регистра 1, в которые бь|ла записана действительная часть идентификатора. На остальные элементы И блока 2 по третьим входам 12 устройства подаются запрегцаюгцие сигналы.

Устройство работает следующим образом.

На первый вход 10 устройства подается идентификатор пользователя, определявший об.ьем памяти, к которому разрешено обра;пение данному пользователю. Идентификатор пользователя, состоящий из К разрядов. имеет действительную часть и мнимую. Для получения разрешения на доступ к памяти необходимо правильно указать только действительную часть идентификатора, разместив ее в строго определенных разрядах.

В остальных разрядах идентификатора указывается мнимая его часть. которая может быть совершенно произвольной. Идентификатор (действительная и мнимая его части) записывается в регистр 1, информация с которого подается на первые входы блока 2 элементов И (количество элементов И в блоке 2 равно К) ° На вторые входы блока 2 элементов И из центрального устройства управления (не показан) подаются разрешаюгцие и запрещающие сигналы. Разрешаюшие сигналы подаются только на те элементы И, номера которых соответствуют

:1омерам тех разрядов регистра 1, в которые была записана действительная часть идентификатора. На остальные элементы И блока 2 из центрального устройства управления подаются запрещающие сигналы. Таким образом, на выходе блока 2 элементов И будет присутствовать только действительная часть идентификатора.

Идентификатор (его действительная часть), пройдя через первый дешифратор 3, выбирает из регистра 4 кода защиты тот регистр, который соответствует данному идентификатору. По этому же идентификатору происходит установка всех триггеров блока 5 управления в нулевое состояние.

120360!

0m dnwu 4

her dna< g

Фиг. 2

Составитель О. Кулаков

Редактор P. Цицика Техред И. Верес Корректор Е. Рошко

Заказ 8425/56 Тираж 583 Г!одписное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5 филиал ППП «Патент», г. У жгород, ул. Проектная, 4 з

По сигналу от первого дешифратора 3 содержимое выбранного регистра 4 кода защиты за один такт переписывается в блок 5 управления, и соответствующие триггеры 14 блока 5 управления устанавливаются в единичные состояния.

Триггеры 14 блока 5 управления, установленные в единичное состояние, подготавливают тем самым срабатывание элементов

И блока 8 элементов И. Триггеры 14 блока 5 управления, находящиеся в единичном состоянии, определяют допуск к соответствующим ячейкам памяти.

Кодовый адрес запрашиваемой ячейки поступает в регистр 6 адреса и на второй дешифратор 7. На соответствующем выходе дешифратора 7, определяемом кодом адреса, появляется сигнал, который поступает на второй вход соответствующего элемента И блока 2 элементов И. Соответствующий элемент И блока 8 срабатывает и через элемент ИЛИ 9 поступает на регистр 6 адреса.

При этом на выходе 13 устройства появляется сигнал разрешения обращения к памяти по адресу, поступившему на второй вход l! устройства.

Если к памяти обращается пользователь, не имеющий на это полномочий, т. с. на pe1ð гистр 1 подается идентификатор, действительная часть которого не предусмотрена для работы в данном устройстве или запись которого произведена в непредусмотренные разряды, то обращение к памяти блокируется триггерами 14 блока 5 управления. В этом

15 случае элементы И блока 8 будут закрыты по первым входам. определяемым состоянием триггеров 14 блока 5 управления.