Запоминающее устройство

Иллюстрации

Показать всеРеферат

Яф, СОНОЗ СОВЕТСНИХ ," = QA gi < СОЦИАЛИСТИЧЕСНИХ 4Т: —.=-.-=, РЕСПУБЛИН д . "

„,„Я0„„1203602 (51)4 (д 1! С 29 00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ г

3!(. p (,,-„

ОПИСАНИЕ ИЗОБРЕТЕНИЯ !<1., :- ::

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ц

/ (21) 3774353/24-24 (22) 26.07.84 (46) 07.01.86. Бюл. № 1 (72) Л. О. Беспалов и А. Г. Головачев (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР № 1049982, кл. G 1! С 29/00, 1982. (54) (57) ЗАПОМИНАЮШЕЕ УСТРОЙСТВО, содержащее первый и второй блоки памяти, первый и второй блоки контроля, элемент задержки. первый блок сравнения, первый, второй и iðåòèé элементы И, блок элементов ИЛИ, первый и второй блоки элементов И, причем первые и вторые входы блоков памяти являются входами устройства, вторые входы бл оков памяти подкл к)<1 ен ы к входу элемента задержки, выход которого соединен с первыми входами блоков контроля, первый выход первого блока памяти подключен к второму входу первого блока контроля, первому входу первого блока с равнения и первому входу первого блока элементов

И, второй выход первого блока памяти 00еди неll с гpp гьим Входом 11(.р ВОI () (). Iока I(OIlтроля и Вторым входом первого блока элементов И, первый Вход первого элемента И соединен с входом элемента задержки, выходы первого и второго олоков контроля подключены соответственно к первым входам второго и третьего элемсHTOB И, BhlxoJ Bi oрого элемента И соединен с третьим входом первого блока элементов И, первый Выход второго блока памяти подключен к второму входу второго блока контроля, второму вход; первого блока сравнения и первому входу второго блока элементов И, второй выход второго блока памяти соединен с третьим входом второго блока контроля и вторым входом BTopol0 блока элементов И, выходы первого и второго блоков элементов И подключены к первому и второму входам блока элементов ИЛ И, Выход которого является выходом устройства, отличающееся тем, что. с целью.повышения надежности устройства, оНо содержит третий блок памяти, третий блок контроля, второй и третий блоки сравнения, первый, второй и третий элементы

ИЛИ, третий блок элементов И. ч(твертый пять<и и шестой элементы И, при . :: В«).-<ый вход третьеl о блока контроля г(>свдп)ге< выхо.IOxl элемента задеря;ки. 11(, рвый и второй входы третьего блока памяти подключены соответственно к первым и в1орым входам перво(о и второго блоков памяти, первый

Вых(,д третьего блока памяти соединен с

BT0p I! )! Входом трсTB(l 0 б.lOI(B КОНТрОл я.

Вгорыми Bx0;(BOIH Второго и третьего блоков сравнения и IIBpBB!xt в;Одом третьего блока элементов И, второй ВхОд которого подклк>«еН к третьему входу третьего блока контроля и к второму Выходу третьего блока памяти, вь ход третьего блока э lcx!e!IT0B 14 coez«H(H уу с третьим входом блока элементов ИЛИ, %ФУ первые входы второго и третьего блоков С сравнения подключены соответственно к первым выходам первого и второго .;)ков памяти, первые выходы Олоков сравнс ния подключены к Входам четвертого элемента 11, ва

Вы Од которого «оединен «вторыми входами второго. третьего и шестого элементов И, вторые выходы первого и третьего блоков сравнения подк.)ючсны к входам перво(о СА> элсх)ента ИЛИ, Выход которого со«динеl! 1„1,1

«Вторых) Bxo, 0.; и. рвого э.)смента И. вы 0:It>l ( первого и треть(го элементов И подключены к Входам второго элем(нта ИЛИ, выход которого соединен с третьим входом ьторого ().:Ока .)см сHTOB И. Первый Вх0,1 1срн(н о ..1«мсн I а И соед) нсн с первым Вх0,;Ох! пят(и 0 i,1("1<. HТа И, BTOpO)! Вх().1 КOTÎ))OI 0 подк,ll()

К ВТ<;РОМ, ВЫ ХО.! i ВТОРО () О, I 0KB «PB BH(. Н ИЯ, ф ф

Выход третьего блока контроля «Осдинсп с первым входîM шестого.элемента И, Выходы пятого и шесто(х> элсх)снтоп И сос,!,нl!<. I!ы

«ВXO;!Bi! I! третьего s«l«XI«H I а И, 111, Вь.. 0 I

КО< )IH):!) 1<) !К,1 ЮЧ(Н К )t Ь(Х1 Х Е)ХО.(Х 1 ()(< l сl < () IOI;; элех1«1:.1ЧВ 11.

1203602

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе специализированных цифровых вычислительных машин (СЦВМ) иили систем обработки и передачи цифровых данных.

Цель изобретения ности устройства.

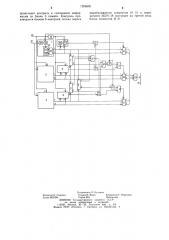

На чертеже представлена блок-схема уст рой ств а.

Устройство содержит первый 1, второй 2 и третий 3 блоки памяти, первый 4, второй 5 и третий 6.блоки контроля, первый 7, второй 8 и третий 9 блоки сравнения, первый 10„ второй 1!, третий 12, четвертый 13, пятый 14 и шестой 15 элементы И, первый 16, второй 17 и третий 18 элементы ИЛИ, первый 19, второй 20 и третий 21 блоки элементов И, элемент 22 задержки, блок 23 элементов

ИЛИ, регистр 24 адреса, дешифратор 25 кода адреса, накопитель 26, информационное поле 27 накопителя, поле 28 контрольных разрядов накопителя, выходной регистр 29, блок 30 свертки по модулю 2, блок 31 сравнения, адресный вход 32, вход 33 опроса и выходную шину 34, Запоминающее устройство работает следующим образом.

На вход 32 устройства подается код адреса, а на вход 33 — сигнал опроса. В каждом блоке — 3 памяти код адреса подается на вход регистра 24, и сигнал опроса на второй вход дешифратора 25, управляющего регистром 24. При наличии сигнала опроса на входе дешифратора 25 на одном из его выходов появляется сигнал, при помощи которого выбирается информация из соответствующей ячейки накопителя 26.

С выхода информационного поля 27 и поля 28 контрольных разрядов накопителя 26 считанная информация поступает на вход регистра 29. С выхода регистра 29 информация поступает на выходы блоков 1 — 3 памяти.

Информационная ее часть с первого выхода блока 1 памяти подается на первые входы блоков 7 и 8 сравнения, с первого блока 2 памяти подается на второй вход блока 7 и на первый вход блока 9, с первого выхода блока 3 памяти подается на вторые входы блоков 8 и 9. В блоках 7- — 9 сравнения происходит поразрядное сравнение информации, считанной из блоков памяти. В случае равенства информации, считанной из блоков 1 и 2 памяти, на втором выходе блока 7 формируется сигнал «Равно», который через элемент ИЛИ 16 поступает на второй вход элемента И 10. При наличии на первом входе элемента И 10 сигнала опроса, он формирует сигнал, поступающий через элемент ИЛИ 17 на третий вход блока элементов И 20, тем самым разрешающий считывание информации и ее контрольных признаков из блока 2 памяти через блок 23 на выходную шину 34. Аналогично происхо1 !

О !

3s

<и г

55 дит сравнение блоком 9 информации, считываемой из блоков 2 и 3 памяти и, в случае равенства, передача информации и ее контрольных признаков на выходную шину 34.

Также выполняется блоком 8 сравнение информации, считываемой из блоков 1 и 3 памяти. При ее равенстве на втором выходе блока 8 формируется сигнал «Равно», который подается на второй вход элемента

И !4. При наличии на первом входе элемента

И 14 сигнала опроса, он формирует сигнал разрешения считывания информации, который через элемент ИЛИ 18 поступает на третий вход блока 21 и, тем самым, разрешает считывание информации и ее контрольных признаков из блока 3 через блок 23 на выходную шину 34. В случае неравенства информации, считываемой из блоков 1 и 2, 1 и 3, 2 и 3 памяти, на первом выходе каждого из блоков 7, 8 и 9 сравнения формируется сигнал «не равно», который поступает на первый, третий и второй входы элемента И 13 соответственно.

При наличии на всех входах одновременно элемента И !3 сигналов «Не равно» элемент

И 13 выработает разрешающий сигнал для элементов И 11, 12 и 15. Информация с выходов блоков — 3 памяти поступает соответственно на входы блоков 4 — 6 контроля, где ее информационная часть свертывается при помощи блока 30 по заложенным контрольным признакам. Результаты свертки сравниваются в каждом блоке 4, 5 и 6 с контрольными признаками блоков 3! сравнения.

Сигнал опроса подается на первые входы блоков 4 — 6 контроля с выхода элемента 22 задержки (для синхронизации работы устройства) . В случае равенства результата свертки информационной части и контрольного и ризнака (признаков) в блоке 4, а также наличия сигнала опроса на входе этого блока, блок 31 блока 4 формирует сигнал, который поступает на первый вход элемента И 11.

При наличии на втором входе элемента И 11 сигнала разрешения на его выходе появляется сигнал, поступающий на третий вход блока элементов И 19 и, тем самым, разрешающий передачу информации и ее контрольных признаков, поступающих на вход блока элементов И 19 дальше — через блок элементов ИЛИ 23 на выходную шину 34 устройства. В случае неравенства результатов свертки информационной части и контрольного признака (признаков) в блоке 4, этот блок не вырабатывает сигнал опроса.

В работу включатся пепи, обеспечивающие считывание информации из блока 2 памяти через блок элементов И 20 и блок элементов

ИЛИ 23 на выходную шину 34 устройства.

Контроль информации в этом случае осуществляется блоком 5 контроля, работа которого аналогична работе блока 4 контроля.

Сигнал опроса формируется элементом И 12 и через элемент ИЛИ 17 поступает на третий вход блока элементов И 20. Аналогично

1203602

Составитель О. Кулаков

Реда кто р О. Г оло в ач Техред И. Верес Корректор Г Решетник

Заказ 8425/56 Тираж 583 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 происходит контроль и считывание информации из блока 3 памяти. Контроль производится блоком 6 контроля, сигнал опроса вырабатывается элементом И 15 и через элемент ИЛИ !8 поступает на третий вход блока элементов И 21.