Преобразователь кода числа из системы остаточных классов в позиционный код

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ .РЕСПУБЛИК (19) (11) А (51)4 Н 03 Н 7 00

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3771704/24-24 (22) 12.07.84 (46) 07.01.86. Бюл. Ф 1 (72) В.А.Иванченко и П.Л.Прокопьев (53) 68 1.3(088.8) (56) Авторское свидетельство СССР

Ф 1005028, кл. G 06 F 5/02, 1981.

Авторское свидетельство СССР

У 554536, кл. G 06 F 5/02, 1974. (54)(57) ПРЕОБРАЗОВАТЕЛЬ КОДА ЧИСЛА

ИЗ СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В

ПОЗИЦИОННЫЙ КОД, содержащий блок модульных вычитателей, позиционный накапливающий сумматор, блок дешифраторов нуля и блок управления, включающий два триггера, элемент задержки, первый элемент И, коммутатор, первую группу элементов И, причем вход пуска преобразователя соединен с единичным входом первого триггера блока управления, первый вход первого элемента И которого соединен с тактовым входом позиционного накапливающего сумматора, с тактовым входом блока модульных вычитателей и с тактовым входом преобразователя, выход блока модульных вычитателей соединен с входом блока дешифраторов нуля, вход остатка по старшему модулю и входы остатков по остальным модулям преобразователя соединены соответственно с первым информационным входом коммутатора блока управления и входом уменьшаемого блока модульных вычитателей, выходы элементов И первой группы блока управления соединены с входом вычитаемого блока модульных вычитателей и с информационным входом позиционного накапливающего сумматора, выход которого является выходом преобразователя, а также в блоке управления выход первого триггера соединен с вторым входом первого элемента И, выход которого соединен с первыми входами элементов И первой группы, и через элемент задержки с единичным вхо.",ом второго триггера, выход которого соединен с управляющим входом коммутатора, выход которого соединен с вторыми входами элементов И первой группы, нулевой вход первого триггера соединен с нулевым входом второго триггера, отличающийся тем, что, с целью повышения быстродействия, он содержит блок хранения констант, а блок управления содержит вторую группу элементов И и второй элемент

И, причем выход блока дешифратара .нуля соединен с первыми входами элементов И второй группы блока управления, выходы которых соединены ,с адресным входом блока хранения констант, выход которого соединен с вторым информационным входом коммутатора блока управления, а также в блоке управления выход второго триггера соединен с вторым входом последнего элемента И второй группы, выход каждого элемента И второй группы соединен с вторым входом следующего элемента И второй группы, выходы элементов И второй группы соединены с соответствующими входами второго элемента И, выход которого соединен с нулевым входом второго триггера.

12036

2О

50

Изобретение относится к вычислительной технике и может быть использовано для преобразования кодов чисел, представленных в системе остаточных классов (СОК), в позиционный код.

Целью изобретения является повышение быстродействия.

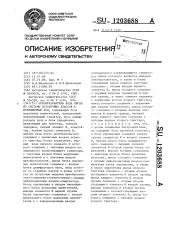

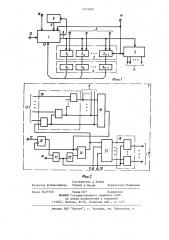

Иа фиг. 1 представлена схема преобразователя кода числа из СОК IG в позиционный код, на фиг. 2 — схема блока управления.

Преобразователь кода числа из

С0К в позиционный код содержит блок

1 управления, блок 2 модульных вь 15 читателей, позиционный накапливающий сумматор 3, блок 4 дешифратора нуля, блок 5 хранения констант, выход 6 преобразователя, выходы 7 и 8 блока 1 управления, вход 9 остатков по 1 †(п — 1) модулям преобразователя, вход 10 по старшему о модулю преобразователя, вход 1 1 блока 1 управления, вход 12 пуска преобразователя, вход 13 блока уп- 25 равления, тактовый вход 14 преобразователя (n — число модулей СОК).

Блок 1 управления содержит триггеры 1> и 16, элементы И 17 и 18, группы 19 и 20 элементов И, коммутатор 21 и элемент 22 задержки.

Преобразователь кода числа из

СОК в позиционный код работает следующим образом.

Код преобразуемого числа, представленный остатками по модулям

Pt-P„, поступает через группу входов 9 на соответствующие модульные вычитатели блока 2, остаток по модулю P < через вход 10 — на вход блока 1 управления.

По сигналу "Пуск", поступающему на управляющий вход 12, преобразователь начинает работу. В первом такте с выхода 7 блока 1 управления остаток „ поступает на вторую группу входов блока 2, где вычитается

«t и по соответствующим модулям из кода преобразуемого числа. Одновременно

Ж„ передается на сумматор 3. В последующих тактах из содержимого вычитателей блока 2 вычитается константа Р, поступающая из блока 5 хранения констант через вход 11 на блок 1 управления и далее через выход 7. на блок 2. Одновременно в

55 каждом такте Р„ поступает на позици88 2 онный сумматор 3, где суммируется с содержимым сумматора. При обнулении вычитателя по модулю Р>, блока 2 соответствующий дешифратор нуля блока 4 вырабатывает сигнал, поступающий через вход 13 на блок управления. Блок 1 управления формирует адрес константы P ° Р, которая через вхоц 11 в каждом последующем такте поступает на блок 1 управления и далее через выход 7 на блок 2 и псзиционный сумматор 3.

При обнулении вычитателя по модулю

P блока 2 блок 1 управления формирует адрес константы Р> Р „ „ Р„

Аналогично. преобразователь работает и в последующих тактах. При обнулении всех вычитателей блока 2 преобразователь прекращает работу.

Преобразованное число находится на выходе 6.

Блок 1 управления работает следующим образом.

В исходном состоянии все триггеры блока 1 управления сброшены в нулевое состояние. По сигналу

"Пуск", поступающему на вход 12 устанавливается в единичное состояние триггер 15, открывающий элемент И 17 для прохождения тактовых импульсов. По первому тактовому импульсу остаток сС< поступающий через вход 10 на коммутатор 21, передается через элементы И группы

19 на выход 7 блока 1 управления.

В конце первого такта задержанным на элементе 22 задержки импульсом устанавливается в единичное состояние триггер 16 в результате чего во втором такте константа с блока 5 хранения констант через. вход,1« коммутатор ?1 и элементы И группы 19 поступает на выход 7. Единичный уровень с выхода триггера 16 открывает последний элемент И группы 20. При обнулении вычитателя по модулю Р блока 2 с дешифратора нуля блока 4 поступает сигнал, открывающий соответствующий элемент И группы 20. На выходе 8 формируется адрес, поступающчй на блок 5 хранения констант.

При обнулении всех вычитателей блока

2 открывается элемент И 18, в результате чего сбрасывается в нулевое состояние триггеры 15 и 16. прекращая работу преобразователя, 1203688 иг.

Заказ 8429/60

Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель А.Клюев

Редактор И.Николайчук Техред З.Палий Корректор Г.Решетник