Дельта-модулятор

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3716651/24-24 (22) 21.03.84 (46) 07.01,86. Ьюл. № 1 (71) Рижский ордена Трудового Красного Знамени политехнический институт им. А.Я . Пельше (72) К,С. Комаров и Г,Н. Котович (53) 621.376.9(088.8) (56) Дельта-модуляция. Теория и применение./Под,ред, M.Ä. Венедиктова, M. Связь, 1976, с. 189, рис. 7.9.

Авторское свидетельство СССР

¹ 1121777, кл. Н 03 К 13/22,19.07.83. (54)(57) ДЕЛЪТА-МОДУЛЯТОР, содержащий компаратор, первый вход которого через входной фильтр соединен с входом модулятора, а выход подключен к входу триггера, выход которого соединен с выходом модулятора и подключен к информационному входу регистра, сдвига, прямые и инверсные выходы разрядов которого соединены с соответствующими входами элемента,эквивалентности, к выходу которого подключены соединенные последовательно фильтр, первый амплитудно-импульсный модулятор, первый преобразователь полярности и первый интегратор, прямые и инверсные выходы двух первух разрядов регистра сдвига соединены с соответствующими входами блока шумокомпенсации, выход которого подключен к другому входу первого преобразователя полярности, входы синхронизации триггера и регистра сдвига объединены и подключены к

„„SU,, 1203707 А (5g 4 Н 03 M 3/02 шине синхронизации, о т л и ч а ю— шийся тем, что, с целью улучшения распознаваемости преобразуемых сигналов, в него введены соединенные последовательно второй амплитудно-импульсный модулятор, второй преобразователь полярности и второй интегратор, соединенные последовательно третий амплитудно-импульсный модулятор, третий преобразователь полярности и третий интегратор, сумматор и четыре элемента И, входы первого и второго элементов И подключены соответственно к прямым и инверсным выходам двух первых разрядов регистра сдвига, а выходы — к управляю- Е щим входам второго амплитудно-импульс- уу ного модулятора, входы третьего и четвертого элементов И подключены. С соответственно к прямым и инверсным

\ выходам трех первых разрядов регистра сдвига, а выходы — к управляющим входам третьего амплитудно-.импульсного модулятора, вход которого объединен с входом второго амплитудноимпульсного модулятора и подключен к выходу фильтра, выход блока шумокомпенсации соединен с другими вхо- CO дами второго и третьего преобразователей полярности, выходы всех интеграторов подключены к входам сумматора, выход которого соединен с вторым входом компаратора, управляющие входы первого амплитудно-импульс- ф ного модулятора подключены к прямому и инверсному выходам первого разряда регистра сдвига.

1203 707

Изобретение относится к вычислительной технике и электросвязи и может быть использовано, например, для качественного преобразования речевых сигналов в цифровую Форму

Цель изобретения — улучшение рас познаваемости преобразуемых сигна-( лов.

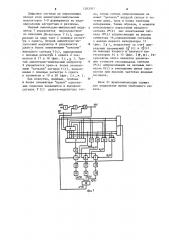

На фиг. 1 приведена функциональная схема дельта-модулятора; на 10 фиг. 2 — временные диаграммы, пбяс— няющие его работу.

Дельта-модулятор содержит входной фильтр 1 через который вход устройства подключен к первому входу компаратора 2, выход которого подключен к первому входу триггера 3. Выход триггера 3 соединен с информационным входом регистра 4 сдвига и одновременно является выходом устройства. Прямые и инверсные выходы регистра 4 сдвига,.подключены к элементу 5 эквивалентности, выход которого через фильтр 6 подключен одновременно к управляющим входам первого,второго и третьего амплитудноимпульсных модуляторов 7-9. Выходы амплитудно-импульсных модуляторов

7-9 подключены через первые входы соответственно первого, второго и третьего преобразователей 10-12 полярности к входам соответственно первого, второго.и третьего интеграторов 13-15. Выходы первого, второго и третьего интеграторов 13-15 заведены на входы сумматора 16, вы35 ход которого подключен к второму входу компаратора 2.

Входы первого-и второго элементов И 17 и 18 подключены соответственно к прямым и инверсным выходам двух первых разрядов регистра 4 сдвига, а выходы элементов И 17 и 18 соединены с управляющими входами второго амплитудно-импульсного моду- 4> лятора 8. Входы третьего и четвертого элементов И 19 и 20 подключены соответственно к прямым и инверсным выходам трех первых разрядов регистра 4 сдвига, а выходы элементов И 19 и 20 соединены с управляющими входами третьего амплитудно-импульсного модулятора 9. Входы блока 21 шумокомпено сации подключены к входам элементов

И 17 и 18, а его выход соединен с Ы вторыми входами первого, второго и третьего преобразователей 10-12 по1пярности.

Кроме того, управляющие входы первого амплитудно-импульсного модулятора 7 подключены к прямому и инверсному выходам первого разряда регистра 4 сдвига, синхронизирующий вход которого объединен с синхронизирующим входом триггера 3 и подключен к шине 22 синхронизации, В блок 21 шумокомпенсации входят, например, четыре элемента И, два регистра сдвига, два элемента НЕ и соединенные последовательно преобразователь полярности, интегратор и усилитель, выходом подключенный к выходу. блока 21, входы которого ягляются входами двух элементов И, выходы которых соединены .с входами соответствующих регистров сдвига, выходы которых через два других элемента И подключены к входам преобразователя полярности, причем вход каждого регистра сдвига объединен с входом элемента НЕ, выход которого соединен с другим входом другого элемента И. Однако выполнение блока шумокомпенсации может быть и другим.

Дельта-модулятор работает следующим образом.

Входной сигнал U(c) (фиг. 2с1), ограниченный по полосе входным фильтром 1, поступает на первый вход компаратора 2, на второй вход которого заведен сигнал аппроксимации U*(t) (фиг. 2 а ), формируемый цепью обратной связи кодера. Результаты сравнения в виде единичных или нулевых информационных битов с приходом очередных тактовых импульсов (фиг.2 р ) записываются в триггер 3 (фиг. 2Ь ) и регистр 4 сдвига.

Элемент 5 эквивалентности и фильтр

6 в результате анализа записанной в регистр части выходной последовательности Y (t) (фиг. 2 Б ) дельта-модулятора формируют медленно меняющийся слоговый уровень V, пропорциональный амплитуде и частоте входного сигнала U(t). Уровень V поступает на управляющие входы первого, вторагс, и третьего амплитудно-импульсных модуляторов 7-9, в результате чего шаг квантования сигналов, восстанавливаемых на первом, втором и третьем интеграторах 13-15, является функци:— ей амплитуды и частоты входного сигнала, т.е, осуществляется слоговая адаптация шага квантования к параметрам входного сигнала, 1203707

Фиа. !

Цифровые сигналы на управляющих входах всех амплитудно-импульсных .модуляторов 7-9 формируются по индивидуальным алгоритмам и различны, Первый амплитудно-импульсный модулятор 7 управляется непосредствен4 но выходным ДМ-потоком Y (t), задер( жанным на один такт с помощью регистра 4 сдвига. Второй амплитудно-им,пульсный модулятор 8 управляется двух-и более элементными "пачками"

; выходного сигнала У(С), выделяемыми с помощью регистра 4 сдвига и элементов И 17 и 18 (фиг. 2 2., ) ). Третий амплитудно-импульсный модулятор

9 управляется трех- и более элементными "пачками сигнала ((t ), выделяемыми с помощью регистра 4 сдвига и элементов и 19 и 20 (фиг. 2 e,х. ).

Как известно, двойные, тройные и более элементные "пачки" однотипных символов появляются в выходном сигнале V (t) дельта-модулятора тогt да, когда сигнал аппроксимации не может догнать" входной сигнал в течение двух, трех и более тактовых интервалов. Таким образом, в моменты интенсивного нарастания входного сигнала 0*() шаг квантования сигнала V*(t) аппроксимации на выходе сумматора 16,определяемый сигналом с выхода первого интегратора l3

10 (фиг. 2 З ), возрастает за счет прн ращений напряжений 0 () и U (С) на выходах второго и третьего интеграторов 14 и 15 (фиг. 2 8, ;). Результатом этого является увеличе15 ние точности отслеживания сигнала

У*() аппроксимации за входным сигналом u(t) и уменьшение шумов перегрузки при высоких частотах входных сигналов.

Блок 21 шумокомпенсации служит для подавления шумов свободного канала.

1203707 и () й(О

У(Ю)

8 иД) Составитель О.Ревинский

Редактор О.Юрковецкая Техред Ж.Кастелевич

Корректор С. Шекмар

Филиал ППП "Патент", г. Ужгород, ул.Проектная,4

Заказ 8430/61 Тираж 871 Подпис ное

ВНИИПИ Государственного комитета СССР. по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5