Устройство для контроля напряжения источников питания коммутационных аппаратов

Иллюстрации

Показать всеРеферат

СООЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (191 (11) (51) 4 С О1 R 19/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3519922/24-21 (22) 08.12.82 (46) 30.О9.86. Бюл. № 36 (71) Научно-исследовательский и проектно-конструкторский институт по проблемам развития Канско-Ачинского угольного бассейна (72) В.П. Горбиль,А.Л. Демко и В.А. Степанов (53) 621.317.757(088.8) (56) Авторское свидетельство СССР №.349949, кл. G R 19/00, С 01 R 19/04, 1970.

Авторское свидетельство СССР

¹ 834546, кл. С 01 R 19/04, 1979. (54)(57) 1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

НАПРЯЖЕНИЯ ИСТОЧНИКОВ ПИТАНИЯ

КОММУТАЦИОННЫХ АППАРАТОВ, содержащее формирователь периода интегрирования, интегратор и индикатор, о т л и ч а ю щ е е с я тем, что, с целью повышения помехозащищенности и точности определения минимального уровня среднего значения пульсирующего напряжения источника питания при толчканых нагрузках, в него введены преобразователь напряжения в частоту, блок следящего преобразования частоты сети, преобразователь частоты в код, блок умножения, элемент задержки и процессор, при этом вход преобразователя напряжения в частоту является первым входам устройства, а выход преобразователя напряжения в частоту подсоединен к первому входу блока умножения, второй вход которого соединен с выходам преобразователя частоты в код, вход которого соединен с входом формирователя периода интегрирования и выходом блока следящего преобразования частоты сети, вход которого является вторым входом устройства, выход формирователя периода интегрирования соединен с управляющим входом процессора и входом элемента задержки, выход которого подключен к первому входу интегратора, выход блока умножения соединен с вторым входом интегратора, выход которого подключен к информационному входу процессора, а к выходу процессора присоединен индикатор.

2. Устройство по и 1, о т л и ч а ю щ е е с я тем, что процессор включает в себя блок сравнения кодов, ключ и регистр, причем первые входы блока сравнения кодов и регистра соединены между собой и образуют информационный вход процессора, выхоц регистра соединен с вторым входом блока сравнения кодов и является выходом процессора, выход блока сравнения кодов соединен с вторым входом регистра через ключ, управляющий вход которого является управляющим входом процессора.

1204035

Изобретение относится к измерительной технике и предназначено для использования при контроле. источников питания коммутационных аппаратов при толчковых режимах работы.

Цель изобретения — повышение помехозащищенности и точности Определения минимального уровня среднего значения пульсирующего напряжения источника питания при толчковых нагрузках.

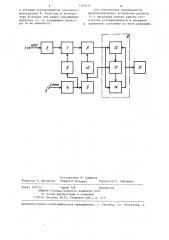

Функциональная схема устройства представлена на чертеже.

На вход 1 поступает контролируемое напряжение. Преобразователь 2 напряжения в частоту преобразует контролируемое напряжение в частоту импульсов. Питающая сеть подключе-" на на вход 3. Блок 4 следящего преобразования частоты сети осуществляет преобразование в следящем режиме частоты питающей сети в частоту управляемого генератора по прин— ципу фазовой автоподс ройки частоты. Выход блока 4 соединен с Входом преобразователя 5 частоты в код и входом формирователя 6 периоца интегрирования, формирующего на своем выходе короткие импульсы с периодом, равным длительности текущего периоды питающей сети. Выход преобразователя

5 соединен с первым входом блока 7 умножения, второй вход которого соединен с выходом преобразователя 2 напряжения в частоту. Выход блока 7 соединен с информационным входом интегратора 8, выход которого соединен с первым входом процессора 9, Выход формирователя 6 соединен с вторым входом процессора 9 и Входом элемента задержки 10, зацержкгающе -o сигнал сброса интегратора 8 В нулевое состояние на время, не!збхсдкмсе для работы процессора 9, выход которого соединен с индикатором 11, регистрирующим минимальное среднее значение контролируемого напряжения.

Кроме того, процессор 9 состоит из блока 12 сравнения ксцов, выхоц которого соединен через ключ ;3 с управляющим входом регистра 14.

Первый вход блока 12 сравнения кодов и информационный вход регист:ра 14 является первым..входом процессора 9, а управляющий вход;ключа 13 является вторым входом процессора 9. Выходом процессора 9 является точка соединения выхода регистря 14 H Вropoã" входа блока 12 сравнения кодов.

Устройство работает следующим

o6\pЯ3Ом.

KoHòðoJII,"póåмое напряжение с зяжкмОЕз электромагни еного привода коммутационного аппарата U(t) поцключено к Входу преобразсвят ля 2 напряжения

В частотi,. ня Выходе которого форми111 руется посл(здОВятельнсстb кмеЕульсОВ чя.стота которых прспсрцкональня мгновенному зняч" нию напэяжения U(t) .

Выходная частота с преобразователя 2 поступает F1B пер1зый вхоц блока умно15 жения 7. Одноезременнэ на второй вход блока умножения i по"ò-;óïàåò код, пропорциональный частоте IIHT яюшей сети. НЯ выхс,le био;«.а умножения 7„ который построен па принципу управляелс МОГО ДQJIHTP B JI . фОРНHPУ ется пОток им пульсов, частота котopllx пропорцкоHBJIhHB прсиэвеценЕлю Входных сиГналОВ, т.е., на выход=- блока 7 получается сигнал ГрспсрцкснальньЕй мгновенному значеЕеию ко:Етролируемогo напряжения и обратно Hpo — Орциональный периоду

r e l Hi .3тот сигнал и "ic упяет ня Hv. Гратср 8, представляющий соаой счет—

ЧИК ИМ -УЛЬСOB. В КО-1 О Зсм фОР!Ь;HPУPòсЯ код суммы импульсов 1 я перкоде кн-:егрирования, -.: е. Нсд, прспсрцио—

IЕЯЛЬНЫИ СРЕД11 ЕМ5! 3. .B × I И1С НЯПР!ЯЖЕ НИЯ °

Формирование ие1"; ервяля кнтегркро—

«с;

Вяния 0,, 1111ВНОГО по длительнос тк периоду сети,. производится путем сброся IT ну:Еевое ссстоне111е интеграторая 8 импульсами, и О ступающими -.е—

:,-!с Н«м!«н т- адерж-„!.- "; 0 с Вь1хсдя фср— B мк ODBòcJIÿ 6 парис!1В кн -егркрсвяния.

Тя=cHT. Об ря э ОH, -IP- Iвыхсде иеЕтег я— тора 8 в конце кя;;,дого периода сете=.O1О НЯПРЯЕКЕНИЯ:.TIOPk1НРP EÒCII КОД СРЕДCi!.

Н !Э Г З %1 Я -I C H H Я К О Н т Р О Л 1.1 Р У!-" М С Г С Н Я П Р Я женив U,t, . =тот код ПЕОст :: Яет В процессор 9 ня первь.й Вход блока 12

С

H õoã реГЕлстря памяти !, Одержимое

Я . регистра 1-1 и выходной код интегратора 3 cpçH11HBЯют я блоком 12 cpBВ кения кодов и в случае,. если Yoä, записанный В регистр 1 больше, чем код =; интегр=-. Оре 9 В момент .:рихода !

>. Импульса с Выхода преобразователя 6 .. =.рисда интегрирования HB ключ 13. на выходе ключа 13 образуется сиг(--:.ал разрешения записи r-. регистр 14„

1204035

Составитель В. Савинов

Редактор А. Юрчикова Текред И.Попович Корректор E. Сирохман Заказ 5267/2 Тираж 728 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4, в который переписывается содержимое интегратора 8. Если код в интеграторе 8 больше или равен содержимому регистра 14, то содержимое регистра 14 не изменится.

Для обеспечения правильности функционирования устройства регистр

14 в начальный момент работы устройства устанавливается в исходное единичное состояние по всем разрядам.