Устройство для измерения фазового сдвига

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (д) 4 G Oi R 25/00 25 08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ г ° б, ° :

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3768479/24-21 (22) 12. 06. 84 (46) 15. 01. 86. Бюл. У 2 (72) С.Е. Токовенко, В.И, Вдовиченко, П.П. Жабицкий, А.В, Выговский, Г,В. Талызин и С.П. Котляр (53) 621.317.77(088,8) (56) Авторское свидетельство СССР

У 601631, кл. G 01 R 25/00, 1977.

Авторское свидетельство СССР

У 930151, кл. G 01 R 25/00, 1981. (54) (57) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ

ИЗМЕНЕНИЯ ФАЗОВОГО СДВИГА, содержащее последовательно соединенные генератор опорных сигналов и управляемый делитель частоты, фазовый дискриминатор, первые входы которых соединены с шиной входных сигналов и вы1 ходом делителя частоты, а вторые входы через первый элемент И вЂ” с единичными выходами триггеров, второй и третий элементы И, первые и вторые входы которых соединены с выходами триггеров, четвертый и пятый элементы И, первые входы которых соединены с выходом генератора опорных сигналов, а выходы — с входами реверсивного счетчика, о т л и ч а ющ е е с я тем, что, с целью повышения точности измерения, в него введены счетчик циклов, формирователи импульсов, элементы И, ИЛИ и до„„SU„„1205055 A полнительный реверсивный счетчик, причем единичные выходы триггеров через первый элемент ИЛИ соединены с входом первого формирователя, первый выход которого подключен к третьим входам второго и третьего элементов И, а второй — к первым входам шестого и седьмого элементов

И, вторые входы которых соединены с выходом генератора опорных сигналов, а третьи и четвертые — с выходами триггеров фазового дискриминатора, выходы шестого и седьмого элементов И соединены с входами дополнительного реверсивного счетчика, вход начальной установки которого подключен к выходу второго элемента ИЛИ, первый вход которого соединен через счетчик циклов с выходом первого элемента И, а второй и третий входы второго элемента ИЛИ вЂ” с выходами переполнения дополнительноГо реверсивного счетчика, которые через второй и третий формирователи соединены с первыми входами третьего и четвертого элементов ИЛИ, вторые входы которых соединены с выходами второго и третьего элементов И„ выходы третьего и четвертого элементов ИЛИ соединены с входами управле ния коэффициентом деления управляемого делителя и входами четвертого и пятого элементов И.

7205055

Изобретение относится к радиоизмерительной технике и может быть использовано в устройствах измерения параметров фазомодулиронанных сигналов, в частности при измерении пере- !7 мещения с помощью фазовых датчиков.

Цель изобретения — повьш ение точности измерения.

В случае быстрого изменeíèÿ фазы, основным параметром системы являются ее динамические показатели, результат измерения формируется в каждом периоде следования. входных сигналон. При малых скоростях изменения фазы, формируется усредненное значение изменения фазы за несколько периодов входных сигналов. Для этого сигнал: фазового рассогласования между входными .и вспомогательными импульсами поделенной опорной частоты разделяет-" 20 ся на два сигнала, первый из которых соответствует малой скорости изменения фазы, а второй — большой скорости, при этом сигналы компенсации первого сигнала вырабатываются н виде .среднего за несколько периодов, а сигналы компенсации второго формируются в каждом периоде входных сигналов.

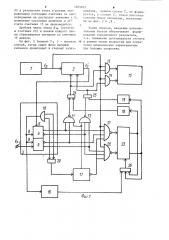

На фиг. 1 представлена функцио- 30 нальная схема предлагаемого устройства; на фиг. 2 — временные диаграммы его работы.

Устройство (фиг. 1) содержит генератор 1 опорных сигналов, соединенный с ним упранляемый делитель 2 частоты, фазовый дискриминатор 3, включающий триггеры 4 и 5, первые входы 6 и 7 которых подключены к выходу делителя 2 частоты и шине щ входных сигналов, а вторые входы 8 и 9 через первый элемент И 10 — к единичным выходам триггерон 4 и 5, второй и третий элементы И 11 и 12, перные входы которых соединены с выЭ ходами триггеров 4 и 5, четвертый и пятый элементы И 13 и 14, первые входы которых соединены с выходом генератора 1 опорных импульсов„ а выходы — с входами реверсивного счетчика 75, счетчик 16 циклов, соединенный с выходом элемента И 10. формирователи 17 — 19 импульсов, элемент ИЛИ 20, элемент И 21 и 22, дополнительный ренерсивный счетчик

23, элементы И7П4 24 — 26, причем вход формирователя 17 подключен через элемент ИЗЖ 20 к выходам триггерон 4 и 5, первый выход формирователя 17 соединен с входом элементов И 17 и 72 а второй выход — с входами дополнительных элементов И

21 и 2?, вторые, третьи и четвертые входы которых соединены с выходами триггеров 4 и 5 и выходом генератора 1 опорных сигналов, выходы элементов И 21 и 22 подключены к входам дополнительного реверсивного счетчика 23, выходы переполнения которого через формирователи 18 и 19 соединены с первыми входами элементов ИЛИ

24 и 25, вторые входы которых соединены с выходами элементов И 11 и 12, а выхоцы элементов ИЛИ 24 и 25 подключены к входам управления коэффициентом деления делителя 2 и вторым входам элементов И 13 и 14, кроме того, выходы переполнения счетчика

23 и выход счетчика 16 циклов соединены через элемент ИЛИ 26 с входом начальной установки счетчика 23.

Устройство работает следующим образом.

В известных устройствах выходные сигналы фазового рассогласования между входными и вспомогательными импульсами поделенной опорной частоты поступают на вход управления коэффициентом деления непосредственно, обеспечивая полный режим компенсации н каждом цикле измерения — периоде входных сигналов, что и обуславливает синхронное изменение отсчета.

В предлагаемом устройстве управление делителем 2 производится но двум каналам: непосредственно через элементы И 11 и 12 и через накопительный счетчик 23, элементы И 21 и 22 и формирователи 18 и 19. Причем непосредственное управление через элементы И 11 и 12 производится в случае больших значений временного рассогласования, что соответствует большой скорости изменения фазы, а управление через усредняющий накопитель — при малых значениях скорости изменения фазы и соответственно малом значении рассогласования. Разделение контуров управления производится с помощью фор мирователя 17, вырабатывающего сигнал при каждом сравнении входных и нспомогательных сигналов длительностью, ранной или большей флуктуации фазы входных сигналов в режиме покоя, 3 1205055 и управляющего работой элементов И 11, 12, 21 и 22, Управление делителем в режиме малых скоростей или в режиме покоя через элементы И 21 и 22 производится путем промежуточного накопления сигналов рассогласования с учетом знака рассогласования за несколько циклов сравнения, число которых определяется счетчиком 16 циклов.

На фиг. 2 0, О показаны вспомогательные и входные сигналы на входе фазового дискриминатора. При неизменной фазе входных сигналов на входе

7 они совпадают во времени с сигналами (фиг. 2, моменты времени Т, Т ) вспомогательной последовательности, в результате триггеры 4 и 5 опрокидываются в единичное состояние одновременно (фиг. 2 с, d,) поэтому сигналы на выходах элементов И 11, 12, 21 и 22 (фиг. 2е,f,g,h) не форсируют. ся, Возврат триггеров в исходное состояние производится сигналом (фиг. 2i) с элемента И 10. Сигналами с выходов триггеров через элемент ИЛИ 20 запускается формирователь 17 импульсов, прямой выход которого подключен к элементам И 21 и 22, а инверсный — к входам элементов И 11 и 12. Такое состояние схемы соответствует динамическому равновесию.при неизменной фазе.

В случае изменения фазы входных сигналов, например, в сторону опережения (фиг. 2, момент Tp ), триггер 5 устанавливается в состояние

"1" раньше триггера 4 на время 6Ч определяемое скоростью изменения фазы. Сигналом с триггера 5 (фиг.26) запускается формирователь 17, формирующий импульс длительностью с помощью которого сигнал ь f разделяется на два импульса: 7» — на выходе элемента И 22 и à — на выходе элемента И 12.

Nap

Значение Т выбирают равным или большим флуктуации фазы в режиме равновесия, поэтому режим при ь У)7 соответствует режиму больших скоростей, а при ьУсТ режиму малых скоростей изменения фазы.

В соответствии с этим сигнал Ч. формируемый элементом И 12, поступает непосредственно на вход делителя 2 через элемент ИЛИ 25.

Сигналы опорной частоты в промежутке C на выходах элементов

И 21 и 22, охватывающие зону девиации входного сигнала, поступают на вход реверсивного счетчика 23, выполняющего функции накопительного элемента, формирующего на выходах переполнения среднее за цикл усреднения количество импульсов. Цикл усреднения определяется счетчиком 16 циклов, выходной сигнал которого через элемент ИЛИ 26 приводит в начале каждого цикла усреднения счетчик 23 в исходное состояние.

Каждым сигналом переполнения счетчика 23 запускается соответствующий формирователь импульсов с длительностью, равной одному периоду следования опорных сигналов, обеспечивающих через элементы ИЛИ 24 и 25 коррекцию временного положения вспомогательных сигналов на один период опорных сигналов.

Режим циклического счета счетчИка 23 — от 0 до + N в одном направлении и от 0 до — N в другом направлении, Сигналы переполнения формируются только при переходе через состояние + N с возвратом в исходное

З0 состояние "0" после каждого переполнения благодаря обратной связи через элемент ИЛИ 26, поэтому число Ncp коррекций (сигналов переноса) может быть выражено как целая часть числа (П

,е n; — число опорных сигналов в

40 каждом из промежутков на выходах элементов И 21 и 22;.

N — объем счетчика 23; ш — число циклов сравнения за цикл усреднения.

Для безошибочной работы при минимально регистрируемой в каждом цикле усреднения скорости (когда n, =1) должно выполняться условие m N, 50 т,е. изменение временного положения вспомогательных сигналов и изменение отсчета в счетчике 23 происходит тогда, когда суммарное число импульсов обоих направлений элементов И 21 и

22 превышает объем N счетчика. Если при флуктуации фазы входных сигналов с формированием сигналов разных направлений на выходах элементов И 2 1 и

Таким образом, введение дополнительных блоков обеспечивает формирование усредненного результата, т.е. повышение достоверности отсчета

10 в режиме малых скоростей при сохранении динамических характеристик при больших скоростях, 5 1205055 6

22 в результате счета в разных нап- дывания, причем cHI H, .г, ф„ равлениях состояние счетчика за цикл руется, а сигнал,авен ас усреднения не достигает значения + М, сованию между сигналами, показан„ы— изменения состояния делителя и от- ми на фиг. 2 а счета счетчика 15 не производится.

Дробная часть числа И ц (остаток в счетчике 23) в начале каждого цикла сбрасывается сигналом со счетчика

16 циклов.

На фиг. 2 (момент Т ) — показан случай, когда сдвиг фазы входных сигналов происходит в сторону запаз1205055

1z

Фиг. 2

Составитель Старостина

Редактор А. Лежнина Техред М.Кузьма Корректор Т. Колб

Заказ 8522/46 Тираж 747 Подписное

ВНИИПИ .Государственного комитета СССР ло делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная,