Устройство для распределения заданий процессорам

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ " ь

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3753119/24-24 (22) 12.06.84 (46) 15.01.86. Бюл. Ф 2 (72) В.А.Богатырев (53) 681.328(088.8) (56) Авторское свидетельство СССР и 866560, кл.- 06 F 9/46.

Авторское свидетельство СССР

В 913377, кл. G 06 Р 9/46.

Авторское свидетельство СССР

У 982005, кл. 4 06 F 9/46. (54 ) (57 ) 1 . УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ ПРОЦЕССОРАМ, содержащее блок памяти, адресный вход которого подключен к входу кода запрашиваемой функции устройства, выход разрешения чтения блока памяти подключен к входу запуска устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет распределения запросов с учетом загруженности процессоров, оно содержит блок выделения наименьшего кода, узел приоритета, группу реверсивных счетчиков и группу элементов И, при этом выход блока памяти подключен к первой группе информационных входов блока вьщеления наименьшего кода, вторая группа информационных входов блока выделения наименьшего кода подключена к выходам счетчиков, информационные выходы блока выделения наименьmего кода подключены к информационным входам узла приоритета, вход запуска устройства подключен к входу запуска блока вьщеления наименьшего кода, выход окончания выборки блока вьщеления наименьшего кода подключен

„„Я0„„1205144 A (в 4 G 06 F 9/46 к стробирующему входу узла приоритета, информационные выходы узла приоритета подключены к первым входам элементов И группы, к выходам управления загрузкой устройства и к суммирующим входам соответствующих счетчиков, вычитающие входы счетчиков подключены к входам регистрации выполненных заданий устройства, вторые входы элементов И группы подключены к входу кода запрашиваемой функции устройства, выходы элементов

И группы являются выходами кода запрашиваемой функции устройства.

2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что блок вьщеления наименьшего кода содержит п триггеров, л схем сравнения, а мультиплексоров, т магистральных усилителей (где и — число процессоров в системе), счетчик, элемент задержки и генератор тактовых импульсов, при этом первая группа информационных входов блока подключена к информационным входам триггеров, синхровходы триггеров подключены к выходу элемента задержки, к запускающему входу генератора тактовых импульсов и к входу обнуления счетчика, входы обнуления триггеров подключены к выходам соответствующих схем сравнения, первые входы схем сравнения подключены к выходам мультиплексоров и к информационным входам усилителей, информационные входы мультиплексоров подключены к второй группе информационных входов блока, адресные входы мультиплексоров объединены и подключены к информационному выходу счетчика, выход переноса

1205144

15

30

35 счетчика подключен. к выходу окончания выборки блока и к входу блокиров ки генератора тактовых импульсов, выход генератора тактовых импульсов подключен к счетному входу счетчика, Изобретение относится к вычислительной технике и может найти применение в многопроцессорных системах для распределения нагрузки между процессорами.

Цель изобретения — расширение функциональных воэможностей эа счет динамического распределения запросов с учетом загруженности процессоров.

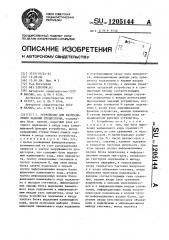

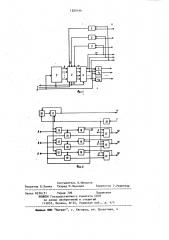

На фиг,1 изображена структурная схема устройства; на фиг,2 — схема

-блока нахождения наименьшего кода.

Устройство содержит элементы И 1, блок 2 памяти, блок 3 выделения наименьшего кода, узел 4 приоритета и группу счетчиков 5, при этом адресный вход блока 2 памяти подключен к входу 6 кода запрашиваемой функции устройства, вход разрешения чтения блока 2 памяти — к управляющему входу 7 устройства, информационный выход блока 2 памяти подключен к первым информационным- входам

8 блока выделения наименьшего кода, вторые информационные входы 9 которого подключены к выходам счетчиков

5, информационные выходы 10 — к информационным входам узла 4 приоритета, управляющий вход — к управляющему входу 7 устройства, а сигнальный выход 11 — к первому сигнальному выходу устройства и управляющему входу схемы 4 приоритета, выходы которой подклкчены к первым входам элементов И 1, к вторым выходам 12 управления загрузкой устройства и входам сложения соответствующих счетчиков 5, вычитающие входы которых подключены к входам регистрации выполненных заданий устройства, вто40 рые входы элементов И 1 подключены к входу кода запрашиваемой функции устройства,авыходы-ккодовым выходам кода запрашиваемойфункции устройства. выходы триггеров являются информационными выходами блока и подключены к управляющим входам усилителей, выход элемента задержки подключен к входу запуска блока.

Блок выделений наименьшего кода (фиг.2) содержит в триггеров 13, п1 схем 14 сравнения, rn мультиплексоров

15, rn магистральных усилителей 16, счетчик 17, элемент 18 задержки и генератор 1 9 тактовых импульсов, при этом первые информационные входы 8 блока подключены к информационным входам триггеров 13, синхровходы которых подключены к входу обнуления счетчика 17, входу запуска генератора 1 9 импульсов и к выходу элемента

18 задержки, входы обнуления триггеров — к выходам соответствующих схем

14 сравнения, первые входы которых подключены к выходам мультиплексора

15 и к информационным входам усилителей 16, а вторые — к объединенным между собой выходам 20 усилителей 16, информационные входы мультиплексоров

15 подключены к вторым информационным входам 9 блока 3, а адресные к информационному выходу счетчика 17, выход переноса которого подключен к выходу 11 окончания выборки блока 3 и к входу блокировки генератора 19 импульсов, выход которого подключен к счетному входу счетчика 17, выходы триггеров 13 являются информационными выходами 10 блока 3 и подключены к управляющим входам усилителей 16, вход элемента 18 задержки подключен к входу 7 запуска блока 3 °

Устройство работает следующим образом, Устройство осуществляет динамическое распределение запросов между процессорами с учетом их функциональных воэможностей (способности выполнить запрашиваемую функцию) и загруженности процессоров. Функциональные возможности процессоров отображаются в блоке 2 памяти, при этом, если

1 -й процессор способен выполнить

1205144 функцию 11;, то в ячейку 2; заносится "1", если нет — 0 °

Код запрашиваемой функции

f,(1 = 1, 2,..., n) поступает с входа

6 кода запрашиваемой функции устройства на адресный вход блока 2 памяти и сопровождается сигналом на лйнии 7.

На выход блока 2 памяти вьдается содержимое -й строки, разряды, содержащие "1", сдответствуют процессорам, 10 способным выполнить запрашиваемую функцию. В блоке 3 происходит определение наыченее загруженных процессоров, способных выполнить запрашиваемую функцию. Информация о способ- 15 ности процессоров выполнять запрашиваемую функцию поступает на вход

8 блока 3 с выходов блока 2 памяти, информация о загруженности процессоров поступает на входы 9 с выходов счетчиков 5. Содержимое счетчика 5 соответствует числу задач, находя щихся на обслуживании в j -м процес— соре. В результате работы блока 3 на его выход 10 выдается "1" при 25

"1" на входе 8 и нахождении в счет1 чике 5 кода не большего чем в ос) I тальных счетчиках 5. Если в нескольких счетчиках находятся одинаковые коды, то выделение одной "1" с выходов 10 происходит на схеме 4 приоритета по сигналу на выходе 11 блока 3, вьдаваемом при завершении поиска наименьшего кода. С выхода 12 схемы 4 приоритета сигнал поступает на вход загрузки 1 -ro процессора, на вход прибавления единицы к счетчику 5 и на управляющий вход элемен1 та И 1 . При этом на информационный . 1 вход j -го процессора через элемент

И 1 подается код запрашиваемой функции с входа 6 кода запрашиваемой функции устройства. При завершении

)-м процессором выполнения каждойлибо функции на вычитающий вход счетчика 51 поступает сигнал, производящий уменьшение на единицу содержимого счетчика 51 ° !

Блок 3 выделения наименьшего кода работает следующим образом.

По сигналу на входе 7, задержанному на элементе 18 на время считывания с блока 2 памяти, производится обнуление счетчика 17, запуск генератора 19 тактовых импульсов и запись в триггеры 13 кода с входа 8 блока 3. Если триггер 13 содержит единицу, то через усилитель 16 и мультиплексор 15 на общую линию 20 ! выдается содержимое к-ro разряда счетчика 5 (к = 1,2,...,01, где а разрядность счетчиков 5), начиная со старшего разряда. Разряд счетчиков вьдаваемь|й на линию 20, задается счетчиком 17, имеющим коэффициент пересчета, равный разрядности счетчиков 5. На выходах мультиплексоров

15 происходит инвертирование соот-. ветствующих разрядов счетчиков 5.

На линии 20 формируется логическая 1 для магистралей уровень логической

I — низкий), если хотя бы с одного усилителя 16 выдается уровень логической единицы. На схемах 14 сравнения происходит сравнение бита на линии 20 с битом, вьдаваемым с инверсного выхода мультиплексоров 15. Если на выходе мультиплексора 15 находит,! ся низкий потенциал, а на линии 20 потенциал логической 1, то на выходе схемы 14 сравнения формируется сиг1 нал, по которому триггер 13 обнуляется. Это происходит, если инвертированный разряд счетчика 5, подключаемый на линию 20, не является наибольшим из соответствующих разрядов других счетчиков, подключаемых на линию 20. Таким образом, к завершению цикла работы счетчика 17 при формировании им переноса в триггерах 13 сохраняются "1", если в соответствующих счетчиках 5 находятся наименьшие коды. Сигнал переноса счетчика 17 .блокирует работу генератора 19 тактовых импульсов и поступает на сигнальный выход 11 блока 3.

1205144

7 б

Составитель В.Минаков

Редактор Е. Копча Техред М.Пароцай

Корректор Г.Решетник

Филиал ППП "Патент", r, Ужгород, ул, Проектная, 4

Заказ 8536/51 Тираж 109

ВНИИПИ Государственного по делам изобретений

113035, Москва, Ж-35, Подписное комитета СССР и открытий

Раушская наб., д. 4/5