Устройство для защиты памяти при отключении питания

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (594 11 С 29 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOINY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3783063/24-24 (22) 06.07.84. (46) 15 ° 01.86. Бюл. В 2 (72) В.Н. Карякин, Ю.И. Сучков, В.М. Данилов, В.П. Белоусов и А.С. Турусов (53) 681.327(088.8) (56) Авторское свидетельство СССР

Ф 619967, кл. G 11 С 29/00, 1977.

Авторское свидетельство СССР

У 568973, кл. G 11 С 29/00, 1974. (54) (57) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ ПРИ ОТКЛЮЧЕНИИ ПИТАНИЯ, содержащее первый датчик сетевого напряжения, первый и второй ключи, входы которых являются одними из входов устройства, первый и второй элементы

И, элемент задержки, выход которого подключен к входу узла блокировки, выход которого является первым вьг ходом устройства, о т л и ч а ющ е е с я тем, что, с целью повьппения быстродействия устройства, в него введены второй датчик сетевого напряжения, интегрирующие блоки, счетчики, триггеры и элемент ИЛИ, выход которого подключен к входу элемента задержки, а первый и второй входы соединены соответственно с выходами первого и второго элементов И, причем входы первого и вто„„Я0„„1205193 A рого датчиков сетевого напряжения являются другим входом устройства, выход первого датчика сетевого напряжения соединен с входом первого интегрирующего блока, первый выход которого подключен к входу установки в "0" первого счетчика и входам запуска первого триггера и первого ключа, а второй выход — к первому входу первого элемента И и входу сброса первого ключа, выход которого соединен со счетным входом пер" вого счетчика, выход которого подключен к входу сброса первого триггера, прямой выход которого соединен с вторым входом первого элемента И, вы- Е ход второго датчика сетевого напряжения подключен к входу второго интегрирующего блока, первый выход кото- С рого соединен со входом установки в "0" второго счетчика и входом сбро- Я са второго ключа, а второй выход— с входами запуска второго триггера и второго ключа, выход которого подключен к счетному входу второго счетчика, выход которого соединен с вхо- Ф дом сброса второго триггера и первым входом второго элемента И, „второй вход которого подключен к пря- © мому выходу второго триггера, выход элемента ИЛИ является вторым выходом устройства.

1205193 2

Изобретение относится к вычислительной технике и может быть использовано в различных системах обработки данных, которые критичны к потерям информации в ЗУ при снятии напряжения питания.

Целью изобретения является повышение быстродействия установки.

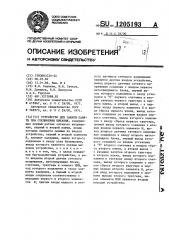

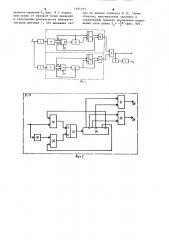

На фиг. 1 приведена функциональная схема предложенного устройства, на фиг. 2 и 3 — функциональные схемы наиболее предпочтительных вариантов выполнения соответственно интегрирующих блоков и ключей; на фиг. 4-6 принципиальные схемы наиболее предпочтительных вариантов выполнения первого и второго датчиков сетевого напряжения и узла блокировки соответ. ственно; на фиг, 7 и 8 — временные диаграммы, поясняющие работу устройства.

Предложенное устройство содержит (фиг. 1) первый 1 и второй 2 датчики сетевого напряжения с входами 3 ° На фиг. 1 обозначены первый выход 4 устройства. Устройство содержит также элемент ИЛИ 5, элемент задержки

6, узел 7 блокировки, первый интегрирующий блок 8, первый ключ 9, первый. счетчик 10, первый триггер 11, первый элемент И 12, второй интегрирующий блок 13, второй ключ 14, второй счетчик 15, второй триггер 16 и второй элемент И 17.

Первый 8 и второй 13 интегрирующие блоки содержат каждый (фиг. 2) элемент НЕ 18, элементы И 19-22, триггер 23 и регистр 24 сдвига.

Каждый из ключей 9 и t4 содержит (фиг. 3) триггер 25 и элемент И 26.

На фиг. 1 — 3 обозначены входы 27 устройства, выходы 28 и 29 интегрирующих блоков 8 и 13.

Первый датчик 1 сетевого напряжения содержит (фиг. 4) резистор 30 и стабилитрон 31, включенные по схеме ограничения напряжения по верхнему уровню.

Второй датчик 2 сетевого напряжения содержит (фиг. 5) сопротивление 32 и стаблитрон 33, включенные по схеме ограничения напряжения по нижнему уровню.

Узел 7 блокировки содержит (фиг.6) триод 34 и нормально разомкнутые контакты 35 реле включения питания.

На фиг. 7 изображены диаграммы напряжений на входе {фиг. 7а) и на

ЗО

55 выходе (фиг. 7P) датчика 1. На фиг.8 изображены диаграммы напряжений на входе (фиг. 8а) и на выходе (фиг.85 ) датчика 2. Ра фиг. 7 д,8 и 8 а, 8 обозначены моменты времени, ц, ино тервалы времени — „,ь .и значения

U Ц напряжений ограничения,.

Предложенное устройство работает следующим образом.

Ца выходе датчика 1 (фиг. 1) при нормальной работе имеются импульсы длительностью о, (меньше длительности половины периода частоты сети). При пропадании напряжения сети в момент

2,(фиг. 7ci) на выходе датчика 1 появится импульс длиной (фиг. 7Е) (короче С,) „

На выходе датчика 2 при нормальной работе имеются непрерывные импульсы с расстоянием между ними длительностью r> (фиг. 85).

При пропадании напряжения сети в момент времени, близкий или равный о (фиг. 8о), за счет паразитиной индуктивности самой сети вырабатывается обратный импульс, по времени близкий к периоду сети, а по напряжению значительно ниже номинального.

В этом случае датчик f выдает импульс, близкий к номинальным параметрам, а датчик 2 за счет выбора порога ограничения U<(фиг. Яд) выше паразитного выброса не выдает импульса. Импульсы с выхода датчика 1 поступают на вход блока 8, затем — на входы ключа 9, счетчика 10, триггера 1t и элемента И 12, которые анализируют сигналы положительной полярности. При длительности выходного сигнала датчика I, меньшей длительности 2, (фиг. 78), на выходе элемента И 12 выдается сигнал, свидетельствующий о пропадании напряжения сети, Импульсы с выхода датчика 2 поступают на вход блока 13, а с его выходов вЂ, на входы ключа 14, счетчика 15, триггера

16 и элемента И 17, предназначенных для измерения длительности с >(фиг.8 ) между сигналами датчика 2. При длительности паузы между сигналами датчика 2 больше номинальной на выходе элемента И 17 появляется сигнал, свидетельствующий о пропадании напряжения сети. С выхода датчика 1 (или датчика 2) сигнал поступает на вход элемента И 19 (фиг. 2> и через элемент НЕ 18 на вход элемента Ч 20.

При поступлении сигнала единичного

1205193

55 уровня и разрешающем потенциале на другом входе элемента И 19 сигнал с его выхода поступает на вход триггера 23 и взводит его. Единичный потенциал с выхода триггера 23 поступает на вход регистра 24 и начинает продвигаться по нему со скоростью, определяемой сдвигающей частотой на входе 27, В первом такте сдвига будет взведен первый разряд регистра 24, а второй его разряд останется в предыдущем состоянии, при этом на выходах регистра 24 установятся единичные потенциалы, которые поступают на входы элемента И 21. В результате на выходе 28 вырабатывается сигнал "Начало", Во втором такте сдвигающей частоты информация из первого разряда регистра 24 переписывается во второй разряд, а в первом разряде подтверждается прежний потенциал. В результате на вход элемента И 21 поступает нулевой потенциал и на выходе элемента И 21 сигнал

"Начало" заканчивается.

Есди до достижения единичным потенциалом последнего разряда реги— стра 24 произойдет смена полярности входного сигнала на входе блока 8 (или 13), то переключения триггера

23 не произойдет, так как последний разряд регистра 24 остался в прежнем положении и выдает разрешающий потенциал на вход элемента И 19 и запрещающий сигнал на вход элемента

И 20, в результате триггер 23 остается в прежнем положении. По достижении единичным входным сигналом последнего разряда регистра 24 через и тактов (где И вЂ” число разрядов регистра 24) сдвигающей частоты 1 разрешающий потенциал с выхода регистра 24 поступает на вход элемента

И 20, а соответственно, запрещающий потенциал — на вход элемента

И 19, тем самым разрешается пр . поступлении нулевого входного, сигнала на вход блока 8 (или 13) переключение триггера 23 и получение через такт сигнала "Конец" на выходе

29 элемента И 22, а через И тактов— разрешение на прием триггером 23 единичного сигнала. Таким образом, блоки 8 и 13 не реагируют на входные сигналы, длительность которых коРоче вРемени " х Т Ав где Т Ав. период сдвигающей частоты. В описываемом устройстве это время выбрано, например, равным 10 мкс. т ft

При поступлении сигнала Начало на вход ключа 9 (или 14) взводится триггер 25, с выхода которого потенциал поступает на вход элемента

И 26 и разрешает прохождение сигналов сдвигающей частоты через второй вход элемента И 26 на выход его.При поступлении сигнала "Конец" триггер

25 выключается и блокирует элемент

И 26, запрещая прохождение сдвигающей частоты на его выход.

Таким образом, если параметры сигналов датчиков 1 и 2 находятся в норме, то на выходах элементов

И 12 и 17 не вырабатываются сигналы, с элемента ИЛИ 5 сигнал не поступает на выход устройства и на вход узла 7..

При выходе параметров сигналов одного из датчиков 1 и 2 за допустимые пределы на выходах элементов И 12 (17) вырабатывается сигнал, который через элемент ИЛИ 5 поступает на выход устройства и одновременно на вход элемента задержки 6, где задерживается на гремя, отведенное для аварийного завершения программы ЦВМ, а с выхода элемента задержки 6 поступает на вход узла 7, который осуществляет по выходу 4 блокировку всех обращений к накопителю (условно не показанному) .

При появлении сигнала на входе узла 7 триод 34 (фиг. 6) открьгяается и блокирует обращения к накопителю, тем cBMbM предотвр щая порчу информации во время переходных процессов при пропадании напряжения питания. После отключения питания контакты реле включения питания замыкаются и осуществляют дальнейшую блокировку.

Время определения аварийного отключения сети и время выполнения аварийной программы составляет 4 мс, что позволяет применить для питания накопителя стандартные источники питания, имеющие время удержания напряжения питания в допустимых пределах порядка 5 мс после отключения напряжения. При отключении напряжения сети в момент Я (фиг. 7) задержки во времени определения отключения сети не получается, При пропадании напряжения сети в момент, (фиг. 8g) погрешность определения времени отключения сети равна = †" (фиг.8 )

2. так как в этот момент блок 13 ключ

14, счетчик 15 и триггер 16 не обнаруживают следующий импульс. Сдвиг

5 1 момента времени (фиг. 8 ) вправо или влево от нулевой точки приводит к укорочению длительности выходного сйгнала датчика 1, что вызывает сиг205193 Ь нал на выходе элемента И 12. Таким образом, максимальная задержка в определении времени пропадания напряжения сети равна F = — (фиг. Sd).

s 2

1205193

Фихте ви

Ugbe

ВНИИПИ Заказ 8533/53

Тираж 583 Подписное

Филиал ППП "Патент", г.Ужгород, ул.Проектная, 4