Синхронный делитель частоты на 13

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (59 4 Н 03 К 23/24 (21) 3751964/24-21 (22) 12.06.84 (46) 15.01.86. Бюл. ¹ 2 (72) В.И.Мяснов (53) 621.374(088.8) (56) Будинский Я. Логические цепи в цифровой технике. Под ред. Б.А.Калабекова. Пер. с чеш. М., 1977, с.246, табл ° 6.3 схема М13. (54)(57) СИНХРОННЫЙ ДЕЛИТЕЛЪ ЧАСТОТЫ

НА 13, содержащий четыре 3К -триггера и два элемента И, счетные входы всех 3К -триггеров соединены с тактовой шиной устройства, входы всех 3К -триггеров соединены с шиной сброса устройства, выходы четвертого

-триггера являются выходами устройства, прямой выход первого

Л -триггера соединен с3 -входом второго ЛК -триггера, прямой выход которого соединен с первым входом первого элемента И, выход которого

„„SU„„120538I соединен с Д -входом четвертого 3К триггера, выход второго элемента И соединен с -входом третьего ЛК триггера, отличающийся тем, что, с целью повышения надежности работы устройства, инверсный выход первого -триггера соединен с первым входом второго элемента И и вторым входом первого элемента И, выход которого соединен с k -входом четвертого -триггера, инверсный выход которого соединен с вторым входом второго элемента И, 3 -вход первого 3k -триггера соединен с пря- мым выходом третьего К -триггера, инверсный выход которого соединен с третьим входом первого элемента И и с K -входом второго 1К -триггера, инверсный выход которого соединен с

К-входом первого К -триггера, при этом К-вход третьего 3 К -триггера соединен с прямым выходом второго

ЗК -триггера.

1 l 2053

Изобретение относится к цифровой технике и может быть использовано, например, при построении хронизаторов, цифровых синтезаторов. частоты, эпектромузыкальных инструментов и т.п.

Целью изобретения является повышение надежности работы устройства, что достигается уменьшением ::исла элементов и связей. 11

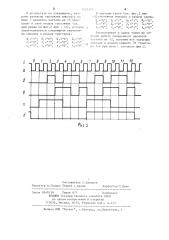

На фиг.1 приведена функциональная схема синхронного делителя частоты на, 13, на фиг.2 — временные диаграммы его рабаты.

Синхронный делитель частоты на 13 15 содержит четыре !1С -триггера 1-4„ два элемента И 5 и 6, тактовую шину

7, шину 8 сброса и выходные шины 9 и 10.

Счетные входы всех k -триггеров 2g

1-4 соединены с тактовой шиной 7 устройства, входы 1 всех 3k -триггеров

1-4 соединены с шикай 8 сброса устройства, выходы четвертого < -триггера 4 являются выходными шинами 25

9 и 10 устройства. Прямой выход первого 3k -триггера 1 соединен с -входом второго С -триггера 2, прямой выход ко араго соединен с К -входом третьего 1k --триггера 3 и первым входом пергаго элемента И5. Выход котарога соединен с - — и k †входами четвертого Jk -триггера 4, иьнэерсный выход которого саецинен с вторым входом второго элемента И 6, выход

I которого соединен с 1 -входом третьеГО 1 риГГ ра 3 4 иньсрсныи ВыхОд каторага с треть4Г1 ьходам первого элемента И 5 -I с ." -.Входом второго

-триггера 2, инверсный выход кото4

40 рого соединен с К -входом первого

1К -триггера 1, инверсный выход котоРОГО соединен с первым! Входом BTopo:p»o элемента И б и с вторым входом перваго элемента И 5, пряма: -ыход третьего k, -триггера 3 соединен с 1 -вхо.-дом первого k -триггера 1.

При указанной схеме-. соединения

=-лемектов логические уравнения для .1 в и К -входов всех 3k -триггерсв предлагаемого синхронного делителя частоты на 13 на 3К -триггерах следу-. ющие: (! 1 э -1 4 !4 0! 2 !4!э 4 12> 2 1 Э 3 григгеров.

По сигналу "Сброс", поступающему по шине 8 сброса устройства, все

11< †.триггеры синхронного делителя

-IBcToTbI íà 13 устанавливаются в исходное нулевое положение. При этом (см. диаграммы на фиг.26,3,2,II) при .:,=0 (где 4 — порядковый номер состояния схемы и порядковый комер входного тактового импульса на тактовой .Тине 7) состояния выходов равны: а — »О» Q --»О» Q — »О» q»QtI 1 4 1 j 1

На основании логических уравнений для,1 — и K -входов 1К -триггеров состояния входов следующие:

k =»0»

4 0

»1», !»1!!

1оскольку каждый 1К -триггер па юслецующему входному тактовому импульсу на шине 7 (на фиг.1 и 2,1 триггеры 1-4} переключается по отрицательному перепаду сигнала на счет- ом входе (при J =.»О" и k =»О» не при

-»1» и K ="1» переключается в проти1I .=!Опаложное состояние, при д = 1 и ! =»О» переклн>чается в состояние лог>. ..c!oA »единицы» а при э ="0" ч к =-» 1» — в состояние логического нул!Я»)1, то по первому входному тактовому импульсу первый, второй и чет:- ерт!Ый,) -триггеры 1, 2 и 4 не изменяют сьоего состояния (см. диаграм»bt 2 3,3,!44)„ а третий )k -триггер 3

-.!ереключается в состояние логической е!:, IHIIöû» (фиг. 22 при I =1) . При этом состояния выходов равны: р -tl11 . Gl — p

1 4

ti0Pt, Д ttptt . У l

ИзменяютсЯ и сОстОЯниЯ ВХОДОВ:

012

0, на прямом выхоце первого 3 k -тригcера 1 !, n — cHI HB!1 Я ходе второго 14 -триггера 2, г сигнал 4) на прямом выхоце третьего

-! -триггера 3, g - сигнал Q 4 на пря-мом выходе четвертого 3 К -триггера 4.

Работа синхронного делителя частоты на i3 полностью описывается логическими уравнениями для — и к -вхадан ега 41 -триггеров. Этими же уравнениями определяется и схема соединения — и k -входов с соответствующими выходами соответствующих К

На фиг.2 обозначено: 4 — Входной сигнал на тактовой шине 7, — сигнал

= ! 1 P1 t 1 -tip», 4 -2

k -Я! 1» с k Il pit !

1 и Е 1 =»1»

k =»О»;

:14 Q", к4 =»О».

120 1!3 акте (см. выходов фиг ° 2 при

В результате по следующему рому входному тактовому импул шине 7 делитель частоты на 13

В третьем т

=3) состояния в,оьcу на пере(см. ходит в свое второе состояние диаграммы на фиг.2 при =2), характеризуется следующими зн которое аченияРассматривая и далее таким же образом работу синхронного делителя частоты на 13, получим все значения

10 вь!ходов и входов каждого к — триггера 1 — 4 при всех согласно фиг.2. ми выходов и входов триггеров:

7 8 9 10 11 12

О S д р

Фиг. 2

Составитель С.Клевцов

РедактоР А.ГУлько ТехРед З.Палий Корректop М.Пожо

Заказ 8540/59 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, ih-35, Раушская наб., д.4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4

1 ="1" ! !

="0">

="1" г

О, ="0"

="0".

7 !

Q1="1", ="0";

="0"

1, ="0", 0-- 0" °!!1 У

="0" ! у

Я !

12 !!z

1 входов равны.

04= 0

= 1!!. 1 О!!

У Э

="1" K ="0".