Устройство для реализации алгоритма волдера

Иллюстрации

Показать всеРеферат

Устройство относится к области вычислительной техники и позволяет сократить время вычисления амплитуды и фазы за счет табличной организации величины второго этапа при реализации рекуррентных соотношений по алгоритму Волдбра, при этом фаза вычисляется во всем диапазоне ее представления . Устройство содержит и итерационных блоков, каждый из которых содержит два сумматора-вычитателя и блок памяти. После выполнения м итераций на выходе первого сумматор а-вычитателя итерационного блока сформируется значение амплитуды сигнала, на выходах знакового разряда итерационных блоков сформируется состояние, однозначно определяю- :щее значение фазы от О до 90, а код на входах ординаты и а бсциссы определяет номер квадранта. 1 ил. IND о О) ч1 Од

СООЗ СОВЕТСКИХ

ЛУЛЕО

РЕСПУБЛИК

:SU 1206776 (51)4 0 06 F 7 548

ГОСУДАРСТВЕННЫЙ КОМИТЕТ CCCP

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТЮ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3785433/24-24 (22) 28.08.84 (46) 23.01.86. Бюл. Р 3 (72) В.И. Горин и А.В. Шанин (53) 681.325(088.8) (56) Балков В.Д., Смолов В.Б. Аппаратурная реализация элементарных, функций в ЭВМ, Л.: изд-во ЛГУ, 1975, с. 71, рис. 21(г,а).

Авторское свидетельство СССР

Н2 813421, кл. G 06 F 7/548, 1978. (54) УСТРОЙСТВО ДЛЯ РЕАЛИЗАЦИИ АЛГОРИТМА ВОЛДЕРА (57) Устройство относится к области вычислительной техники и позволяет сократить время вычисления амплитуды и фазы за счет табличной организации величины второго этапа при реализации рекуррентных соотношений по алгоритму Волдера, при этом фаза вычисляется во всем диапазоне ее представления. Устройство содержит итерационных блоков, калдый иэ которых содержит два сумматора-вычитателя и блок памяти. После выполнения и итераций на выходе первого сумматора-вычитателя итерационного блока сформируется значение амплитуды сигнала, на выходах знакового разряда итерационных блоков сформируется состояние, однозначно определяющее значение фазы от 0 до 90, а код о на входах ординаты и абсциссы опреде- 3 ляет номер квадранта. 1 ил.

1 1

Изобретение относится к области вычислительной техники и может быть использовано в специализированных вычислителях для определения величины амплитуды и фазы сигнала, представленного его квадратурными составляющими.

Цель изобретения — повышение быстродействия вычисления амплитуды и фазы за счет табличной организации величины второго этапа при реализации рекуррентных соотношений по алгоритму Волдера и расширение функциональных возможностей за счет воэможности вычисления фазы. на всем диапазоне ее представления.

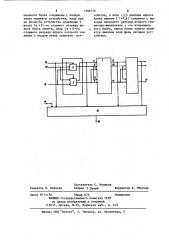

На чертеже приведена структурная схема устройства.

Устройство содержит И итерационных блоков (1-1, 1-2,..., 1 -ч), каждый из которых содержит первый 2 и второй 3 сумматоры-вычитатели, имею.— щие общий управляющий вход 4, первые информационные входы 5 и 6 соответственно первого и второго сумматоров-вычитателей, вторые информационные входы 7 и 8 соответственно первого и второго сумматоров-вычитателей, выход 9 знакового разряда, вто4 рого сумматора-вычитателя, выходы пер-" вого 10 и второго 11 сумматоров-вычитателей, блок 12 памяти, входы знака ординаты 13 и абсциссы 14 устройства входы абсциссы 15 и ординаты 16 устройства, выход 17 амплитуды сигнала и выход 18 кода фазы сигнала.

Устройство работает следующим образом.

Абсолютные значения квадратурных составляющих входного сигнала поступают на входы 1S (х) и 16 (у) первого итерационного блока, а их знаки— на вход 13 (sign у) того же блока и вход 14 (sign х) устройства.

В каждом итерационном блоке осуществляются следующие вычисления

-.1 ;„ = у †. 2, х; sign 11 х. = х.+ 2 „° sign

-4 .

Ji1 j 5 4 Ф причем первое реализуется сумматором-вычитателем 3, а второе - сумматором-вычитателем 2.

После выполнения,л итераций на о выходе 10 последнего блока сформируется значение амплитуды сигнала, а на выходах 9 итерационных блоков сфбрмируется состояние, однозначно определяющее значение фазы в пре20677,6 делах от 0 до 90, а на входе 13 первого итерационного блока и входе

14 устройства — комбинация также однозначно определяющая номер квадрата, которому соответствует мгновенное значение фазы сигнала.

В целом, установившаяся двоичная комбинация на входе 13 первого операционного блока, на входе 14 устройства и на выходах 9 всех итерационных блоков однозначно определяет значение фазы сигнала в диапаэо0 не от 0 до 360 . Эта двоичная комбинация подается на адресные входы блока 12 постоянной памяти, опреде-. лял тот адрес, по которому хранится мгновенное значение фазы сигнала, заданного исходными квадратурными составляющими.

Формула изобретения

Устройство для реализации алгорит. ма Волдера, содержащее 11 итерационных блоков (ll- число итераций),каждый из которых включает два сумматора-вычитателя, причем выходы перного и второго сумматоров-вычитателей

j --ro итерационного блока (j =1 II -1) соединены с первыми входами соответственно первого и второго сумматороввычитателей (j +1)-ro итерационного блока непосредственно и с вторыми входами первого и второго сумматороввычитателей (j +1)-ro итерационного

З5 .блока со сдвигом на j разрядов в сторону младших разрядов, первые входы первого и второго сумматоров-вычи-тателей первого итерационного блока соединены соответственно с входами

40 абсциссы и ординаты устройства, вторые нкоды первого и второго сумматоров-вычитателей первого итерационного блока соединены соответственно с входами ординаты и абсциссы устрой45

5 ства, выход первого сумматора-вычитателя И -го итерационного блока является выходом амплитуды сигнала устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстро50 действия вычисления, в него дополнительно введен блок памяти, причем управляющие входы первого и второго сумматоров-вычитателей (j +1)-ro итерационного блока соединены с выходом

55 знакового разряда второго сумматоравычитателя j -ro итерационного блока, управляющие входы первого и второго сумматоров-вычитателей первого итераСоставитель С. Куликов

Техред . З.палий

Корректор А. Обручар

Редактор В. Иванова

Заказ 8714/50 Тирам 673

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )K-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", r. Ултород, ул. Проектная, 4

3 1206776 4 ционного блока соединены с входом ройства, а вход i --го разряда адреса знака ординаты устройства, вход зна- блока памяти (=1,И) соединен с вы1 ка абсциссы устройства подключен к ходом знакового разряда второго сум-! входу (n +2)-го старшего разряда ад- матора-вычитателя i --го итерационреса блока памяти, вход (п +1)-го ного блока, выход блока памяти являстаршего разряда адреса которого сое- ется выходом кода фазы сигнала устдинен с входом знака ординаты уст- ройства.