Устройство для умножения частоты на код

Иллюстрации

Показать всеРеферат

Устройство относится к области вычислительной техники и может быть использовано в вычислительных системах и системах автоматического управления для преобразования данных в частотно-импульсном коде. Целью изобретения является расширение функциональных возможностей путем обеспечения контроля заправильностью функционирования устройства. Устройство содержит генератор тактовых импульсов, два управляемых делителя частоты, счетчик, два триггера, четыре элемента И, элемент ИЛИ и элемент с тремя устойчивыми состояниями (по выходу) 1 ил. 9 ю о Од 00

СОЮЗ СОВЕТСКИХ

ФНММВЮ

РЕСПУБЛИК.,SU 120 (51)4 G 06 F 7 68

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н *BTOPCHOMY СВИЖТВВФТВУ

ГОСУДМ СТНЕННЫЙ КОМИТЕТ ССОР

OO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТЮ (21) 3604346/24-24 (22) 10.06.83 (46) 23,01.86. Бюл. и 3 (71) Институт машиноведения им. А.А. Благонравова (72) М.Д. Генкин, А.П. Кирилов»-, Г.Ф. Пешков и О.Б. Скворцов (53) 681.325(088.8) (56) The Radio and Electronic

Engineer, 1969, v. 38, Р 6, р.334335.

Авторское свидетельство СССР

N 580555, кл. С 06 F 7/68, 1976. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧАСТОТЫ

НА КОД (57) Устройство относится к области вычислительной техники и моает быть использовано в вычислительных системах и системах автоматического управления для преобразования данных в частотно-импульсном коде. Целью изобретения является расширение функциональных возмолжостей путем обеспе-. чения контроля sa правильностью функционирования устройства. Устройство содержит генератор тактовых импульсов, два управляемых делителя частоты, счетчик, два триггера, четыре элемента И, элемент ИПИ и элемент с тремя устойчивыми состояниями (по выходу)

1 ил.

1206780

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах и системах автоматического управления для преобразования данных в частотно-импульсном коде.

Целью изобретения является расширение функциональных возможностей за счет обеспечения контроля за правильностью функционирования устройства.

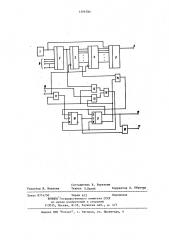

На чертеже показана функциональная схема устройства.

Устройство для умножения час.тоты на код содержит генератор 1 15 тактовых импульсов, управляемый делитель 2 частоты, счетчик 3, регистр

4, управляемый делитель 5 частоты, выход которого является выходом 6 устройства, информационный вход 7 которо-20 го соединен с входом управления записью регистра 4 и входом обнуления счетчика 3, счетный вход которого соединен с выходом управляемого делителя 2 частоты, управляющие входы ко- 25 торого соединены с шиной 8 задания коэффициента умножения, информационный вход управляемого делителя 2 частоты соединен с выходом генератора 1 тактовых импульсов и информационным входом управляемого делителя б частоты, управляющие входы которого соединены с выходами разрядов регистра 4, входы разрядов которого соединены с выходами раз- 35 рядов счетчика 3. Устройство для умножения частоты на код содержит также триггеры 9 и 10, элементы

И 11-14, элемент ИЛИ 15 и элемент 16 с тремя устойчивыми состояниями (по 40 выходу)„ выход которого соединен с выходом 17 вида ошибки устройства для умжожения частоты на код, входы 7 и 18 начальной установки которого соединены соответственно с 45 первым входом элемента И 11 и первым входом элемента И 13, второй вход которого соединен с прямым выходом триггера 9, выходом 19 наличия ошибки устройства и входом элемента 16 50 с тремя устойчивыми состояниями (по выходу), другой вход которого соединен со счетным входом триггера

9 и прямым выходом триггера 10, нулевой вход кОторого соединен с нулевым входом триггера 9 и выходом элемента ИЛИ 15, первый вход элемента

И 14 соединен с выходом управляемого делителя 2 частоты, а второй вход элемента И 14 соединен с вторым входом элемента И 11, инверсным выходом триггера 9 и первым входом элемента И 12, выход которого соединен с единичными входами триггеров 9 и

10, второй вход элемента И 12 соединен с выходом переноса счетчика 3.

Устройство для умножения частоты на код работает следующим образом.

Входной частотный сигнал подается на вход 7, а код, на который следует умножить частотный сигнал, подается на шину 8. Каждый импульс на входе 7 обеспечивает по заднему фронту сброс счетчика 3 в нулевое состояние. После этого счетчик 3 начинает заполняться импульсами с выхода управляемого делителя 2 частоты, на вход которого подаются импульсы от генератора 1 тактовых импульсов. Если частота импульсов на выходе генератора 1 тактовых импульсов равна

Е, то частота импульсов на входе счетчика 3 равна f /Н, где и — коэффициент деления управляемого делителя 2 частоты, который определяется кодом, поданным на шину 8. Таким образом, за время между импульсами, поступающими на вход 7 в счетчике 3 будет накоплен код К = Е Т/N, где

Т вЂ” период импульсов на входе 7, Т=1/f „ . При поступлении следующего импульса на вход 7 по его переднему фронту код из счетчика 3 переписывается в регистр 4. Управляемый делитель 5 частоты обеспечивает деление частоты импульсов f на К, на выходе 6 устройства формируется сигнал с частотой fr / = fon N Если период импульсов на входе 7 изменяется, то обеспечивается соответствующее изменение и выходного сигнала, однако для нормального функционирования нем обходимо, чтобы К не превышало 2 где М вЂ” разрядность счетчика 3. Кроме того, период импульсов на входе

7 должен быть больше, чем период импульсов на выходе управляемого делителя 2 частоты. Если эти условия не выполняются, устройство не будет правильно функционировать. Контроль эа правильностью функционирования осуществляется следующим образом. В исходном состоянии триггеры 9 и 10 сброшены и на их инверсных выходах сигналы логической единицы. При по06780 з 12 явлении импульсов на выходе управляемого делителя 2 частоты они проходят на нулевые входы триггеров 9 и 10, подтвержцая их состояние. При.поступлении входного импульса по счетному входу переключается триггер 10 от импульса, проходящего через элемент

И 11. Если на вход 7 поступят два.. импульса, а на выходе управляемого делителя частоты 2 импульсов не будет, григгер 10 установится в нулевое состояние, а триггер 9 в единичное состояние, на выходе 19 появится единичный логический сигнал наличия ошибки, который откроет элемент 16, на выходе которого появится нулевой логический сигнал, свидетельствующий, что частота импульсов на входе 7 выше допустимой. Если частота импульсов на входе 7 меньше допустимой, произойдет переполнение счетчика 3, и импульсом с его выхода переноса бу» дет обеспечена установка триггеров

9 и 10 в единичное состояние, что также приведет к появлению сигнала наличия ошибки на выходе 19, причем вид ошибки в этом случае индицируется в виде единичного логического сигнала на выходе 17.

Возврат устройства в исходное состояние возможен только при подаче импульса на вход 18, что позволяет надежно зафиксировать наличие сбоя в работе устройства..

Формула изобретения

Устройство для умножения частоты на код, содержащее два управляемых делителя частоты, счетчик, регистр и генератор тактовых импульсов, выход которого соединен с информационными входами первого и второго управляемых делителей частоты, управляющие входы первого управляемого делителя частоты соединены с шиной задания коэффициента умножения уст ройства, а выход подключен к счетному входу счетчика, выходы разрядов которого соединены с входами разрядов регистра, вход управления записью ко торого соединен с входом обнуления счетчика и информационным входом устройства, а выходы разрядов подключены к управлякщим входам второго управляемого делителя частоты, выход которого соединен с информационным выходом устройства, о т л и1О ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей путем обеспечения контроля за правильностью функционирования устройства, в него введены два триг15 гера, четыре элемента И, элемент ИЛИ и элемент с тремя устойчивыми состо-, яниями, выход которого соединен с выходом вида ошибки устройства, первый вход первого элемента И соединен с

2О информационным входом устройства, счетный вход первого триггера соединен с прямык выходом второго триггера и первым входом элемента с тремя устойчивыми состояниями, второй

25 вход которого соединен с прямым выходом первого триггера и выходом наличия ошибки устройства, выход второго элемента И соединен с единичными входами первого и второго триггеров, щ вход начальной установки устройства подключен к первому входу третьего элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход третьего элемента И соединен с прямым выходом первого триггера, выход первого управляемого дели:,теля частоты соединен с первым входом четвертого элемента И, второй вход которого соединен с вторым вхоО дом первого элемента И, инверсным выходом первого триггера и первым входом второго элемента И, второй вход которого соединен с выходом переноса счетчика, выход четвертого элемента И соединен с вторым входом элемента ИЛИ, выход которого подключен к нулевым входам первого и второго триггеров.

1206780

Составитель В. Березкин

ТехРед З.Палий Корректор А. Обручар

Редактор В. Иванова

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 8714/50 Тираж 673

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5