Устройство для трехточечного быстрого преобразования фурье

Иллюстрации

Показать всеРеферат

COOS СОВЕТСКИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИК (19) (И) 1 А дц 4 G 06 F 15/332

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ц

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3764853/24 24 (22) 04.07.84 (46) 23.01.86.Бюл, Р 3 (71) Институт физики полупроводников СО АН СССР (72) Н.Д.Новоселов, Г.А.Кухарев, Е.И.Черепов и В.С.Скорняков (53) 681.32(088.8) (56) Кухарев Т.А. и др. Структура процессорных элементов, модульных

БПФ-процессоров. "Известия ВУЗов.

Приборостроение", 198!, т.ХХШ, h 2.

Авторское свидетельство СССР (1107132, кл. G 06 F 15/332, 1984. (54)(57) УСТРОЙСТВО ДПЯ ТРЕХТОЧЕЧНОГО БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащее первый сумматор-вычитатель, выход суммы которого подключен к информационному входу регистра, информационный выход которого подключен к первому входу второго сумматора-вычитателя, выход разности которого подключен к первому входу третьего сумматора-вычитателя, причем выход суммы второго сумматоравычитателя, выход суммы и выход разности третьего сумматора-вычитателя являются выходами соответственно первого, второго и третьего операндов устройства, входами первого, второго и третьего операндов которого являются соответственно второй вход второго сумматора-вычитателя и первый и второй входы второго сумматоравычитателя, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит первый и второй сумматоры, вычитатель, умножитель на 1/16 и первый и второй умножители на 1/8, выход первого умножителя на 1/8 подключен к первому входу первого сумматора, выход которого подключен к входу умножителя на !

/16, выход которого подключен к пер— вому входу второго сумматора, выход которого подключен к входу второго умножителя на 1/8, выход которого подключен к первому входу вычитателя, выход которого подключен к второму входу третьего сумматора-вычитателя„ а выход разности первого сумматоравычитателя подключен к вторым входам вычитателя и первого и второго сумматоров.

1 12

Изобретение относится к аычислительной технике и может быть ис:пользовано в специализированных пвс?пессорах быстрого преобразованля Фурье . (БПФ) высокой производительности: Цель изобретения — упрощение устройства.

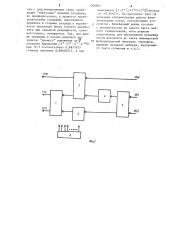

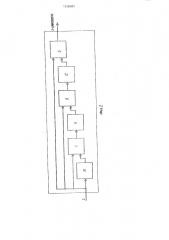

На фиг.l представлена функциональ ная схема устройства; на фиг.2 схема блока сумматоров; на фиг,3 временные диаграммы работы.

Устройство содержит три суммато— ра-вычитателя (блока двухточечного ДПФ) 1-3, регистр 4, блок 5 сумматоров, блок 6 синхронизации. Блок сумматоров (фиг.2) содержит сумматоры 7 и 8 вь?читатель9, умножитель )О на 1/8, умножитель. 1) на 1/16 и умножитель 12 на 1/8, Устройство работает следующим образом.

Операнд f(О) поступает на второй вход третьего сумматора-вычитателн, а операнды f(I) и f(2) поступают соответственно на входы сумматора-вычитателя, выход суммы которого f(1)+

+Е(2) соединен с регистром А. Сумма f (1)+Х(2) через регистр 4 без изменения поступает на Входной регистр сумматора-вычитателя 3. и !3 Виде (. /2 P f () )+f (2)) поступает на входной регистр вычигателя того же бла са, причем результат F(G)=f(0)+

+»(!,+f(2) поступает на выход уст, ройства. а результат F(0)+1/7 1»((1)-

+f(2)(поступает на вход сумматоравычитателя 1, на Выходе которого лов лучается

Р(1)==f(О) — 1/2 jf(1)+»(2)1 + .; и f(1) f(2)

Результат f(1)-f(2) с выход-. сум-МВТпрВ-вычитателя 2 поступает на вход блока 5 сумматоров., на вьг -.оде которого получается величина .1- )а(г(!, "-f(2)j котора.я по-тупает на Bõoä сумматора-вычитателя 1, на выходе которого появляется значе=ив

F (2)=f (O) — 1/2 ?» (1)+Й(2),-q — :» (11-й(2)) .

Блок сумматоров работает следующим образом.

Входной операнд М разрядностью и поступает на вход сумматора 7, на цругой вход этого сумматора поступает значение операнда Х,сдвинутое на три разряда вправо, т., 0,125 11 „

Значение суммы 1,125 Х с Выхода сум0680 1 матора 7, сцвинутое IIo четыре разряда Вправо, т. е. 0,0703125 )(постуПBET ?ла ВхОд су ??лвтот3а 8 „на вход

ВТОРОГО СУМ?"атагРа»:РИХОДИТ ЗиаЧЕние (. Значение суммы 1,0703125 < с выхода oó IìàòoðB, сдвинутое на т)?и разрл,та вправо, т..е. 0„1337890625 )(гоступает на вход вы,?лтателя,,!B другой вход которог0

1 д прыхОГHT зн . t eни )(На В-=:,!ходе вычитателя получаем BHB÷åíèå

0,,8662109375 ?(, что соответствует вепичине -- y, В даннои интерпретаI3 г ци:-. с coo TBc Tств ующей точностью. ВыС.ход вь?читателя является выходом блока сумматоров. Таким образом все устройство реализуеr вычисления по формулам (2 (Р(0) = .Г (О) + f (1) +» (2),"

2() Р (1) = (О) — (1)+» (2)+j 1Я Pf (1)—

-1 (2Я1 . (2)

F (2) =f (О) — 1/2 (f ())+f (2)1 (f (1) — f (2) 1 -" . 7

Устройство управляется стандарт—

2 ныл блоком 6 синхронизации. ."множители фиГ.,"i Осу?пестВляют сдВиГи ин— формационных разрядов; умножитель .0 на >ри разряда вправо 2 — 3J, умножител; 11 на четыре разряда вправо

ЗО (7-4), умножитель 12 на три разряда

Вправо, 2-3), Физически это представлнет -.сбой жестко фиксированную ком?лутея,-;ю информационных выходов одно1 с регистра хранения с соответству— ю? (11?ли информационными выходами,цругого регистра, 1 (З

В олоке реализуется срункция,(/ с О-.ласно выражению

; (,, ",? -а; "1 - о) ),(-3)-. -4 а)1) ) 1

Тссчность представления зна-ления ксн танты †- =0,8660254 в данной

<2 -Il интерпретации:.Оответствует i.

:н 0 Г i, "-1 фик с ?л р О В ан н о?л формате в 8 Yi 1 6 разр::,. .„Ов,ес:ли учесть,чт0 "; множение осу .ле твляется на константу меньше 1. За счет последовательно-.о аппаратурного сдвиге с подсуммированием повышается (: точно.. ть умножения i í условиях огранил .p!1Ä?ой ра-;рядной сетки реал;ных ма .?èí I по сравнению с умножением по пр?лнц?лпу Одновременных сдвигов и сведения результатов. ?."ëè разрядность равна 8,, ra одновременный сдвиг на

10 разрядов (2, выходит за границу

"ч-;Вс(ьи ельност < Однобайтной разИ01 ти B ?ри 11ос?.едов ат ельных сдВи гах с подсуммированием также происходит "обрезание" младших разрядов, но предварительно, в процессе последовательных сложений, выполняются переносы в старшие разряды и вероятность получения более точного резуль-, тата при заданной разрядности, соответственно, повышается.. Так, при длине операнды в восемь разрядов ревю Il з зультат прямого умножения на

6 -Ъ » -1о!Х согласно выражению (2 -2 -2 -2, Х при Х =! соответствует 0,8671875 (точное значение 0,8660254), а при

20680l 4 выполнении 1-2 3 р1+2 (1-+2 ))J резулЪ ат =0,8662!! . На диаграмме (фиг.З/ показана синхронизация работы функциональных узлов, составляющих устройство. Ковейерный режим показан с дискретностью до одного такта пол- ного суммирования, хотя реально квантование для обеспечения конвейер- ности доводится до такта минимальной !

О функциональной операции (например, времени хранения выборки, внутреннего такта сложения и т.д.) . 2368QI

1206801

Составитель А.Баранов

Редактор П.Коссей Техред Т.Дубинчак Корректор А.Зимокосов

Заказ 8715/51 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г. Ужгород,ул.Проектная, 4