Устройство цифрового преобразования сигналов импульсно- кодовой модуляцией в сигналы с дельта-сигма модуляцией

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

ONI

РЕСПУБЛИК (19) (111 (Я) 4 Н 03 М 7 36

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbtTWI ( фг;;. -...

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMV СВИДЕТЕЛЬСТВУ

«. (21) 3717607/24-24 (22) .08.04.84 (46) 23.01.86. Бюл. М 3 (71) Ленинградский электротехнический институт связи им. проф. М.А. Бонч-Бруевича. (72) Л,М. Гольденберг, А.В. Брунченко и Ю.С. Власюк (53) 621.376.56 (088.8) (56) Electronic Components and

Applications, 1980, ч. 2, У 4, р. 242-250.

Экспресс-информация. Сер. Передача информации. 1980, 9 1, с. 13, пис. 6. (54)(57)УСТРОЙСТВО ЦИФРОВОГО ПРЕОБРАЗОВА1ЩЯ СИГНАЛОВ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ В СИГНАЛЫ С ДЕЛЬТАСИГМА-МОДУЛЯЦИЕЙ, содержащее регистр, первый и второй элементы НЕ и первый сумматор на и разрядов, первые входы и -2 разрядов которого соединены с соответствующими входами устройства, первый вход (n-l) -го разряда подключен к соответствующему входу устройства через первый элемент НЕ, первый вход и -го разряда первого сумматора соединен с выходом второго элемента НЕ, вход которого объединен с вторым входом л-го разряда первого сумматора, вторые входы остальник разрядов которого подключены к выходам соответствующих разрядов регистра, вход синхронизации которого соединен с первой тактовой шиной, о т л и ч а ю щ е е с я тем, что, с целью увеличения отношения сигнал/шум, в него введены второй сумматор на п разрядов, умножитель на два, 17 -триггер и коммутатор, выход которого соединен с выходом устройства, первый вход подключен к выходу

h-ro разряда регистра, управляющий вход коммутатора объединен с входом синхронизации D -триггера и подключен к второй тактовой шине, второй вход коммутатора объединен с входом второго элемента НЕ и подключен к ® выходу З-триггера, информационный вход которого объединен с первым входом n -ro разряда второго сумматора и подключен к выходу tl -го разряда первого сумматора, первые входы ос- Я тальных разрядов второго сумматора соединены с выходами соответствующих разрядов регистра, входы которого подключены к выходам соответствующих разрядов второго сумматора, вторые входы разрядов которого соединены с соответствующими выходами умножителя на два, входы которого объединены с соответствующими первыми входами tl --1 разрядов первого сумматора.

1206963 где d.„, d, l5

920 эи, (2) („, В 5gll (Д„„,1 (3) 6 * так (1Х1), 30 щ П1Ф1 (1Tl

Изобретение относится к вычислительной технике и может быть использовано в системах передачи данных, речи и другой информации.

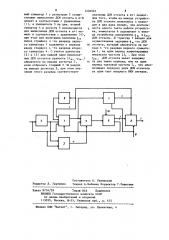

Цель изобретения — увеличение отношения сигнал/шум, На чертеже приведена функциональная схема устройства, Устройство цифрового преобразования сигналов с импульсно-кодовой модуляцией (ИКМ) в сигналы с дельтасигма-модуляцией (ДСМ) содержит первый сумматор 1 на и разрядов,,первые входы h -2 разрядов которого подключены к соответствующим входам устройства, а первый вход его (п-1)го разряда соединен с соответствующим входом устройства через первый элемент НЕ 2, при этом все указан.ные входы первого сумматора 1 объединены с соответствующими входами умножителя 3 на два, выходы которого соединены с входами соответствующих разрядов второго сумматора 4 на . разрядов, выходы последнего соединены с соответствующими входами регистра 5, выход -ro разряда которого подключен к первому входу ком;мутатора 6, выход которого соединен с выходом устройства, а управляющий вход объединен с входом синхронизации 2 -триггера 7 и подключен к второй тактовой шине 8. Выходы остальных разрядов регистра 5 соединены с вторыми входами соответствую- щих разрядов первого сумматора 1 и с другими входами соответствующих разрядов второго сумматора 4. Выход

h-го разряда первого сумматора подключен к другому входу h --го разряда второго сумматора 4 и информационному входу D òðèããåðà 7, выход которого соединен с вторым входом коммутатора р, входом второго элемента HE 9 и вторым входом h -ro разряда первого сумматора 1, первый вход которого подключен к выходу второго элемента HE 9.

Умножнтель 3 на два может быть выполнен, например, в виде перекрестной связи, осуществляющей сдвиг двоичного числа на один разряд в сторону старших разрядов.

Частота повторения тактовых сигналов, поступающих по второй тактовой шине 8, в два раза превышает частоту f тактовых сигналов, приходящих по первой тактовой шине 10.

Устройство работает следующим образом.

Отсчеты ИКМ сигнала поступают на первые входы сумматора I, начиная с

h-1 разряда с входа устройства. Величену сигнала на выходе сумматора 1 в момент времени m можно записать в виде

d„=d + Х - =(а -g )+ сигналы на выходе сумматора соответственно в моменты времени m и m-1;

ИКМ отсчет на входе устройства; сигнал в обратной свяВ момент времени m+1 величина сиг.нала на входе сумматора

Если, величины d и dm„l вычисляются в одном такте входного ИКМ сигна35 ла, то Х„ =Х, а после подстановки йн m

J „= (J,-pm, +2õ„-(Первый элемент НЕ 2 инвертирует старший (знаковый) разряд входного сигнала Х . Второй элемент НЕ 9 служит для того, чтобы обеспечить работу старшего разряда первого сумматора 1 в режиме сложения по модулю два.

Можно исключить второй элемент НЕ 9 при условии, что на один из входов, например на первый вход старшего g

ro разряда первого сумматора 1, подать сигнал, значение которого соответствует значению логической единицы, а на второй вход этого же разряда первого сумматора 1 — сигнал, соответствующий логическому нулю. В 5 этом случае результат, получаемый на выходе первого сумматора 1, будет таким же, как и при использовании второго элемента НЕ 8. При втом перСоставитель О. Ревинский

Редактор Л. Гратилло Техред А.Вабинец Корректор Г.Решетник

Заказ 8734/59 Тираж 818 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

3 1 вый сумматор 1 с регистром 5 осуществляют вычисление ДСМ отсчета в m-й момент в соответствии с уравнением (1), а умножитель 3 на два, второй сумматор 4 и регистр 5 используются для вычисления ДСМ отсчета в ш+1 момент в соответствии с уравнением (4), при этом для вычитания величины выход страшего rl -ro разряда первого сумматора 1 подключен к первому входу старшего л -го разряда второго сумматора 4. С учетом равенства (2.) и (3) для каждой пары вычисленных ДСМ отсчетов разность (6, -g „,) образуется на выходе регистра 5, если отбросить старший и -й разряд на выходе регистра 5, при этом значение этого разряда соответствует

206963 4 значению ДСМ отсчета в ш+1 момент.

Для того, чтобы на выходе устройства ДСМ отсчеты появлялись с периодом в два раза меньше, чем длительность одного такта работы устройства, коммутатор 6 подключает к выходу устройства попеременно и

ДСМ отсчеты. Э -триггер 7 введен для осуществления задержки -го ДСМ

1Î отсчета, который образуется на выходе И -ro разряда первого сумматора 1, на один период коммутирующих импульсов частоты 2f . При этом

ДСМ отсчета имеет задержку на два таких периода, или на один период тактовой частоты, что обеспечивает передачу двух ДСМ отсчетов эа один такт входного ИКМ сигнала.