Биполярный цифровой амплитудный анализатор

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ш4 H 03 М 1/00 (21) 3639673/24-21 (22) 31. 08. 83 (46) 30.01.86. Бюл. У 4 (72) Л.П. Петренко и А.В. Чиликин (53) 621.317(088.8) (56) Бахтиаров Г.jl. и др. Аналогоцифровые преобразователи, М, 1983, с. 215, рис. 7.32а.

Авторское свидетельство СССР

У 651475, кл. Н 03 M 1/00, 1977. (54)(57) БИПОЛЯРНЫЙ ЦИФРОВОЙ АМПЛИТУДНЫЙ АНАЛИЗАТОР, содержащий четыре компаратора, соединенные неинвертирующими входами с входной шиной устройства, инвертирующие входы подключены к соответствующим выходам формирователя эталонных напряжений, содержащего коммутатор, два источника тока и резистивный делитель, соединенный через коммутатор с выходами источников тока, первый выход формирователя эталонных напряжений соединен с инвертирующим входом четвертого компаратора и входом блока контроля, о т— л и ч а ю шийся тем, что, с целью повышения быстродействия, в . него введены малоразрядный биполярный цифровой амплитудный анализатор, ..Я0„,1208605 четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, три элемента И, шифратор и сумматор, вход малоразрядного биполярного амплитудного анализатора соединен с входной шиной устройства, первые два выхода — с входами первого слагаемого сумматора, третий выход— с выходом третвего разряда устройства, первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и управляющим входом формирователя эталонных напряжений, вторые входы элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ соединены с выходами соответст: вующих компараторов, выходы первых трех из которых соединены с входами шифратора, а выход четвертого — с первым входом третьего элемента И, первые входы первого и второго элементов И соединены с выходами шифратора, вторые входы всех элементов И соединены с выходом блока контроля, выходы первых двух элементов И соеди- О иены с входами второго слагаемого Я сумматора, а с входом переноса по- (ф следнего — выход третьего элемента (©

И, выходы сумматора соединены с вы ходами. нулевого, первого и второго разрядов устройства.

Сл

1208605

Изобретение относится к электроизмерительной и преобразовательной технике и может быть использовано для анализа амплитуд биполярных напряжений и преобразования их в цифровой код.

Цель изобретения — повышение быстродействия анализатора путем уменьшения длительности переходных процессов при изменении знака анализируемого напряжения.

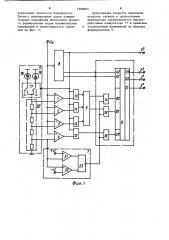

На фиг. 1 приведена схема анализатора; на фиг. 2 — таблица истинности и состояний разрядов отдельных его узлов.

I го

Устройство содержит четыре компаратора 1-4, формирователь 5 эталонных напряжений, сумматор 6, блок

7 контроля, малоразрядный биполярный цифровой амплитудный анализатор

8, шифратор 9, элементы ИСКЛЮЧАНМЦЕЕ

ИЛИ 10-13, элементы И 14-16. Формирователь 5 состоит из коммутатора

17, источников 18 и 19 тока и резис- 25 тивного делителя 22. Блок 7 контроля содержит два компаратора 21 и

22 и элемент И 23. Неинвертирующие входы компараторов 1-4 соединены с входной шиной и входом анализатора ЗО

8, инвертирующие — с выходами формирователя 5, причем первый выход последнего соединен с входом блока

7 контроля, выход которого подключен к вторым входам элементов И 35

14-16, первые входы элементов И 14 и 15 соединены с выходами шифратора 9, а первый вход элемента И 16— с выходом элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ )3. Первые два выхода анализа- 40 тора 8 соединены с входами первого

".слагаемого сумматора 6, а третий выход — с выходом третьего разряда устройства и первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10-13, вторые 45 входы которых соединены с соответствующими выходами компараторов 1-4, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

10-12 соединены с входами шифраторатор 9, выходы которого соединены 50 с первыми входами элементов И 14 и 15, выходы которых соединены с входами второго слагаемого сумматора 6, выход элемента ИСК1ПОЧАЮЩЕЕ

ИЛИ 13 соединен с вторым входом эле- 55 мента И 16, выход которого соединен с входом переноса сумматора 6, выходы которого соединены с выходными шинами нулевого, первого и второго разрядов устройства.

Анализатор работает следующим образом.

На входе блока 7 постоянно присутствует логическая единица, а нулевой уровень появляется лишь на время переключения коммутатора 17.

Для положительных входных напряжений старший разряд анализатора 8 имеет значение "0" (фиг. 2, графа ЦАА 8). В результате к резистивному делителю подключается источник

18 положительного тока так, что на резисторах падает напряжение, равное шагу квантбвания 6U=(U -(-Ц„„)) /28, где U - максимально возможное преобразуемое напряжение. Для рассматриваемого четырехразрядного анализатора 60=0, 125 U . Напряжение на первом выходе формирователя 5

Uw/2=46U. Если входное напряжение

Пп + Uw/2, то компаратор 4 находится в состоянии "0", а на выходе шифратора 9 устанавливается код "00" (фиг. 2, графа СД 9). В результате код анализатора 8 проходит на выход устройства через сумматор 6 без изменения.

Для положительных По>0,5Uh, H Bblходе компаратора 4 устанавливается

"1" (зоны XII-XVI фиг. 2), поступающая на вход переноса сумматора 6.

В результате выходной код устройства образуется путем суммирования кода анализатора 8 с выходным кодом шифратора 9 с учетом переноса (фиг. 2).

При изменении знака входного напряжения на отрицательный состояние старшего разряда анализатора 8 изменяется на "1", выходные напряжения формирователя изменяются на отрицательные. На время переходных процессов на вьглоде блока 7 контроля устанавливается "0" вследствие того, что на неинвертирующий вход компаратора 21 подано положительное напряжение, равное 0,45 Ц„, а на инвертирующий вход компаратора 22— такое же отрицательное напряжение.

В момент переключения на выходах обоих компараторов появляются "1", вызывающие появление на выходе элемента И 23 уровня "0". Таким образом, прохождение логических сигналов через элементы И 14-16 во время

1208605

Äèå. 7 переходных процессов блокируется.

Процесс формирования кодов отрицательных напряжений аналогичен процессу формирования кодов положительных напряжений и иллюстрируется таблицей на фиг. 2.

Допускаемая скорость изменения входного сигнала в предлагаемом анализаторе ограничивается быстродействием коммутатора .17 и временем установления напряжений на выходах формирователя 5.

1208605

Г о

0,К

Составитель В. Латышев

Редактор А. Orap Техред C,Мигунова Корректор,С. Шекмар

Заказ 300/60 Тираж 818 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д..4/5

I 1

1 !!!

l!! 1.

1! I! I

Яаюа 4 ААЮ ЮФ Ю9 т

07

Ю,Г

011

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4