Цифровой синтезатор частот

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может использоваться в устройствах вычислительной и измерительной техники. Цель изобрет енияпопучение последовательности фик- . сированных значений расстроек, не зависящих от центральной частоты диапазона. Блок 2 установки частоты устанавливает число Кц, определяющее значение центТэал ьной выходной частоты . Пересылку числа в двоичном коде в накапливающий сумматор 5 через йеремножитель П 4 обеспечивает регистр 3 частоты. П 4 Ф со 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН ())4 н 03 В 19 00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬП ИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCH0MV СВИДЕТЕЛЬСТВУ (21) 3742909/24-Ю9 (22) 16.05 .84 (46) 07,02.86. Бюл, Р 5 (71) Таганрогский радиотехнический институт им.В.Д.Калмыкова (72) В.Ю.Капустин, В.С.Григорьев и П.И,Молчанов (53) 621.373.42 (088.8) (56) Патент США 11 3831015, Н кл- 235/197, кл, G 06 F 15/34, 1974.

Гнатек Ю.P. Справочник по цифроаналоговым и аналого-цифровым преобр азователям. М.: Радио и связь, 1982, с. 255-259 °

„„SU, » 121 198 А (54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ (57) Изобретение относится к радиотехнике и может использоваться в устройствах вычислительной и измерительной техники. Цель изобретенияполучение последовательности фиксированных значений расстроек, не зависящих от центральной частоты диапазона. Блок 2 установки частоты устанавливает число К, определяющее значение центральной выходной частоты . Пересылку числа К„ в двоичном коде в накапливающий сумма тор 5 через неремножитель П 4 обеспечивает регистр 3 частоты. П 4 обеспечивает умножение числа Кц на код величины р асстр ойки,, хр анящейся в блоке памяти (БП) 10 „Разрядность П 4 и БП )0 определяется требуемой точностью установки расстройки, а также центральной частоты. Емкость БП 10 при этом зависит от кол-ва расстроек. Вычи— литель амплитуды 6 на основе данных и текущей фазы вычисляет цифровые значения модуля текущей BM плитуды, а знак амплитуды с выхода

1210198 сумматора 5 поступает непосредствен- но в цифроаналоговый преобразователь 7 и на вход счетчика 9. Счетчик 9 подсчитывает кол-во периодов синтезируемого синусоидапьного сигнала и обеспечивает смену коэф. р ас стр ой ки . Цифр о ан ало го вый пр еобразователь 7 преобразует дискретные значения амплитуды в ступенчатый аналоговый сигнал, первая гармоника которого выделяется при помощи фильтра 8 нижних частот. 1 ил.

Изо бретение относится к радиотехнике и может использоваться в устройствах вычислительной и измерительной техники, Цель изобретения — получение последовательности фиксированных значений расстроек, не зависящих от центральной частоты диапазона,.

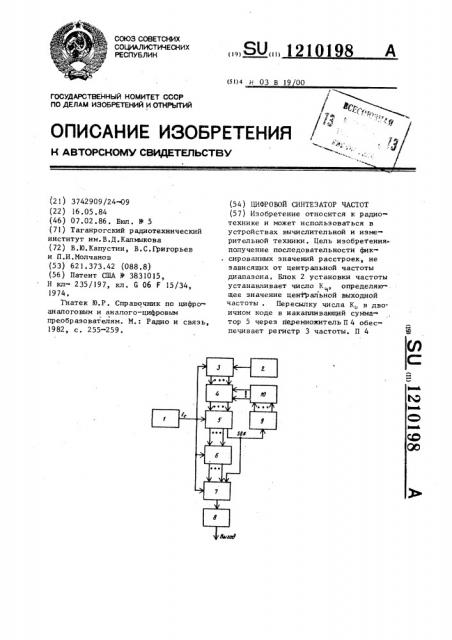

На чертеже представлена структурная схема цифрового синтезатора частот °

Цифровой синтез атор частот содержит т актовый генератор 1, блок

2 установки частоты, регистр 3 частоты, перемножитель 4 кодов, накапливающий сумматор 5, вычислитель 6 амплитуды, цифроаналоговый преобразователь (ЦАП) 7, фильтр нижних частот (ФНЧ) 8, счетчик 9, блок 10 памяти °

Цифровой синтезатор частот работает следующим образом °

Блоком 2 установки частоты устанавливается число К, определяющее значение центральной выходной частоты диапазона f . Регистр 3 с так1 товой частотой f обеспечивает переТ сыпку числа К в двоичном коде в н акаппи в ающий сумматор 5 через пер емножитель 4. Перемножитель 4 может быть выполнен на основе или матричных умножителей, или постоянных запоминающих устройств и обеспечивает умножение числа К на код вели-

Ц чины расстройки М, хранящихся в блоке 10 памяти. Разрядный и знаковый SGN выходы накапливающего сумматора 5 содержат информацию о фазе.синусоидального сигнала в пределах одного периода, Приращение фазы (в радианах . на каждом такте тактовой частоты определяется выражением

2ЯКцИ /2, где 2 - емкость накаплиН М .) вающего сумматора 5, причем 1 «а К

H 2 ", следовательно, минимальное приращение фазы определяется только значением и и равно 7/3

Вычислитель 6 амплитуды на основе введенных данных и текущей фазы вычисляет на каждом такте частоты цифровые значения моцуля текущей амплитуды. Знак амплитуды с выхода

ВЬЮ накапливающего сумматора 5 поступает непосредственно в,AII 7 и на вход счетчика 9 °

ЦАП 7 преобразовывает дискретные значения амплитуды в ступенчатый

20 аналоговый сигнал, первая гармоника которого выделяется при помощи ФНЧ 8.

На выходе цифр ово го синтез атор а частот получается множество различных последовательностей частот причем каждая из частот отдельно рассматриваемой последовательности определяется произведением центральной частоты, задаваемой блоком 2 уст ановки частоты „ 4, т Кц/2 на коэффициент расстройки М

* Р.1

-М ы 1, 1 Р

При этом количество частот fö и может достигатьвеличиныМ = 2/4, Д. при условии, что высшие частоты формируются не менее, чем четырьма отсчетами на период, В значительно меньших пределах может быть коли1210198 4

Формула из о бр ет ения

Разрядность перемножителя 4, блока 10. памяти определяется требуемой точностью установки расстройки,. а также центральной частоты, Емкость блока 10 памяти при этом зависит лишь от количества рас —. строек.

Сост авит ел ь Ю. Ко в ал ев

Редактор Р,Цицика Техред М.Пароцай Корректор И.Эрдейи

Заказ 530/58 Тираж 818 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП "Патент", r,Óæãîðoä, ул. Проектная, 4 чество P коэффициентов расстройки °

Таким образом, на выходе заявленного устройства можно получить множество F последовательностей в произвольном временном сочетании, каждую длиной P частот, причем

FP>N .

Счетчик 9 подсчитывает количество периодов синтезируемого синусоидаль— ного сигнала и обеспечивает смену коэффициентам расстройки, Блок 10 памяти выполняет функции хранения заданной последовательности необходимых значений расстроек и регенерацию этой последовательности по сигналам управления, поступающих со старших п разрядов счетчика 9.

Количество коэффициентов расстроек Р при этом равно 2 . Смена коэффиh циента расстройки происходит авто е-р матически после отработки 2 периодов выходного синусоидального сигнала, независимо от величины рас" стройки, здесь 2 - полная разрядность счетчика 9 (P>n) .

Цифровой синтезатор частот, содержащий последовательно соединенные блок установки частоты и регистр частоты, последовательно соединенные накапливающий сумматор, вычислитель амплитуды, цифроаналоговый преобразователь и фильтр нижних частот, последовательно соединенные счетчик и .блок памяти, а также тактовый генератор, при этом управляюиже входы регистра частоты, накапливающего сумматора, вычислителя амплитуды и цифроаналогового преобразователя объединены и подключены к выходу тактового генератора, а выход старшего разряда накапливающего сумматора соединен со знаковым . входом цифроаналогового преобразователя,отличающийся тем, что, с целью получения .после довательности фиксированных значений расстроек, не зависящих от централь»

25 ной частоты, между поразрядными выходами регистра частоты и соответствующими поразрядными вхопами накапливающего сумматора введен перемножитель кодов, вторая группа входов которого подключена к соот

О ветствующим поразрядным выходам блока памяти, а вход счетчика соединен с выходом старшего разряда накапливающего сумматора.