Приоритетное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и предназначено для применения в устройствах , выполняющих функцию прерьгоания. Цель изобретения - сокращение объема оборудования. Приоритетное устройство содержит два регистра , четыре элемента И, элемент НЕ и четыре элемента ИЛИ. 1 ил.

COOS СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (Я) 4 6 06 F 9/46.(21) 3727713/24-24 (22) 06.04.84 (46) 15.02,86. Вюл, У 6 (72) В,И.Сбытов, В.М.Смирнов, А.Ф.Такса и Т.В.Соина (53) 681.325 (088.8) (56) Авторское свидетельство СССР

Р 991428, кл. G 06 F 9/46, 1983.

Авторское свидетельство СССР

М 666543, кл. G 06 F 9/46, 1979.,.SU„, 1211727 A (54) ПРИОРИТЕТНОЕ УСТРОЙСТВО (57) Изобретение относится к автоматике и вычислительной технике и предназначено для применения в устройствах, выполняющих функцию прерывания. Цель изобретения — сокра" щение объема оборудования. Приоритетное устройство содерлжт два регистра, четыре элемента И, элемент

НЕ и четыре элемента ИЛИ. 1 ил.

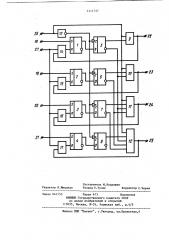

2 этого элемента поступает единичный уровень с прямого выхода триггера 5.

Одновременно импульс с выхода 22 через элемент ИЛИ 14 поступает на вход сброса триггера 1 и устанавливает этот триггер в нулевое состояние передним фронтом. С прямого выхода триггера I нулевой уровень поступает на вход триггера 5, и по заднему фронту импульса, установившего передним фронтом триггер 1 в нулевое состояние, триггер 5 устанавливается также в нулевое состояние, а единичный уровень с его инверсного выхода поступает на третьи входы элементов И 10, ll 12. Далее синхроимпульсы последовательно проходят через элементы И 10 на выход 23, на элемент И Il, на выход 24 на выход 25, после чего устройство возвращается в исходное состояние.

Формула изобретения

Приоритетное устройство, содержащее два регистра, группу элементов И и группу элементов ИЛИ, причем единичный вход каждого разряда первого регистра соединен с соответствующим запросным входом устройства, каждый выход первого регистра соединен с единичным входом одноименного разряда второго регистра, прямой выход каждого разряда второго регистра соединен с пер- вым входом одноименного элемента И группы, вторые входы элементов И группы соединены с тактовым входом устройства, выходы элементов И группы являются группой выходов устройства, о т л и— ч а ю щ; е е с я тем, что, с целью сокращения объема оборудования, устройство содержит элемент НЕ, причем тактовый вход устройства через элемент HE соединен с тактовыми входаФ ми разрядов второго регистра, выход каждого элемента ИЛИ группы соединен с входом сброса одноименного разряда первого регистра, первые входы элементов ИЛИ группы соединены с входами сброса устройства, второй вход каждого элемента ИЛИ группы соединен с одноименным выходом устройства, инверсный выход каждого разряда второго регистра соединен с соответствующим входом всех последующих элементов И группы.

f 1211727

Изобретение относится к цифровой технике и может быть использова1но в блоках управления общей памятью вычислительных систем или систем сброса и регистрации информации.

Цель изобретения — сокращение объема оборудования устройства.

На чертеже представлено приоритетное устройство.

Устройство содержит триггеры 1-4 to первого -регистра, триггеры 5-8 второго регистра, элементы И 9-12, элемент НЕ 13, элементы ИЛИ 14-17, запросные входы 18-21 устройства, выходы 22-25 устройства, тактовый 15 вход 26,устройства, вход 27 сброса устройства.

Устройство работает следующим образом.

Перед началом работы устройство 2о устанавливается в исходное состояние подачей на вход 27 сброса устройства импульса единичного уровня, который через элементы ИЛИ 13-16 поступает на входы триггеров 1-4 и уста- 25 навливает их в нулевое состояние.

Нулевой уровень с прямых выходов триг. геров I 4 поступает на входы триггеров 5-8, и по заднему фронту синхроимпульса эти триггеры устанавливаются в нулевое состояние. Следовательно, на выходах 22-25 — нулевые уровни, При поступлении запросов, т.е. импульсов единичного уровня, на входы 1821 триггеры 1-4 устанавливаются в единичное состояние и с их прямых выходов на входы триггеров 5-8 поступают единичные уровни. По заднему фронту первого поступившего после этого на вход 26 синхроимпульса, который через инвертор 13 поступает также на тактовые входы триггеров

5-8, триггеры 5-8 устанавливаются в единичное состояние а прямых выхо 45 дах триггеров, а следовательно, и на вторых входах элементов И 9-12 единичные уровни, а на инверсных— нулевые. Нулевой уровень с инверсного выхода триггера 5 высшего по приоритету канала поступает на третьи входы входовых элементов И 1012 более низких по приоритету каналов и закрывает их. Следующий синхроимпульс, поступивший на вход 26 проходит через элемент И 9 на выход 22, так как на второй вход! 211727

2D

Составитель М.Кудряшев

Техред Т.Тулик Корректор С.Черни

Редактор Н.йвыдкая

Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

ll3035, Москва, Ж-35, Раушская наб., д.4/5

Заказ 641/53

Филиал ППП "Патент", r.Óìãoðîä, ул.Проектная,4