Микропроцессор

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) SU(ii) (58 4 С 06 F 15 0

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPGHOIVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3770762/24-24 (22) 09.07.84 (46) 15.02.86 ° Бюл. 9 6 (71) Киевский научно-исследовательский и конструкторский институт периферийного оборудования (72) В.Ф.Каплун, Ю.M.Омельянчук, Н.Д.Панков и Д.Б.Сафьяновский (53) 681.32(088.8) (56) Прангишвили И.В. Микропроцессоры и микроЭВМ. М.: Энергия, 1978, с.70.

Березенко А.И. и др. Микропроцессорные комплекты повышенного быстродействия. M. Радио и связь, 1981, с. 30. (54)(57) МИКРОПРОЦЕССОР, содержащий арифметико-логическое устройство, регистр результата, блок памяти и первый мультиплексор, причем выход

i-го разряда регистра результата подключен к входам < -ro разряда первого информационного входа арифметико-логического устройства и первого информационного входа первого мультиплексора (i =1, К, где К разрядность арифметико-логического устройства), выход которого подключен к второму информационному входу арифметико-логического устройства, выход i --ro разряда которого подключен к входам 1 -го разряда информационных входов регистра результата и блока памяти, выход i --го разряда которого подключен к входу i-ro разряда второго информационного входа первого мультиплексора, вход кода операции микропроцессора подключен к входу признака операции арифметико-логического устройства и к входу записи-считывания блока памяти, адресный вход блока памяти подключен к адресному входу микропроцессора, вход записи результата входа кода операции микропроцессора подключен к синхровходу регистра результата, отличающийся тем, что, с целью повышения бысТродействия, в него дополнительно введены с второго по М= К+1 мультиплексоры -(где N — разрядность информационного слова процессора, N -= -К и где и — количество разрядов, необрабатываемых в АЛУ), регистр адреса операнда и регистр первого операнда, причем вход i -го разряда j -го информационного входа устройства подключен к входу i -го разряда (j+2)-.ro информационного входа первого мультиплексора (j =1 М, где

М вЂ” количество информационных входов микропроцессора), управляющий вход которого подключен к первому выходу регистра адреса операнда, синхровход и информационный вход которого подключены соответственно к входу записи адреса операнда входа кода операции микропроцессора и к входу адреса операнда микропроцессора, первый и второй информационные входы tn -го мультиплексора (щ=2, Н-К+1) подключены к выходам (в+К-1)ro разряда соответственно регистра результата и блока памяти, (j +2)-й информационный вход п1-ro мультиплексора подключен к входу (m+k-1 )го разряда j -ro информационного входа микропроцессора, выход в-го мультиплексора подключен к входу (m+K-1)-го разряда информационных входов регистра результата и блока памяти, выход регистра результата подключен к-информационному выходу микропроцессора, управляющий вход

in-го мультиплексора подключен к rn --му выходу регистра адреса операнда, выход i -го разряда регистра первого операнда подключен к входу -ra разряда (М+3)-ro информационного входа первого мультиплексора. (М+

+3)-й информационный вход щ-го муль-, типлексора подключен к выходу (Fn+

+ -1)-го разряда регистра первого операнда, информационный вход и синхровход которого подключены соответственно к входу первого операнда .и входу записи первого операнда входа кода операции микропроцессора.

М<3 2

Изобретение относится к вычислительной технике и может быть использовано в устройствах оперативного преобразования информации для редактирования (преобразования) информации.

Целью изобретения является повышение быстродействия.

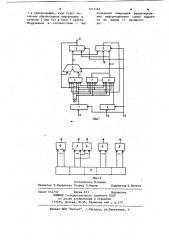

На фиг.1 изображена функциональная схема микропроцессора", на фиг.2схема варианта объединения мультиплексоров в группы.

Микропроцессор содержит арифметико-логическое устройство 1, регистр

2 результата, блок 3 памяти, первый мультиплексор 4, мультиплексоры 5, регистр 6 адреса операнда, регистр

7 первого операнда, входы.: 8 — кода операции, 9 — информационный, 10— адресный, 11 — первого операнда, 12 — адреса операнда микропроцессора, выход 13 результата микропроцессора.

Регистр 6 управляет коммутацией информации, причем управление мультиплексорами осуществляется независимо, т.е. на их выходах могут формироваться сигналы с различных информационных направлений. Для этого регистр 6 условно разделен на и -К+1

И -разрядных групп (по числу мультиплексоров 5 и с учетом первого мультиплексора 4). Разрядность групп h определяется из условия где @+3 — число информационных входов мультиплексоров, М. — количество входов 9.

С целью уменьшения разрядности регистра 6 мультиплексоры 5 могут быть для конкретных реализаций процессора объединены в группы, каж5

44 дая из которых управляется соответствующими выходами регистра 6 (фиг.2).

По информационным входам 9 с раз-, личных направлений на входы мультиплексоров 4 и 5 поступают информационные слова, предназначенные для редактирования. Эти информационные слова в общем случае состоят из двух частей: части, предназначенной для обработки в арифметико-логическом устройстве 1, и части, которая не подвергается обработке в арифметикологическом блоке 1. Редактирование информации заключается при этом в изменении как первой, так и второй частей информационных слов в соответствии с конкретным алгоритмом редактирования.

Процессор работает следующим образом.

Перед началом операции редактирования управляющим сигналом со входа

8 в регистр 7 заносится информация (константа), которую предполагают использовать в процессе редактирования, а в регистр 6 — коды, управляющие мультиплексорами 4 и 5. Эти коды позволяют подключить один из

her+3 информационных входов мультиплексоров на их выходы. В результате на выходах мультиплексоров формируется новое информационное слово (например, на выходы мультиплексора

4 поступает информация от K младших разрядов регистра 2, на выходы первого и второго мультиплексоров 5 информация с К +1 и k+2 разрядов регистра 7 и т.д. в соответствии с программой редактирования).

Затем по входу 8 поступают управляющие сигналы, задающие операцию в арифметико-логическом устройстве

Pva. Я

Составитель M.Ñèëèí

Редактор Т.Парфенова Техред Л.Микеш Корректор В.Бутяга

Закаэ 642/54 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, K-35, Раушская наб., д.4/5

Филиал ППП "Патент", г..Ужгород, ул.Проектная, 4

1 и определяющие, куда будет записана обработанная информация: в регистр 2 . или (и) в блок 3 памяти. .Полученное в соответствии с вы1211745 4 Ъ полняемой операцией редактирования информационное слово выдает-. ся на выход 13 процессо ра.