Многоканальное устройство для приема сигналов

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСХИХ

СОЦИАЛИСТИЧЕСН ИХ

РЕСПУБЛИН (51)4 G 08 С 19/28 (21) 3773174/24-24 (22) 19. 07. 84 (46) 15. 02. 86. Бюл, Р 6 (71) Ордена Ленина институт кибернетики им. В.Н.Глушкова (72) Л.А.Гнатив, С.Н.Жаровский, А.M.Лучук и Я.Н.Николайчук (53) 621.398(088.8) (56) Харкевич А.А. Борьба с помехами. M. Наука, 1965, с. 99-101, 117-118.

Грибанов Ю.И. и др. Автоматические цифровые корреляторы. М.: Энергия, 1971, с. 123-126. (54)(57) 1. МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ, содержащее синхронизатор, выход которого соединен с управляющими входами преобразователя аналог-код и формирователя опорных сигналов, в каждом информационном канале накопителя, выходы которых соединены с соответствующими входами решающего блока, выход которого является выходом устройства, информационный вход преобразователя аналог-код является входом устройства, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия устройства, в него введены в каждый информационный канал элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и фор-. мирователь последовательности нечетных чисел, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с информационным входом формирователя последовательности нечетных чисел, выход которого соединен с входом накопителя, „.Я0„„1211785 A выход синхронизатора соединен с управляющими входами формирователей последовательности нечетных чисел информационных каналов, выход преобразователя аналог-код соединен с объединенными первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ информационных каналов, выходы формирователя опорных сигналов соединены с соответствующими вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ информационных каналов, 2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что решающий блок содержит компаратор, группы компараторов, группы коммутаторов и дешифратор, выходы:компараторов каждой группы соединены с первыми входами соответствующих коммутаторов одноименной группы и с соответствующими входами дешифратора, выходы каждой пары коммутаторов предыдущей группы соединены соответственно с первым и вторым входом компаратора последующей группы компараторов и вторым и третьим входами коммутатора последующей группы, выходы коммутаторов последней группы соединены с первым, вторым входами компаратора, выход которого соединен с последним входом дешифратора, пер— вый и второй входы компараторов первой группы объединены соответственно с вторым и третьим входами коммутаторов первой группы и являются входом решающего блока, выход дешифратора является выходом решающего блока.

1211785

Устройство работает следующим образом.

Процесс вычисления суммы квадратов разностей между принимаемым и опорными сигналами происходит эа

ln тактов. В начале каждого такта

40 измерения (преобразования принимаемого сигнала в код) на выходе синхронизатора 2 формируется короткий импульс, по переднему фронту которого происходит предустановка всех триггеров (не показаны) формирователя 5 последовательности нечетных чисел в единичное состояние, а по заднему фронту - запуск преобразователя 1 аналог-код и формирователя 3 опорных сигналов. Одновременно с этим на втором выходе синхронизатора 2 вырабатывается последовательность импульсов, которая действует на всем протяжении такта измерения, тактируя работу преобразователя 1 аналог-код, формирователя 3 опорных сигналов и элементов 4 — 4 > (последняя связь не показана), 45

Изобретение относится к цифровой обработке информационных модулированных сигналов в реальном масштабе времени для определения их параметров и может быть использовано в системах связи и передачи данных.

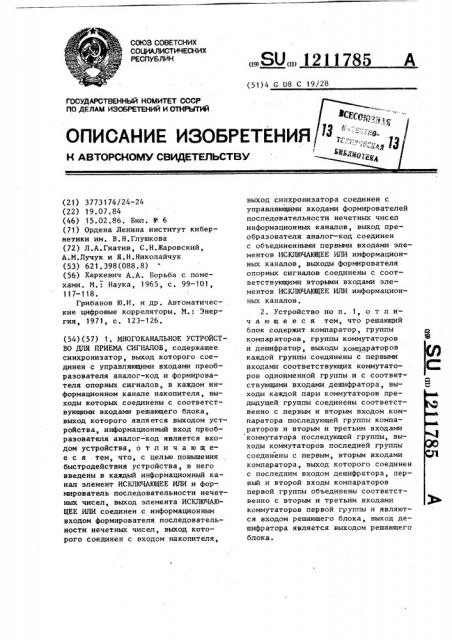

На фиг. 1 представлена блок-схема многоканального устройства для приема сигналов на фиг. 2 — формирователь последовательности нечетных чисел на фиг. 3 — синхронизатор, на фиг. 4 — формирователь опорных сигналов на фиг. 5 — решающий блок.

Устройство (фиг. 1) содержит преобразователь 1 аналог-код, синхронизатор 2, формирователь 3 опорных сигналов, элементы 4 — 4,„ ИСКЛЮЧАЮЩЕЕ ИЛИ, формирователи 5 „ — 5„ последовательности нечетных чисел, накопители 6 — 6, решающий блок 7.

Формирователь (фиг. 2) последовательности нечетных чисел содержит двоичный счетчик 8 и сумматор 9.

Синхронизатор (фиг. 3) содержит генератор 10 тактирующих импульсов и счетчик 11.

Формирователь (фиг. 4) опорных сигналов содержит генератор 12 опорных сигналов и преобразователи аналог-код 13.

Решающий блок (фиг. 5) содержит компараторы 14, коммутаторы 15 и дешифратор 16.

В процессе измерения текущего отсчета принимаемого сигнала с выхода преобразователя 1 аналог-код синхронно с тактовыми импульсами на первые входы элементов 4, - 4 поступает унитарный код (пачка импульсон) текущего отсчета принимаемого сигнала, а на вторые входы элементов 4 — 4п синхронно с тактовыми импульсами с соответствующих выходов формирователя 3 опорных сигналов поступает унитарный код текущего отсчета соответствующего опорного сигнала. При этом в каждом канале на выходе элемента 4 полуI чается унитарный код, равный абсолютной разности между абсолютными текущими значениями принимаемого и опорных сигналов.

По каждому импульсу, поступающему на вход формирователя 5 после4 довательности нечетных чисел, в нем происходит счет нечетных чисел и передача их кодов в накопитель 6„, где коды нечетных чисел складываются с ранее накопленной суммой.

Таким образом, в каждом такте измерения предлагаемый приемник обеспечивает одновременное выполнение операций получения абсолютных разностей принимаемого и опорного сигналов в элементах 4 < †. 4„, суммирование в накопителях 6 - 6 кодов нечетных чисел для получения квадратов этих разностей и суммирование полученных квадратов абсолютных разностей.

После и тактов измерений на выходах накопителей 6, — 6 получаются коды сумм квадратов абсолютных разностей между принятым и опорными сигналами. Эти коды с выходов накопителей 6, — 6„ поступают на решающее устройство 7, где опреДеляется наименьший код, по которому происходит отождествление принятого сигнала с тем из опорных (возможно переданных) сигналов, для которого этот код наименьший.

Формирователь 5; последовательности кодов нечетных чисел (фиг. 2) содержит двоичный счетчик 8 и сумч матор 9, причем выход счетчика 8 соединен с вторым входом сумматора 9;, начиная с второго разряда, а первый вход сумматора подключен к входу счетчика.

1211785

Формирователь 5 работает следующим образом.

Перед запуском приемника происходит предустановка всех триггеров счетчика 8 в единичное состояние.

При поступлении первого импульса с выхода элемента 4 в каждом кана\ ле происходит сброс всех триггеров ,счетчика 8, в нулевое состояние и занесение единицы в первый разряд сумматора 9, которая складывается с кодом нулевого состояния счетчика 8 и передается в накопитель 6„., По каждому пришедшему следующему импульсу с выхода счетчика 8, снимается двоичный код, который посту-. пает на второй вход сумматора 9 на, ю чиная с второго разряда, что обеспечивает операцию умножения кода на два. Одновременно с поступлением кода на вгорой вход сумматора на пер. вый вход (первый разряд) заносится единица. При этом по каждому импульсу,,пришедшему на вход счетчика 8

1 и на первый вход сумматора 9 на

19 выходе сумматора 9,; получается код нечетного числа, который складывается в накопителе 6, с ранее, накопленными кодами последовательностей нечетных чисел.

Накопитель 6; выполнен в виде накапливающего сумматора.

Синхронизатор 2 (фиг. 3) содержит последовательно соединенные генератор 10 тактирующих импульсов и счетчик 11 импульсов.

Синхронизатор работает следующим образом.

Генератор 10 вырабатывает последовательность тактовых импульсов. Эти импульсы поступают на вход счетчика 11, который делит частоту импульсов генератора на коэффициент, равный числу уровней квантования по амплитуде. Сигнал на выходе счетчика 11 соответствует интервалу измерения.

Формирователь 3 опорных сигналов (фиг. 4) содержит генератор 12 опорных сигналов и преобразователи 134

13 аналог-код, входы которых подключены к соответствующим выходам генератора 12 опорных сигналов, а выходы являются выходами формирователя 3 опорных сигналов. Вход генератора 12 опорных сигналов подключен к выходу счетчика 11 синхронизатора 2.

Генератор 12 опорных сигналов (фиг. 4) запускается задним фронтом короткого импульса, который форми10 руеч счетчик 11 (фиг, 3). Опорные сигналы с выхода генератора 12 поступают на преобразователи 13< -13„ аналог-код, которые преобразуют аналоговые опорные сигналы в дискретные сигналы, представленные в унитарном коде.

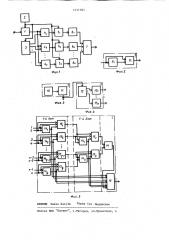

Решающий блок (фиг ° 5) содержит

К (К = op п -1, где rt — число каналов) последовательно соединенных

20 блоков, содержащих компараторы 14 и коммутаторы 15. В каждом 4ом блоке число компараторов и коммутаторов с точностью до целого числа равно n/2 .

25 Решающий блок работает следующим образом.

Коды накопителей 6 — б„ поступают на компараторы 14 < — 14„ и ком-. мутаторы 15i — 15„,, которые проЗ0 пускают код того накопителя, который в результате попарного сравнения оказался меньшим. Выходы компараторов каждого блока и компаратора 14 последнего блока поступают на вход дешифратора 16 и представляют собой

35 закодированный номер накопителя, выходной код которого наименьший.

На выходе дешифратора 16 получается возбужденное состояние шины, номер которой соответствует отождествляемому с принимаемым опорному сигналу.

Таким образом, предложенное уст-

45 ройство обладает меньшим объемом оборудования и большим быстродействием. По сравнению с прототипом оно позволяет обрабатывать более высокочастотные принимаемые сигналы с одновременным выполнением опера50 ции преобразования и обработки.

1211785

Фие.1

Фий,2 фиг. 4

n-f л

Фиг. 5

ВНИИПИ Заказ 644/56 ТиРаж 516 Подписное

1\ fI

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4