Устройство для обучения основам вычислительной техники

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИ(ТИЧЕСКИХ

РЕСПУБЛИК

09) (11) (51)4 С 09 В 19/02 (21) 3767708/24-24 (22) 13.07.84 (46) 15.02.86. Бюл. Ф 6 (71) Курский политехнический институт (72) В.В. Подобед, Г.Д. Деведзи и М.Б. Фельдштейн (53) 68 1.3.071(088.8) (56) Устройство для изучения построения логических схем на микросхемах серии 155: Паспорт (обьединенный)

УМ11ПС, СКБ МВССО СССР, 1975, с. 38.

Цифровые вычислительные машины.

Под ред. Г.Н. Соловьева. М.: Атомиздат, 1977, с. 128-134. (54)(57) УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ

ОСНОВАМ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ, содержащее пульт обучаемого, первый регистр и генераторы тактовых и одиночных импульсов, о т л и ч а ю— щ е е с я тем, что, с целью расширения дидактических возможностей устройства, в него введены блок задания разрядности кодов, последовательно включенные переключатель, блок синхронизации, счетчик, дешифратор и первый коммутатор, выход которого .соединен с первым входом пульта обучаемого и последовательно соединенные второй регистр и второй коммутатор, выход которого подключен ко второму входу пульта обучаемого, третий и четвертый входы которого соединены соответственно с выходом блока синхронизации и выходом блока задания разрядности кодов, подключенным к вторым входам первого и второго коммутаторов и блока синхронизации, д третий, четвертый и пятый входы которого соединены соответственно с выходами генераторов тактовых и одиночных импульсов и выходом дешифра- С тора, подключенным к третьему входу второго коммутатора, третий вход .первого коммутатора соединен с выходом первого регистра.

1211798

Изобретение относится к автоматике и вычислительной технике, в частности к техническим средствам обучения, а именно к учебным установкам, предназначенным для сборки и исследования в различных режимах последовательностных преобразователей (ко нечных автоматов с памятью), используемых в качестве узлов при построении средств вычислительной техники и дискретной автоматики.

Целью изобретения является расширение дидактических возможностей устройства при сокращении времени подготовки установки к экспериментальным исследованиям последовательностных преобразователей.

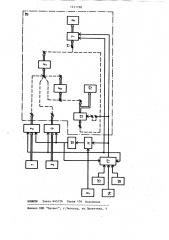

На чертеже изображена структурная схема устройства для обучения основам вычислительной техники.

Она содержит регистр 1, коммутатор 2, регистр 3, коммутатор 4, набор логических элементов 5, дешифратор 6, сдвигающий регистр 7, блок 8 индикации, блок 9 задания разрядности кодов, дешифратор 10, счетчик 11, набор триггеров 12, набор элементов 13 индикации, переключатель 14 режимов работы, генератор 15 тактовых импульсов, генератор 16 одиночных импульсов, блок 17 синхронизации.

Дешифратор 6, элементы 5 и 13, регистр 7, блок 8 и триггеры 12 объединены в пульт 18 обучаемого.

Группы клемм пульта 18 образуют коммутационную панель устройства.

Блок 17 выполнен в виде схемы стартстопного управления, синтез которой может осуществляться методами синтеза цифровых автоматов и содержит два мультиплексора, RS-триггер и конъюнктор (не показаны), причем выходом схемы синхронизации является выход первого мультиплексора, первый информационный вход которого соединен с выходом конъюнктора, первый вход которого подключен к выходу

RS-триггера, R-вход которого соединен с выходом второго мультиплексора, à S-вход, связанный с вторым информационным входом первого мультиплексора, является четвертым входом схемы синхронизации, первый вход которой образован информационными входами второго мультиплексора, пятый - управляющим входом последнего, второй — вторым входом конъюнктора, соединенным с третьим информационным входом первого мультиплексора, а третий — управляющим входом .послед него.

Работа на предлагаемом устройстве осуществляется следующим образом.

Обучаемому необходимо собрать схему исследуемого последовательностного преобразователя используя элементы 5, триггеры 12, элементы 13 индикации, дешифратор 6. Далее необходимо выход исследуемого после" довательностного преобразователя подключить к входу регистра 7, вход его соединить с выходами коммутаторов

2 и 4, а синхровход — с выходом схемы синхронизации блока 1.7. Затем, установив с помощью блока 9 разрядность кода символа и набрав на регистрах 1 и 3 две входные последовательности символов, переключателем 14 следует задать один иэ трех режимов работы: шаговый, однократный или циклический.

В шаговом режиме устройство работает следующим образом.

Два параллельных и-разрядных двоичных кода, набранные на регистрах и 3, поступают на информационные входы коммутаторов 2 и 4. Счетчик

11, задающий номер текущего символа, и блок 9, задающий разрядность кода символа, определяют пару k-разрядных символов, пропускаемых коммутаторами 2 и 4 на вход последовательностного преобразователя (вход набора логических элементов 5). Эта пара символов с учетом текущего состояния последовательностного преобразователя, определяемого состоянием триггеров 12 и индицируемого элементами 13, преобразуются в выходной k-разрядный символ, который с выхода последовательностного преобразователя (выхоц элементов 5) подается на вход регистра 7. При нажатии кнопки"Пуск" генератора 16 схема синхронизации блока 17 под воздействием сигнала шагового режима, поступающего на ее вход с выхода переключателя 14, вырабатывает одиночный синхроимпульс, по которому в регистре 7 осуществляется

k-разрядный сдвиг с одновременным приемом полученного на выходе последовательностного преобразователя символа. Кроме того, одиночный синхроимпульс, поступая на синхровход памяти последовательностного преобразователя (набор триггеров 12), иэме-, 3 1211798 4 няет текущее состояние последней в под воздействием сигнала. цикличессоответствии с сигналами возбуждения, кого режима от переключателя 14 схеснимаемыми с выходов соответствующих ма синхронизации блока .17 постоянно логических элементов 5. Этим же оди- пропускает на выход синхроимпульса ночным синхроимпульсом увеличивается 5 генератора 15. Счетчик. 11 при этом на одну единицу состояние счетчика. реализует счет по модулю m что обесФ

11, что обеспечивает прохождение печивается сигналом разрядности кода на выходы коммутаторов 2 и 3 следую- символа, поступающим от блока 9 на щей пары k-разрядных символов. Тем его управляющий вход. В этом режиме самым оказывается подготовленным 1О две m-символьные входные последоваследующий шаг работы последователь- тельности символов, набранные на ностного преобразователя ° регистрах 1 и 3, циклически (многоТ аким образом, работа установки кратно) преобразуются последовательв шаговом режиме заключается в костным преобразователем в m-симm-кратном (m= †) нажатии кнопки. и вольную выходную последовательность символов, регистрируемую в данном

"П ск"

" у генератора 16, в результате случае с помощью осциллографа, подчего две m-символьные входные пос- ключаемого на выход последовательледовательности символов, набранные ностного преобразователя. Кроме тона регистрах 1 и 3, оказываются преоб- 20 го, в данном режиме подключением осразованными последовательностным пре- циллографа к различным внутренним образователем в ш символьную выход- точкам схемы последовательностного ную последовательность, зафиксирован- преобразователя осуществляется набную регистром 7 и индицируемую бло- людение динамики работы исследуемоком 8. 25 го преобразователя.

Работа устройства в о н к ат однократном Предлагаемое устройство включает режиме отличается от аб р оты в шаго- постоянно собранную вспомогательную вом режиме тем, что по воз ействие д зд йствием схему управления, позволяющую проиэсигнала однократного режима с пе ер р водить исследование последовательключателем 14 схема синх ониза ии ронизации ЗО ностных преобразователей в трех реблока 17 после разового нажатия

I I 1! жимах: шаговом, однократном и цикликнопки Пуск" генератора 16 пропусческом, причем переход от одного рекает на выход пачку из m-синхроим- жима к другому. осуществляется проспульсов, формируемых генератором 15. той установкой переключателя режиВыделение схемой синхронизации бло- мов работы в соответствующее полока 17 m-синхроимпульсов генератора жение В жение. результате исключаются затраты времени обучаемого на сборку

15 осуществляется при наличии обратной связи с выхода дешифратора 10 вспомогательной схемы управления. на вход схемы синхронизации бло- Кроме того, устройство позволяет ка 17. В результате воздействия

° 40 проводить исследование сложных схем

m-синхроимпульсов на память после одо- последовательностных преобразоватевательностного преобразователя (на- леи за счет того, что "функциональбор триггеров 12), регист 7 счетчик р р четчик ные ресурсы (т.е. элементы набоII

11 две m-символьные в ходные последо- ров логических элементов и триггевательности символов, набранные на 45 ров) не расходуются на сборку вспорегистрах 1 и 3, преобразуются после- могательной схемы управления. довательностным преобразователем в И спользование в устройстве второm-символьную выхо н после д ую едователь- ro канала задания входной последованость, фиксируемую егист ом р ую р ром 7 и ин- .;тельности символов позволяет исследодицируемую блоком. 8., вать такие последовательностные

Работа устройства в и ц клическом преобразователи, на вход которых тре50 режиме отличается от аб р оты в шаго- буется одновременно подавать две вом и однократном еж р имах тем, что входные последовательности символов.

1211798

SHHHHH Заказ 645/56 Тираж 456 Подписное филиал ППП "Патент", г.Ужгород, ул.Проектная, 4