Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

СО)ОЭ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) (д1)с) G 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTQPCHOl95f СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 3771748/24-24 (22) 18.07.84 (46) 15.02.86. Бюл. У 6 (72) В.Н. Горшков, С.О. Малецкий, А.А. Соколов и В.Н. Дерунов .(53) 68!.327(088.8) (56) Авторское свидетельство СССР

N - 928423, кл. G 11 С 29/ОС, 1982.

Авторское свидетельство СССР

У 970478, кл. G ll С 29/00, 1982. (54) (57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С

САМОКОНТРОЛЕМ, содержащее накопитель, блок выбора адреса, регистры, блоки сравнения, блок управления и первую группу. элементов И, причем адресные входы накопителя соединены с выходами блока выбора адреса, выходы первого регистра подключены к одним иэ входов блоков сравнения, другие входы которых соединены с выходами первой группы второго регистра, выходы второй группы которого подключены к первым вход!м элементов И первой группы, вторые входы которых подключены к первому выходу блока управления, выходы второго регистра являются информационными выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены коммутаторы, группы сумматоров по модулю два, триггеры, третий регистр, вторая и третья группы элементов И, группа элементов ИЛИ, элементы ИЛИ и элемент И, причем выходы сумматоров по модулю два первой группы соединены с одними из входов первого коммутатора, управляющие входы которого и управляющие входы накопителя подключены к выходам первого триггера, вьгходы первого коммутатора соединены с одними из входов второго коммутатора, другие входы которого подключены к вьгходам третьей группы второго регистра, а выходы — к одним из входов первого регистра, другие входы которого соединены с выходами третьего коммутатора, входы первой группы которого подключены к выходам первой и второй групп второго регистра, выходы первой группы которого соединены с входами сумматоров по модулю два второй группы, входы четвертого коммутатора подключены к выходам первого регистра, а выходы — к информационным входам накопителя, одни из вьгходов которого соединены с входами третьего регистра и первыми входами элементов И второй группы, выходы которых подключены к первым входам элементов ИЛИ группы, вторые входы которых соединены с выхо— дами элементов И первой группы, а третьи входы — с выходами элементов И третьей группы, первые входы которьж подключены к выходам третьеFo регистра, а вторые входы соединены с выходами сумматоров по модулю два второй группы и входами первого элемента ИЛИ, выход которого подключен к первому входу элемента И, второй вход которого соединен с прямым выходом второго триггера, инверсный выход которого подключен к третьим входам элементов И первой группы, а входы соединены с другими выходами накопителя, входы второго элемента ИЛИ и другие входы первого коммутатора и входы второй группы .третьего коммутатора подключены к выходам блоков сравнения, первый и

12; -181 >..:чить>ванин. второй управляющие входы второго и коммутатора соединены соответс ненно с в то рым выходом блока уп р авле н ия. с третьим входом блока управле>1ия и первым управляющим входом третьего коммутатора, второй и третий входы которого подключены соответственно к четвертому и пятому выходам блока управления, ще стой и седьмой выхс ды котсрого соединены с управляющими входами четвертого коммутатора, а восьмой и девятый выходы — соответственно с вторыми входами элементов И второй группы и третьими входами элементов И третьей группы, вхсды первого

Изобретение относится к вычислительной технике, в частностк1 к запоминающим устройствам, в которьгх используется избыточное кодирование данных .

Целью изобретения является повы-. шение быстродействия устройства.

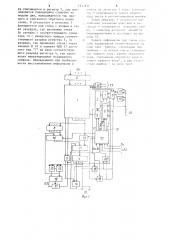

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 — функциональная схема наиболее предпочтительного варианта выполнения блока управления. >

Устройство содержит (фиг, 1, накопитель 1, блок 2 выбора адреса, регистры 3-5 с первого по третий, коммутаторы 6-9 с первого по четвертый, первый 10 и второй 11 триггеры, первую 12 и вторую 13 групйы су>аматоров по модулю два, группы элемен:— тов И 14-16 с первой по третью, группу элементов ИЛИ 17, блоки 18 сравнения, первый 19 и второй 20 элементы ИЛИ, элемент И 21, блок 22 управления. На фиг. 1 обозначены управляющие 23 и 24, информационные 25 и адресные 26 входы устройс.ва, выходь:

27-31 блока 22 управления и информационные выходы 32 устройства.

Блок 22 управления содержит (фиг. 2) элемент НЕ 33, элементы

И 34-39, элементы 40-42 задержки, элементы ИЛИ 43-46, триггер 47, элементы 48-51 задержки.

Предлагаемое устройство работает следующим образом. триггера, первый и B To>>oil -:.-,Кскц;- I>J.Oка управления яв.",яются сд 1,>k:è из управляющих входов у. тройства, ;ругим управляющим входом кс тс>1..:>го яв— ляется третий вход блока yli:.ан.->с- >ия, входы которого с че-.вер.>.О пс щес—

Той ПОДКЛЮЧЕНЬ> СООТBÅ Г Т:>ЕН К выходу злемен ",à И, < ii;-.»i:,". О, y выходу второг О три.-. ер,-:,, к выходу в тoooг О ".. темен а И 1., >>но†ды сумм>а те>ров цо модуля> 11111> первой группы и входы треTI,OA группы третьего ко.-гнут,что->а .1в— ляются информационным>: вк;>11;11- и ус т ройс". На, аПИСЬ I". С ИТЫВ аНИЕ II IIIIvl? МОЖНО

ПРОИЗВ О, >ИТЬ С ПОМОШЬ>О Д >УХ СПОСОООВ ко> ирОВания 1>: личак»аихс я :Р11:тО при первом "пс собе за1>ис„производится за несколько .-актов, а считывани1 — за Оди11 такт, вс в гором спосос е данные считываются Ia не> колько

1 актов B зккписывак>тся з>1 О,. ин 1 акт .

Способ кодирования оц,)Eцечяется

)О гyòåì занесения кода "0" или "1" в

I три1 гер 10, фиг. 1, при за 1си;Iан— нык или содержимым триггера 11 при

Запись информации г.р» rерзо>м способе кодирования происке. ;ит с >едующим образом, >6 исходном состоянии все тр>-:ггеры и регистрь:: обнулень .Пепи га>11 ния

".ÿ фиг. 1 не показаны,. В триггер 10 с входа 23 записывается ксц: 0". ,1воичнОе кОдовОе с11ОНО Х:=, л .. - . л 1, ;В Р P — ЦЕЛОЕ ЧИСЛО I >1k IIÄ O:11>1; -, и

Х =О, I; : = YI

Гdльные 1с р; яBляютс »: . II!;:Ормс„.циОн нь>ми, записываются в регистр 3 через коммутатор 8., Из реги1 1:а 3 ""-ово врез коммутатор 9 ереписывается в накопитель 1 по заданному адресу, .>

- поступающему на вход 26,;!осле этого осуществляется контрольное считывание слова из накопи" еля 1 через элементы И 15 и элементы ИЛИ 17 в регистр 4„ Считанное слово, поступающее в регистр 4, может ст.>ичаться от исходного слова из-за ::боев и

1О

30

40

45 отказов. После контрольного считывания в регистр 4 в одном из блоков 18, например в первом, происходит поразрядное сравнение записанного и считанного слов, например, для всех

M=l, 1+Т, 1+2Т,...

Если хотя бы одна пара символов

Х записанного и считанного слова не .совпадают, то все компоненты кодового слова Х с номерами, например, M=1, 1+Т, 1+2Т,... инвертируются путем посылки единицы с выхода соответствующего блока 18 через коммутаторы 6-8 на соответствующие входы регистра 3, Совпавшие компоненты слова не инвертируются. Эта операция выполняется параллельно всеми блоками 18. После ее завершения новое кодовое слово У=(У,,...Yp), где

Ущ =0,1, сформированное в регистре 3, переписывается в накопитель 1 по тому же адресу. При наличии не более Т смежных постоянных дефектов в р-разрядной ячейке памяти накопителя ) и отсутствии случайных сбоев при записи и считывании кодовое слово У будет храниться без ошибок.

При считывании слово У из ячейки накопителя I с заданным адресом считывается через элементы И 15 и элементы ИЛИ 17 в регистр 4. Одновременно считывается код "0" в трит— гер 11. После этого при подаче управляющего сигнала на элементы И 14 по первым Т символам слова У осуществляется восстановление исходного слова. Для этого М-й контрольный символ У =(M=1-T) через соответстм вующий элемент И 14 группы, который синхронизируется сигналом блока 22 подается через элементы ИЛИ 17 на входы с номерами М, М+Т, М+2Т,... регистра 4. На элементы И 14 при этом поступает также код "1" с инверсного выхода триггера Il. Если

У =1, а это имеет место, в тех случаях, когда при записи символы слова с номерами М, М+Т, М+2Т,... были инвертированы, то символы считанного из накопителя 1 слова У с этими же номерами повторно инвертируются.

Таким образом, в результате выполнения вьппе указанных инверсий для всех M=),2...Т в регистре 4 оказывается исходное слово, последние k симмолов которого являются информацион1 ными и направляются .на рыходы 32 устройства.

Запись информации при таком способе кодирования осуществляется за два такта (запись и считывание) при отсутствии ошибок или за три такта

,запись, считывание, запись) при наличии ошибок. Считывание производится всегда за один такт, Второй способ кодирования данных заключается в том, что перед записью слов в триггер 10 с входа 23 заносится коп "1", а триггер 11 и регистры пр i этом обнулены. Исходное слово поступает через коммутатор 8 в регистр 3. При этом на каждый М-й сумматор 12 поступают символы слова с номерами М, M+T, М+2Т,... В триг-ер 10 записывается код I . Свертка соответствующих разрядов с сумматора 12 поступает на коммутатор 6, куца подается разрешающий уровень с прямого выхода триггера 10. Через коммутатор 6 и коммутатор 7 свертка по модулю два записывается в регистр 3, а затем через коммутатор 9 записывается в накопитель 1 по адресу, поступающему на вход 26.

При считывании слово поступает на регистры 4 и 5. Одновременно считывается код "!" в триггер 1!. С выходов регистра 4 символы с номерами

М+Т, М+2Т,... поступают на соответствующие сумматоры 13, которые осуществляют свертку соответствующих разрядов. Если в результате свертки соответствующих разрядов на вью;одах всех сумматоров 13 получен код "О", то это означает, что нет опьибок в считанном слове. При этом на выходе элемента ИЛИ 19 и элемента И 21 также нулевой уровень. Считанное слово поступает на выход 32 из регистра 4. Если в результате свертки получен код "1" в каком-либо сумматоре !3, то произошла ошибка в одном из разрядов с соответствующим номером. Высокий уровень на вызсде соответствующего сумматора 13 через элемент ИЛИ )9 21, на который поступает разрешающий уровень с выхода триггера 11, поступает в блок 22, где, в свою очередь, будет сформирован сигнал на выходе 29.

По этому сигналу слово с выходов регистра 4 переписывается через коммутаторы 7 и 8 в регистр 3, а с него через коммутатор 9 — в накопитель 1 по тому же адресу, но в инверсном коде. После этого обратный код сло5 )7, :(В ва считывается в регистр >, где прсизводится поразрядное сложейие по модулю два, находившегося там пря— мого и считанного обратного кодов слова. В результате в регистре 5 формируется код слова с нулями в тex же разрядах, где произошел отказ.

По сигналу с соответствующего сумматора 13 с инверсного выхода соответствующего разряда регистра 5. (В О разряде, где произошел отказ) через элемент И 10 и элемент ИЛИ 17 поступает код "1" на вход соответствующего разряда регистра 4, где происходит инвертирование искаженного символа. Одновременно при необходимости восстановления информации в

1 ф .-;-.:.с"1 к-;с E%ü påpнст(pd. 3 (ерг:: ко." .-(ól а— тс о O T(poHэВОцнтс R «„11(иc .h пря; (о! о

c0,(а числа В pc".ГГ!I". риБ ле((ук) ячГЙку .

Т.IT(им образом, н реэуг(1 тате Вы,— i0" НГНИЯ вЂ”.,г (< ап -b!X 1т(1- (Виi(B P -— (" .i " S 0(азЫВ а l Г Я ИСXC! ET (0C 10

Н С, ; С ИМ Н О Л 0 В К 0 I 0 Р 0 1 0 1! В . Я Ю Т Г Я ин((ормационн >(ми и поступая.т на Bhr— э ч

ХОДЫ *.

3(1пись-., информа;ин пни -.яком с-.особе кОдирОВ Ения oсу(цес-Вляе-Гя лл од(lн такт p 560TH(, счит(-(Блние TlpH

::-.(Ибках †. эл четыре тек -л !Гчит((нл— ниc ;;::l ямGго,01 а, ВЗTIНГВ йбрлтноl 0 кода, счит(-,(ванне обратного кодл и

ЭВПИСЬ ПРЯ((0Г0 Ко;:a!, а ПНИ От"; — .— с". Hии 0(((R60!c эа одHH TB(cT. — а (!

211811

0rv 23

Составитель В. Гордонова

Текред Л.Микеш Корректор А. Обручар

Редактор Л. Кастран

Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 647/57 Тираж 544

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5