Динамическое запоминающее устройство

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 С 1 ) С 29/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3777504/24-24 (22) 01,08.84 (46) 15,02,86.Бюл.У 6 (72) Д.Б.Кудрявцев и С.С.Герасимов (53) 681.327 (088.8) (56) Авторское свидетельство СССР

Ф 982089, кл. G ll С 11/34, 1982.

Патент Японии 11 - 54-5659, кл. 97(7) С, опублик ° 1979. (54 ) (57) ДИНАМИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО, содержащее регистр адреса, мультиплексор, дешифратор, блок памяти, регистр данных и блок управления, причем одни из выходов регистра адреса подключены соответственно к входам дешифратора и к входам мультиплексора, управляющие входы которого соединены с первым и с вторым выходами блока управления, выходы блока памяти подключены к входам регистра данных, управляющий вход которого соединен с третьим выходом блрка управления, а выходы являются выходами устройства, о т л и ч а ю щ е е с я тем, что, с

„„SU„„1211812 целью повышения быстродействия устройства, в него введены формирователь сигналов, элемент И-НЕ и элемент ИЛИ-НЕ, выход которого подключен к входу формирователя сигналов, выход которого соединен с первым управляющим входом блока памяти, второй управляющий вход которого под-. ключен к выходу элемента И-НЕ, причем входы элемента ИЛИ-НЕ соединены с четвертым H пятым выходами блока управления, шестой и седьмой выхо ды которого подключены к входам элеме:-.та И-HE адресные входы блока памяти соединены соответственно с выходом мультиплексора и с другими выходами регистра адреса, выход дешифратора подключен к третьему управляющему входу блока памяти и первому входу блока управления, второй и третий входы и восьмой выход которого являются управляющими входами и управляющим выходом устройства, информационными входами которого являются информационные входы блока памяти, СI

« I T: Е: .,.! ) () (I 1 ; ).l l «)

) ) ) .)

-с»!

i!:..l;1! (.

) 1:- )T с-.--,, I Е °;-. ран.! ещ)я не "")-(1» -)(! ур с,„с j»-,- -, (.:iJ Г „!) =;О" „. 1;CHH. 1))о!)11 ."1)IT» .-,1 На!

IT ", l I р е тел(ной технике и:-.)0))(е . а= -. = ис тол(-Зона)7)3 (ЛЯ )0(ТРОЕНИЮ 0) Е!)З" (:ННЬIХ

3 BH0;"4èнî)I»)i)1)х cт «г)I ;,,, ."., t,. 1- а!».(це-;

КИХ ЭЛ(Е))2 :)т ЭХ Па) )и Г) I, )»сл)(кс ТО )0!)) ".

:IЕО «ХОДИ)Х(а !Ii= () И О )зн -) Е С 8 = " Н Т) и T Е!ТЕ );а Т7 ХРа 7(Я)))е!»(;I инф(0Р);)а ->i,f . н а)!« ..)и д Снс т(),ЕХ )1)1аа-IEI ù;=) .: .,»))(а),)i ) 1: ф7 К)»7, Цепь !! иа Ооре тенин я Бляе т с я Ij Ábl -

IIBH». C б!)1«т)рОЛЕ()СтН1»)11 .)) C f t 0iiC I 3<2 )

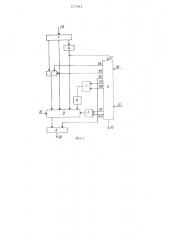

110 »)»)71" с П13ЕДСтанпа На (7)с(И К1М 01)аT. ная схема пре77дя ге (и; 0 т !IT)) 7) а *

-:1а фн1 . 2 -" ()j)THI»IT»iiQI(1 l)7,17=(Я -УЕ)„,;с)

5ЛОКа )j(ll«c»)З))Е17ИН. 1»ацСОЛЕЕ f ОГ, H0)I)HI, g 1)Т)СМЕHHb)P 11!,= C

НЯ!()))17.!«пааво-; y 1)ет ) 01.(с»((Ро 7« т но ))77»))1;») —; 7 (!»(:,г гистр l а,)7ресд.,;.>0-)! —. к)о)-ек-.;,;О . ), алло;. памяти „де))п)фпатор 4 . . с и

1T HPH ()1)ЕН))Я Р) 1-1-(С t 0.:-- :,:.I at),.с. ;; »-.мент %И-.)1) 7 „(()(1р).п)! с д,- те г(1-: 3 нало7) „«jip.мент И-н)-, c )

) те! ";. 1 и-f;!! о ;TT») 1 ),!,с .))1 «,;. )(е: т

)1 ) /, !.()Е :(:.!1,, -",7 -„"=.-,; —; ., ) 1) ЗОтКИХ;-)М;-сс!);.: Н Зс,- )!!)); .-, и НЕ 26)

7)Р 1 н !i) i )1)1. -7)!

B5)A(с7)1 I I« .1)ОК «) с) 1, «!)Ия »1 а Bb!iO lj Е 0 17 (- ц)i!T»l

I)7TiB H8 T-":T: ), !. -;1- T» T-.-) H,; — „н

1;-,, си:-на-. - 1,) 771(0 I .. I It

1 н,п, "Ыло)»ирозка ) ". на)хо;не л)О)с;)))-:l) lс )J;)

) 1 !)И !: а ..,: . l, . 1 ..".)),с, -) "..--)...;)l! !.;

).=.. Г1;- l- !ll.". /, «, Н ).t >b!

): ,),: . „„,;, gC - -„".»)ЕН вЂ” (),1 -)); .)а ) .:=!)«1!!i .. 7)i I!!(!l l ))) . t I.)—!

)С1» . :.0 и(11 tlt!1 :!а ).! )) ;-".TCC! Ннс- П «С. -1!

К;-; );-1! .;:с-,. с, l,: 1- )1

1211812

При отсутствии обращения в момент импульса 41 и включенного триггера 15, т.е, при наличии сигнала 47, формируется сигнал 48 управления мультиплексором 2 для пропускания адреса регенерации, а импульс 44 через элемент ИЛИ-НЕ 7 и формирователь 8 формирует разрешающий сигнал "СЕ" на входе блока 3.

Обращение к памяти в режиме регенерации реализуется всегда за счет того, что запуск триггера 21 осуществляется только в момент импульса 43.

Благодаря связи между выходом дешифратора 4 и входом 27 блока 5, сигнал 52 "Выбор микросхемы" поступает в блок 5, где происходит раздельное формирование сигнала раэреше. ния "СЕ" для режима обращения к памяти сигнала 55 "CEMII" и для режима регенерации "СЕРГ", т.е. сигнала 44. Это позволяет реализовать операцию обращения к блоку 3 в любой момент времени независимо от операции регенерации, эа счет чего сокращается время обращения к динамическому устройству. .В вычислительных системах, где. происходит согласование двух независимых синхронизаций, как правило, существует пассивный отрезок времени "вхождение одной синхронизации в другую", соизмеримый с периодом наибольшей частоты синхросигнала.

Для обеспечения более надежного режима обращения к блоку 3 и максимальной частоты обращения к нему в период регенерации эа такт до начала цикла регенерации, начинающегося с началом сигнала 46 "Старт. рег,", обращение разрешается также в момент импульса 49 (фиг.З) .

Это преимущество устройства особенно важно при применении его в вычислительных системах типа дисплейных контролеров, где обращение к устройству для регенерации отображаемой информации должно быть с максимально возможной частотой с рав10 номерным (беэ перерывов) периодом (не более 1,0-.2 мкс) цикла считывания на динамический элемент памяти °

Формирование сигнала 51 включения триггера 21 осуществляется элементом И-НЕ 20. Сигнал с выхода триггера 21 поступает на входы формирователей 22, 23 и 24, где формируются сигнал 55 "СЕМП" (на вы20 ходе 37) и сигнал 58 "Запись или чтение" на выходе 40, кото1 ые осуществляют управление блоком 3 с частотой импульсов, генерируемых генератором 10 ° Длительности и периоды

25 следования сигналов управления (r ° 3) Формируются в соответствии с техническими условиями на применяем)й динамический элемент памяти.

При обращении вне периода регенерации заданный режим осуществляется беэ синхронизации с режимом регенерации.

Таким образом, происходит обращение к блоку 3 в любой момент вре35 мени независимо от операции регенерации. Это позволяет обеспечить минимальное время обращения к динамической памяти, определяемое только временными соотношениями приМеняемо-.

40. го элемента динамической памяти, 12l 33312 гя

Г

Г н

gii p ?!

211ц

41 ) 1

>>2 )

Г 1

»5 Г1

Г( J (1

Со =тавитель 1 „: аяцева

Техред М, i å >ãñ5 ь

Редактор JI,Êàñòpàí

Ко Р Р е к т o P I . I I >.> > и*;, >

Подписи>:е

Заказ 647/57 7. и р а 5 4 4

ВНИИПИ Государственного ксмнтета СССР по делам изобретений и >1>ткрытий

113035, Москва, Ж-35, Раymская наб,, д,4/5

Филиал ПШ1 "Патент" 5 г. l æãород, ул „Проектная, 4

Я

Хб

57

-т—

УУ (РР >7Ä i Уф Q >7