Умножитель напряжения

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 4 Н 02 М 7/10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ГО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3761924/24-07 (22) 11.07,84 (46) 15.02.86. Бюл. 9 6 (71) Отделение Всесоюзного научноисследовательского института электромеханики (72) В.И.Глухов и О.M.Ãëóõoâà (53) 621.3.14.6(088.8) (56) Электроника, 1970, У 5, с. 83.

Авторское свидетельство СССР

В 1072217, кл. Н 02 М 7/10, 1982. (54)(57) УМНОЖИТЕЛЬ НАПРЯЖЕНИЯ, содержащий транзисторные коммутирующие ключи, первый из которых эмиттером, а каждый из остальных через токоограничивающий резистор базой подключены к первому входному выводу для подключения одной из шин источника питающего напряжения, зарядные конденсаторы, каждый из которых, кроме последнего, включен между коллектором предыдущего и эмиттером последу)ощего транзисторных коммутирующих ключей, зарядные диоды, каждый из которых, кроме последнего, анодом подключен к общей точке соединения соответствующих конденсатора и эмиттера транзисторного коммутирующего ключа, а катодом — к первому входному выводу, выходной конденсатор, включенный параллельно выходным выводам устройства и одной обкладкой подключенный к первому входному выводу, дополнительный зарядный диод, анод которого соединен с другой обкладкой выходного конденсатора, а кагод — с общей точкой соединения последнего зарядного конденсатора и анода последнего зарядного диода, транзисторные зарядные ключи, коллекторно-эмиттерный переход каждого из которых включен между вторым входным выводом для подключения второй шины источника питающего напряжения и общей точкой соединения соответствующего коллектора транзисторного коммутирующего ключа и зарядного конденсатора, а базы которых через токозадающие резисторы объединены, о т л и ч а юшийся тем, что, с целью повьппения КПД в облас".и частот свьппе

1 кГц с одновременным повьппением стабильности выходного и питающего напряжения, в него дополнительно введены линия задержки, логическая схема И и логическая схема ИЛИ, причем выход логической схемы ИЛИ соединен с объединенными выводами токозадающих резисторов, выход логической схемы И через токозадающий резистор соединен с базой первого транзисторного коммутирующего ключа, выход линии задержки соединен с первыми входами логических схем И и ИЛИ, вторые входы которых объединены с входом линии задержки и подключены к третьему входному выводу для подключения шины управляющего сигнала.

1211840

Изобретение относится к радиотехнике и электронике и может применять . ся для повьппения напряжения питания радиоэлектронных схем, имеющих повышенное требование к малым энергоэатратам.

Цель изобретения — повьппение КПД устройства в области частот свьппе

1 кГц с одновременным повьппением стабильности напряжения источника питания и исходного напряжения устройства.

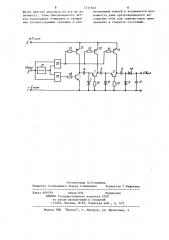

На чертеже приведена электрическая принципиальная схема предлагаемого умножителя напряжения.

Умножитель напряжения состоит из транзисторных коммутирующих ключей

1-3, зарядных конденсаторов 4-6, зарядных диодов 7-9, дополнительного зарядного диода 10 выходного конденсатора 11, транзисторных зарядных ключей 12-14, токоэадающих резисторов 15-20, схемь1 задержки 21, логических схем ИЛИ 22 и И 23.

Транзистор первого коммутирующего люча 1 эмиттером, а транзисторы оммутирующих ключей 2 и 3 базами через токоограничивающие резисторы

19 и 20, подключены к первому выводу для подключения отрицательной шины источника питания; зарядный конденсатор включен между коллектором транзистора l и эмиттером транзистора 2; зарядный конденсатор 5 включен между коллектором транзистора 2 и эмиттером транзистора.3; зарядные диоды 7 и 8 подключены соответственно анодом к общей точке соединения зарядных конденсаторов 4 и 5 с эмиттерами транзисторов 2 и 3, а катодом — к первому входному выводу; выходной конденсатор 11 включен параллельно выходным выводам и одной обкладкой соединен с анодом дополнительного зарядного диода 10, à другой — с первым входным выводом; катод дополнительнîrо зарядного диода

10 соединен с анодом зарядного диода 9 и одной обкладкой зарядного конденсатора 6, вторая обкладка. которого соединена с коллектором транзистора коммутирующего ключа 3; транзисторные зарядные ключи 12-14 эмиттерами соединены с вторым входным выводом для подключения положительной шины источника питания; коллектор транзистора 12 снязан с коллектором транзистора 1 и одной обклад5 !

О !

3S

40 коi зарядного конденсатора 4; коллектор транзистора 13 связан с коллектором транзистора 2 и одной обкладкой зарядного конденсатора 5; коллектор транзистора 14 связан с коллектором транзистора 3 и одной обкладкой зарядного конденсатора 6; базы транзисторов 12-14 через токоэадающие резисторы 15-17, соедийены с выходом логической схемы ИЛИ 22; выход логической схемы И 23 через токозадающий резистор 18 связан с базой транзистора коммутирующего ключа 1; третий входной вывод для подключения шины упранляющего сигнала связан с входом схемы задержки

21 и первыми входами логических схем И 23 и ИЛИ 22, а вторые входы логических схем И и ИЛИ соединены с выходом линии задержки 21.

Умножитель работает следующим образом.

Ца третий входной вывод умножителя напряжения поступает управляю- щий сигнал н виде последовательности прямоугольных импульсов с частотой 1 . Этот сигнал проходит на входы логических схем И, ИЛИ и линию задержки, Линия задержки обеспечивает задержку прохождения входного импульса на величину а °, которая определяется необходимой разницей времени отпирания и запирания транзисторов коммутирующего и зарядного ключеи для полного рассасывания неоснонных носителей из базы при запирании транзисторов. Для разного тица транзисторон эта величина вполне определенна.

На выходе логической схемы ИЛИ 22 обраэуется импульс, длительность которого больше длительности управляющего импульса на величину ь, а на выходе логической схемы И вЂ” импульс., длительность которого меньше длительности управляющего импульса на величину а с . Таким образом, на входы первого зарядного и первого коммутируюшего транзистора поступают упранляющие сигналы, имеющие разную длительность, причем передний фронт импульса, поступающего на базу транзистора коммутирующего ключа 1 отстает от переднего фронта. импульса, поступающего на базу транзистора зарядного ключа 12 на величину ьс, а его задний фронт опережает соответствующий задний

+ Fnurrr г

Оу

&Ajax

Составчтель Л.Устинкина

Редактор Л,Авраменко Техред О.Ващишина Корректор Г.Решетник

Заказ 649/59 Тираж 632 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 фронт другого импульса на эту же ве личину а . Этим обеспечивается четкое чередование отпирания и запирания соответствующих зарядных и ком1211840 4 мутирующих ключей и исключается возможность даже кратковременного нахождения этих пар транзисторов одновременно в открытом состоянии.