Интегральный формирователь импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к одновибраторам, формирующим импульс заданной длительности по перепаду входного сигнала, и предназначено для работы в интегральных цифровых схемах на МОП-транзисторах. Устройство содержит два инвертора, выполненных , например, на транзисторах 1,2 и 3, 4 соответственно, входную шину 5, конденсатор 6, транзисторы 7 и 8 с индуцированным каналом , транзистор 9 с встроенным каналом , выходную шину 10 и общую шину 1 1 . Введение транзистора 8 с индуцированным каналом и транзистора 9 с встроенным каналом позволяет повысить стабильность длительности выходного импульса и быстродействие устройства за счет уменьшения влияния разброса параметров элементов устройства на длительность формируемого импульса и уменьшить длительность среза импульса. 1 ил. (Л «

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4

ОПИСАНИЕ ИЗОБРЕТ

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3769276/24-21 (22) 05.07.84 (46) 15.02.86. Бюл. Ф 6 (72) А.С.Свердлов и Р.Я.Попова (53) 621.373 (088.8 ) (56) Волков С. Генеоаторы прямоугольных. импульсов на МОП-элементах.—

М.: Энергоиздат, 1981, с. 102, рнс. 3.28.

Микросхема К 1809 РУ 1 бК0.348.727-02 ТУ. (54} ИНТЕГРАЛЬНЫЙ ФОРМИРОВАТЕЛЬ

ИМПУЛЬСОВ (57) Изобретение относится к одновибраторам, формирующим импульс заданной длительности по перепаду входного сигнала, и предназначено для работы в интегральных цифровых схемах на МОП-транзисторах. Устройство содержит два инвертора, выполненных, например, на транзисторах 1, 2 и 3, 4 соответственно, входную шину 5, конденсатор 6, транзисторы 7 и 8 с индуцированным каналом, транзистор 9 с встроенным каналом, выходную шину 10 и общую шину 11. Введение транзистора 8 с индуцированным каналом и транзистора 9 с встроенным каналом позволяет повысить стабильность длительности выходного импульса и быстродействие устройства за счет уменьшения влияния разброса параметров элементов устройства на длительность формируемого импульса и уменьшить длительность среза импульса. 1 ил.

Изобретение относится к одновибраторам, формирующим импульс. заданной длительности по перепаду входного сигнала, и предназначено для работы в интегральных цифровых схемах на МОП-транзисторах.

Целью изобретения является лов вышение стабильности длительности выходного импульса и быстродействия устройства за счет уменьшения влияния разброса параметров элементов устройства на длительность формируемого импульса и уменьшения длительности среза импульса.

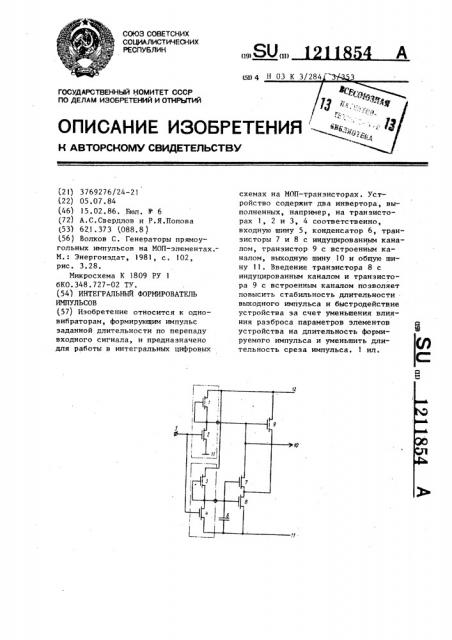

На чертеже изображена схема устройства.

Интегральный формирователь импульсов содержит первый и второй инвер— торы, выполненные, например, на транзисторах 1, 2 и 3, 4 соответственно, входы которых соединены с входной шиной 5, выход второго через конденсатор 6 соединен с об— щей шиной и непосредственно — с затворами первого и второго транзисторов 7 и 8 с индуцированным каналом, третий транзистор 9 с встроенным каналом, причем исток транзистора 7 и затвор транзистора 9 соединены с выходом первого инвертора и выходной шиной 10, исток транзистора 8— с общей шиной 11, истоки транзисторов 7 и 9 и исток транзистора 8— между собой, а сток транзистора 9 с шиной питания 12, Устройство работает следующим образом.

В исходном состоянии на входной шине 5 присутствует единичный потенциал высокое напряжение) . Транзисторы 2 и ч инверторов открыты, конденсатор 6 разряжен, на выходной шине 10- нулевой потенциал (низкое напряжение) . Отрицательный перепад напряжения на шине 5 вызывает запирание транзисторов 2 и 4 инверторов. Начинается формирование выходного импульса единичного потенциала на выходной шине 10 длительность фронта которого определяется временем заряда выходной емкости через транзистор 1 первого инвертора.Одновременно начинается заряд конденсатора 6 через транзистор 3 втсрого инвертора. Когда напряжение на конденсаторе 6 достигнет порогового напряжения транзистора 8, он переходит в активный режим и потенциал

11Р5 его стока и соответственно истока транзистора 7 начинает понижаться.

Одновременное дальнейшее нарастание напряжения на конденсаторе 6, соединенном с затвором транзистора 7, и уменьшение напряжения на истоке транзистора 7 приводит к отпиранию транзистора. На этом формирование выходного импульса заканчивается °

Отпирание транзистора 7 вызывает уменьшение потенциала на его истоке и соответственно выходной шине 10.

Через транзистор 9, работающий в режиме истокового повторителя, из15 менение потенциала шины 10 передается на исток транзистора 7> способствуя его дальнейшему .открыванию. Воз-. никает положительная обратная связь, способствующая быстрому отпиранию

20 транзистора 7 и установлению на вы-. ходной шине 10 "нулевого" потенциала.

Благодаря наличию указанной положительной связи происходит умень25 шение длительности среза выходного импульса и за счет этого растет быстродействие устройства.

Одновременно интегральное исполнение формирователя по предлагаемой

30 схеме способствует росту стабильности длительности формируемого импульса,,Например, увеличение проводимости транзистора 3, способствующее ускорению процесса заряда конденсатора 6, компенсируется увеличением проводимости транзистора 9, способствующее возрастанию запирающего потенциала на истоке транзистора

7.

4О

Формула изобретения

Интегральный формирователь импульсов на ИОП-транзисторах, содержащий первый и второй инверторы, у которых входы соединены с входной шиной, выход первого непосредственно — с выходной шиной, а выход второго через конденсатор. — с общей шиной, и пер б вый транзистор с индуцированным каналом,, сток и затвор которого соединены с выходами первого и второго инверторов соответственно, о т л ич а ю шийся тем, что, с целью

5 повышения стабильности длительности выходного импульса и быстродействия ус-ройства, в него введены второй транзистор с индуцированным каналом, У

Составитель С.Агеев

Редактор Л.Авраменко Техред О.Ващишина

Корректор Г.Решетник

Заказ 649/59 Тираж 818 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Г

Филиал ППП "Патент", r. Ужгород, ул.Проектная,4 затвор и сток которого соединены с затвором и истоком первого транзистора соответственно, а исток — с общей шиной, и третий транзистор с

1211854 4 встроенным каналом, затвор и исток которого соединены со стоком и истоком первого транзистора соответственно, а сток — с шиной питания.