Устройство обработки импульсов

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3753171/24-21 (22) 14.06.84 (l6) 15.02.86. Бюл. К - 6 (72) A.Ã. Андронов, P.M. Мусин и ff.fÎ. илатов (53) 621. 373(088. 8) (56) Грязнов М.И. Интегральный метод измерения импульсов. M.: — Советское радио, 1975, с. 226-229.

Техника средств связи, сер.РТ, вып. 1(19), М., 1979. (54) (57) УСТРОЙСТВО ОБРАБОТКИ ИМПУЛЬСОВ, содержащее усилитель расширенных импульсов и аналого-цифровой преобразователь, о т л и ч аю щ е е с я тем, что, с целью уменьшения погрешности преобразования и повышения помехозащищенности, в него введены электронный переключатель, первый, второй и третий компараторы, источник опорного напряжения, блок управления и первый и второй интеграторы, причем входы интеграторов объединены и подключены к выходу усилителя расширенных импульсов, выход первого интегратора соединен соответственно с первыми входами пер„,SU„„1211861 (ц 4 Н 03 К 5/01 5/153 вого компаратора, третьего компаратора и электронного переключателя, а выход второго интегратора — с первым входом второго компаратора, вторым входом третьего компаратора и вторым входом электронного переключателя, выходы первого и второго компараторов соединены с первым и вторым входами блока управления, а выход третьего компаратора — с третьим входом электронного переключателя, выход которого подключен к первому входу аналого-цифрового преобразователя, второй вход последнего соединен с первым выходом блока управления, первый выход аналого-цифрового преобразователя является выходом устройства, а второй выход соединен с третьим входом блока управления, второй и третий выходы которого соединены соответственно с вторыми входами первого и второго интеграторов, вторые входы первого и второго компараторов соединены с источником опорного напряжения, вход усилителя расширенных импульсов является входом устройства обработки импульсов.

1211861

Изобретение относится к импульсной технике и может быть использовано при создании радиоизмерительной аппаратуры, в частности измерителей параметров импульсов, вольтметров и др.

Цель изобретения — уменьшение погрешности преобразования снижение

) требований к быстродействию и повышение помехозащищенности.

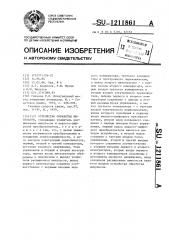

На фиг. 1 представлена электрическая блок-схема устройства, на фиг.

2 — пример конкретной реализации блока управления, Устройство содержит усилитель 1 расширенных импульсов и аналогоцифровой преобразователь 2, электронный переключатель 3, первый второй и третий компаряторы 4, 5 и

6, источник 7 опорного напряжения, блок 8 управления и первьгй и второй интеграторы 9 и 10, причем первые входы интеграторов 9 и 10 обт.единены и подсоединены к выходу усилителя

1 расширенных импульсов, выход первого интегратора 9 соединен с первым входом первого компярятора 4, первым входом третьего компяратора 6 и первым входом электронного переключателя 3, а выход второго интегратора соединен с первым входом второго компаряторя 5, вторым входом третьего компаряторя 6 и вторым входом электронного переключателя 3, выходы первого и второго компаратора 4 и 5 соединены с первым и вторым входом блока 8 управления, выход третьего компяратора 6 соединен с третьим (упряв1тяющим) входом электронного переключателя 3, выход которого подключен к первому входу аналого-цифрового преобразователя

2, второй вход которого соединен с первым выходом блока 8 управления, первый выход аналого-цифрового преоб. разователя (АЦП)2 является выходом

11 устройства, я второй выход АЦП 2 соединен с третьим входом блока 8 управления, второй и третий вьгходы которого соединены соответственно с вторыми входами первого и второго интегратора 9 и 10, вторые вхоцы первого и второго компараторов 4 и 5 соединены с источником 7 опорного напряжения, вход усилителя 1 расширенгн4х импульсов является входом 12 устро 1етвя обработки импульсов °

?5

35

1О

l5

Работа устройства заключается в следующем.

При отсутствии сигнала на выходе усилителя 1 расширенных импульсов, а следовательно, и на входе первого и второго интеграторов 9 и 10 они попеременно находятся в режиме интегрирования и обнуления, т,е, хотя бь| один из интеграторов находится в режиме интегрирования. Управление интеграторами 9 и 10 происходит от блока 8 управления, причем режимы интегрирования первого и второго интеграторов 9 и 10 перекрываются во времени. Время перекрытия больше или равно максимальной длительности входных импульсов. Таким образом независимо от времени прихода входного импульса, хотя бы один из интервалов проинтегрирует его полностью.

С приходом входного импульса на вьгходе одного или сразу двух интеграторов 9 и 10, в зависимости от времени прихода импульса появится выходной сигнал. пропорциональный площади вх. дного сигналя, при этом срябатывяг т соответственно один или оба компяратора 4 и 5, в зависимости от времени прихода входного сигнала.

Возможны три ситуации приходя вхоДнога импульса. Первая ситуация, когда во время действия входного импульса один интегратор работает, а второй интегратор приводится в исходное состояние В этом случае полезный сигнял появляется только на одном выходе устройства, срабатывает один компаратор. Вторая ситуация, когда в момент прихода измеряемого импульса работают оба интегратора. В этом случае на обоих выходах устройства при идентичности интеграторов 9 и 10 появляются одинаковые выходные сигналы, срабатывают оба компаратора

4 и 5. Третья ситуация, когда измеряемый импульс начинается при работе одного интегратора, а заканчивается когда включены оба интегра-! тора, т.е. один из интеграторов начинает работать во время действия входного импульса. В этом случае срабатывают оба компаратора 4 и 5.

На вьгходах обоих интеграторов 9 и

10 появится сигнал, но на выходе того интегратора, который работал в . течении всего времени действия вход. ного импульса, сигнал будет больше.

1211861

Этот сигнал и является верным, так как появился на выходе интегратора, проинтегрировавшего весь входной импульс, Таким образом, общим для всех треХ случаев является то, что достоверным всегда является больший сигнал, его величина.

Сигналы с компараторов 4 и 5 поступают на блок 8 управления, который управляет интеграторами так, что они остаются в режиме интегрирования, и вьдает импульс на запуск

АЦП 2. Для подачи на первый вход

А1(П 2 наибольшего сигнала служит электронный переключатель 3, который управляется от третьего компаратора 6. После окончания преобразования сигнала, поступившего на вход

А11П 2, в цифровой код он выдает сигнал об окончании работы на блок 2 управления, который переводит интеграторы в первоначальный режим попеременного интегрирования.

Первый и второй интеграторы могут быть выполнены на операционных усилителях с включением интегрирующей емкости в цепь обратной связи, а для управления интегратора можно применить электронный ключ, замыкающий эту емкость.

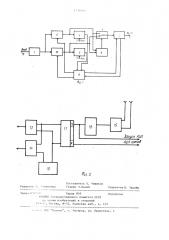

Блок 8 управления может быть расчитан формально как конечный автомат исходя из логики его работы, и может, например, содержать первый, второй и третий элементы ИЛИ 13, 14 и 15, генератор 16 последовательностей импульсов, триггер 17 RS — типа и ждущий мультивибратор 18, первым и вторым входами блока 8 управления являются первый и второй входы третьего элемента ИЛИ 15, выход которого подключен через ждущий мультивибратор 18 к третьему выходу блока

8 управления и к входу триггера 17, R-вход которого соединен с третьим входом блока 8 управления, а прямой выход триггера 17 подключен к первым входам первого и второго элементов ИЛИ 13 и 14, вторые входы которого подключены к входам генератора ° пилообразных импульсов, а первый и второй выходы первого и второго элементов ИЛИ являются соответственно первым и вторым выходами блока 8 управления °

Блок 8 управления работает следующим образом.

При отсутствии входного сигнала

10 триггер 17 находится в нулевом положении и на выходы элементов ИЛИ 13,14 проходят импульсы управления с генератора последовательности импульсов (ГПИ) 16. Сигналы с выходов первого

15 и второго компараторов 4 и 5 поступают через элемент ИЛИ 15 на ждущий мультивибратор 18, который вырабатывает импульс запуска АЦП и устанавли. вает триггер 17 в единичное состоя20 ние. Сигнал с триггера 17 через элемент ИЛ1» 13 и 14 запрещает обнуление интеграторов (считается, что обнуление интеграторов происходит при нулевом сигнале на выходе эле25 ментов ИЛИ 13 и 14). После преобразования аналогового сигнала в цифровой код А1(П 2 сигнал с выхода

АЦП 2 возвращает триггер 17 в исходное положение и интеграторы 2 и 3 щ переходят на режим попеременной работ.,! (Исходный ppxHM), Таким Образом, независимо от времени прихода входного импульса устройство обеспечивает его более точное иэмерение и исключение погРешности за счет задержки синхронизирующего сигнала, т.е. нет погрешности привязки. Уровень срабатывания компараторов 4 и 5 путем подачи напряжения

40 на вторые их входы выбирается равным сигналу с выхода интегратора, соответствующего минимальному по амплитуде и длительности входному сигналу, что исключает ложное сраба45 тывание устройства от помех, произведение длительности которых на их амплитуду, т.е. площадь, меньше площади минимального измеряемого импульса.

Составитель В. Чижиков

Техред З.Палий

Корректор И. Эрдейи

Редактор . !. иваиенко

f fl ill "!!а тент", г. Ужгород, ул. Проектная, 4

Заказ 6".о о Тираж 818 Подписное

К!11111!111 1 осударственного комитета СССР

lt<? дезам изобретений и открытий!!з !., 1огква, Ж вЂ” 35, Раушская наб., д. 4/5