Устройство распределения оперативной памяти

Иллюстрации

Показать всеРеферат

СО1ОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (Я) 4

ОПИСАНИЕ ИЭОБРЕТ

Н ABTOPCHOMY СВИДЕТЕЛЪСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

1 (21) 3768729/24-24 (22) 11.07.84 (46) 23.02.86. Бюл. У 7 (72) С.В.Ефимов, В.В.Мазаник, В.M.Íåôôà и Ю.Л.Степанов (53) 681.32(088.8) (56) Авторское свидетельство СССР

Ф 602934, кл. G 06 F 13/00, 1975.

Авторское свидетельство СССР

У 881722, кл. G 06 F )3/00, 1981. (54) (57 ) УСТРОЙСТВО РАСПРЕДЕЛЕНИЯ

ОПЕРАТИВНОЙ ПАМЯТИ, содержащее первый коммутатор, второй коммутатор, регистр, первую и вторую группу регистров, причем вход запроса устройства подключен к управляющему входу первого коммутатора, нулевой информационный вход первого коммутатора подключен к входу требуемого размера массива устройства, нулевой выход первого коммутатора подключен к входу регистра .(2i-1)-й информационный вход первого коммутатора подключен к

i-му входу размера свободного массива устройства, 1-й вход начального адреса свободного массива устройства (i=1,ï, где и — количество входов в группе) подключен к

2j му информационному входу первого коммутатора, (2i-1)-й выход первого коммутатора подключен к входу i-ro регистра первой группы, выход которого подключен к (2i-1)-му информационному входу второго коммутатора, первый и второй выходы которого подключены соответственно к выходу размера предоставляемого массива устройства и

„„SU„„1213484 А к выходу начального адреса предоставляемого массива устройства, 2i-й выход первого коммутатора подключен к входу i-го регистра второй группы, выход которого подключен к 2i-ìó информационному входу второго коммутатора, о т л и ч аю щ е е с я тем, что, с целью сокращения среднего времени поиска свободного массива памяти, в него введены элемент задержки, группа схем сравнения, матрица схем сравнения, матрица компараторов, элемент ИЛИ, элемент НЕ, элемент И и группа элементов И, причем выход регистра подключен к первым входам схем сравнения группы, второй вход и выход i-й схемы сравнения группы подключен соответственно к выходу

i — ro регистра первой группы и к

i-му входу элемента ИЛИ, выход которого подключен к первому входу элемента И и через элемент НŠ— к выходу признака отсутствия запрашиваемого массива устройства, выход признака наличия запрашиваемого массива которого подключен к выходу элемента И, второй вход которого подключен к выходу элемента задержки, вход которого подключен к входу запроса устройства, выход элемента И подключен к нулевому управляющему входу второго коммутатора, (2i-1)-й управляющий вход которого подключен к выходу i-го элемента И группы и к 21-му управляющему входу второго коммутатора, выход i-ro регистра первой группы подключен к первым входщ К,i-х схем сравнения матрицы (=l,i-l) и к вто1213484

25 рым входам i,Ì-х схем сравнения матрицы (M=i+1,n), первый, второй и третий информационные входы 1, j-го компаратора подключены соответственно к выходу 1-й (1=1,n-l) схемы сравнения группы, к выходу ,)-й ()=1+1,п) схемы сравнения группы и к выходу 1,)-й схемы сравнения матрицы, К-й и М-й входы i-ro элемента И группы подключены соответственно к первому выходу К,i-ro ком паратора и к второму выходу i,М-ro компаратора.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем,что компаратор содержит пять элементов НЕ, четыре элемента И и два элемента

ИЛИ, причем первый, второй и третий информационные входы компаратора подключены соответственно к первому, второму и третьему входам первого элемента И компаратора, выход которого подключен к первому входу первого элемента ИЛИ компаратора, второй вход и выход которого подключе1

Изобретение относится к вычислительной технике, в частности к устройствам управления вычислительными комплексами. Цель изобретения — сокращение среднего времени поиска свободного массива памяти.

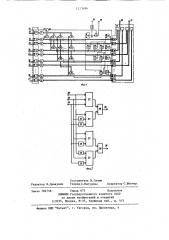

На фиг. 1 представлена функциональная схема устройства, на фиг.2функциональная схема компаратора.

Устройство содержит первый коммутатор 1, первый 2 и второй 3 блоки групп элементов И, первую

4 и вторую 5 группы регистров, группу элементов И 6, регистр 7, элемент 8 задержки, группу 9 схем сравнения, матрицу 10 схем сравнения, матрицу 1.1 компараторов, элемент ИЛИ 12, элемент НЕ 13, элемент И 14, группу 15 элементов

И, третий 16 и четвертый 17 блоки групп элементов И, второй коммутатор 18, группы 19 и 20 элементов

ИЛИ, вход 21 и выход 22 элемента ны соответственно к выходу второго элемента И компаратора и к первому выходу компаратора, второй выхоД которого подключен к выходу второго элемента ИЛИ компаратора, входы Которого подключены к выходам третьего и четвертого элементов И компаратора, первый информационный вход компаратора подключен к первым входам второго и третьего элементов И компаратора и через первый элемент

HE компаратора — к первому входу четвертого элемента И компаратора, второй информационный вход компара-. тора подключен к вторым входам третьего и четвертого элементов И компаратора и через второй элемент HE компаратора — к второму входу второго элемента И компаратора, третий информационный вход компаратора че- . рез третий, четвертый и пятый элементы НЕ компаратора подключен к третьим входам соответственно второго, третьего и четвертого элементов И компаратора. задержки, выход 23 элемента ИЛИ

f вход 24 запроса, вход 25 требуемого размера массива, входы 26 размера свободного массива, входы 27 начального адреса свободного массива устройства, выходы 28 признака отсутствия и ."9 признака наличия запрашиваемого массива устройства, выходы 30 размера и 31 начального

10 адреса предоставляемого массива устройства.

Компаратор содержит первый 32, второй 33 и третий 34 входы, первый

35 и второй 36 выходы, элементы

15 И 37, элементы HI(3 38 и элементы

НЕ 39.

Устройство работает следующим образом.

По сигналу, поступающему на пер20 вый вход 24 устройства, открываются элементы И 2,3, 6 первого коммутатора 1, через которые на входы регистров 4 и 5 принимаются коды размеров и начальных адресов свобо— о од1213484 ных массивов памяти с первой и второй групп входов 26 и 27 устройства, а на вход регистра 7 принимается код размера требуемого свободного массива памяти с входа 25 устройства. Сигнал с входа 24 поступает также на элемент 8 задержки.

К-я схема 9 сравнения вырабатывает сигнал Ак, означающий, что.размер требуемого свободного массива памяти меньше или равен размеру K -ro свободного массива. 1з -я схема 10 сравнения вырабатывает сигнал В;„, означающий, что размер l-ro массива меньше или равен размеру д-ro

1 массива. Сигналы В;„ поступают соответственно на первый 32, второй 33 и третий 34 входы ij-й схемы 10.

Сигнал С1„ на первом выходе 35 схемы означает, что размер.i-ro массива меньше или равен размеру j-го массива, или j-й массив не принимается во внимание, так как его размер меньше требуемого. Сигнал Р;„. на втором выходе 36 ij-й схемы 10 означает, что размер i-ro массива больше размера J-ro массива, или

i-й массив ие принимается во внимание, так как его размер меньше тре буемого. Сигналы выбора Сц и 0;„ поступают на группу элементов И 15.

К-й элемент И 15 формирует сигнал выбора К-ro массива Ек.

Единичное значение принимает только один сигнал Ек, номер которого соответствует первому из наиболее подходящих по размеру и требуемому свободному массиву памяти.

Сигналы поступают на входы элемента

ИЛИ 12, единичный сигнал на выходе которого говорит о наличии хотя бы одного свободного массива памяти, размер которого больше или равен

5 требуемому. Сигнал F< открывает

К-ю пару групп элементов И 16 и 17,. на которую поступают коды начального адреса и размера К-го свободного массива памяти с выходов К-й пары регистров 4 и 5. Сигналы с,выходов элемента ИЛИ 12 и элемента 8 задержки поступают на вход элемента

И 14. Сигнал с выхода элемента

И 14 поступает на второй выход 29

15 устройства и открывает .элементы

И 16 и 17. Так как единичное значение принимает только один сигнал

Е, то только на выходах соответствующей ему пары групп элементов

20 И 16 и 17 появятся коды размера и начального адреса первого наиболее подходящего массива памяти, которые выдаются через группы элементов

ИЛИ 19 и 20 коммутатора 18 вывода .

25 информации на первый 30 и второй

31 выводы устройства.

В том случае, если среди всех свободных массивов памяти нет ни одного, который был бы больше или ращ . вен по размеру требуемому, сигнал на выходе элемента ИЛИ 12 принимает нулевое значение. Он поступает на элемент НЕ 15, с выхода которого выдается на первый выход 28 устройства. Сигнал на выход 29 в данном случае не выдается, а коды размера и начального адреса на первом 30 и втором 31 выходах устройства имеют нулевое значение.

1213484

Фиг. f

ФАР

Тираж 673 Подписное

БНИИПИ Государственного комитета СССР. по делам изобретений и открытий

lj3035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 782/58

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель M.Ñèëèí

Редактор Н.Данкулич Техред С.Мигунова Корректор С.Шекмар,