Устройство для приема и обратного кодирования информации

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и может использоваться при восстаиовлении информации, кодированной сверточиым перфорированным кодом. Изобретение позволяет повысить быстродействие устройства за счет того, что восстановление производится рекуррентным методом.Устройство содержит переключатель,,ключи, регистры, блоки задержки, блок сумматоров, регистры , блоки сумматоров по модулю два, счетчики, блок управления и . переключатель, Блок сумматоров содержит сумматоры по модулю два и элементы НЕ. Блок управления содержит элемент Постоянной памяти, элементы сравнения, элементы И, шифратор и формирователь импульсов. 1 з.п. ф-лы. 3 ил. ts3 00 4 QO 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ.

ГОСУДАРСТЪЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3778953/24-24 (22) 31 ° 07.84. (46) 23.02.86. Бюл. У 7 (72) Я.Д. Хацкелевич и К.А. Гасумян (53) 621 398 (088.8) (56) Авторское свидетельство СССР

Ф 960896, кл. G 08 С 19/28, Н 04 L 1/10, 1981.

Авторское свидетельство СССР

9 924888,кл. Н 04 L I/10, Н 04 L 7/00, 1979. (54) УСТРОЙСТВО ДЛЯ ПРИЕМА И ОБРАТНОГО КОДИРОВАНИЯ ИНФОРМАЦИИ (57) Изобретенйе относится к электросвязи и может использоваться при . восстановлении информации, кодирован"

„„SU„„1213493 A рр а С 08 С 19/28 ной сверточным перфорированным кодом.

Изобретение позволяет повысить быст" родействие устройства за счет того, что восстановление производцтся рекуррентным методом. Устройство содержит переключатель„ключи, регистры, блоки задержки, блок сумматоров, регистры, блоки сумматоров по модулю два, счетчики, блок управления и . переключатель. Блок сумматоров содержит сумматоры по модулю два и элементы НЕ. Блок управления содержит элемент йостоянной памяти, элементы сравнения, элементы И, шифратор и формирователь импульсов. 1 з.п. ф-лы.

3 ил.

1213493!

Изобретение относится к электросвязи и может быть использовано в системах контроля передаваемой информации при восстановлении информа-. ции, кодированной сверточным перфорированным кодом.

Цель изобретения - повышение быстродействия устройства.

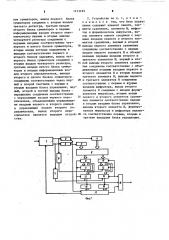

На фиг. 1 приведена структурная схема устройства для "приема и обратного кодирования информации; на фиг. 2 — функциональная схема блока сумматоров (вычислителя);на фиг. 3то же, блока управления.

Устройство для приема и обратного кодирования информации (фиг. 1) содержит переключатель 1, ключи

2 и 3, регистры 4 и 5 блоки 6 и 7 задержки, блок 8 сумматоров (вычислитель), регистры 9 .и 10, блоки

11 - 14 сумматоров по модулю два, счетчики 15 и 16, блок 17 управления и переключатель 18.

Блок 8 сумматоров (вычислитель)

1фиг. 2) содержит сумматоры 19 — 33 по модулю два и элементы НЕ .34 - 37.

Блок 17 управления (фиг. 3) содержит элемент 38 постоянНоН памяти, элементы 39 и 40 сравнения, элементы И 41 — 43, шифратор

44 и формирователь 45 импульсов.

Устройство работает следующим образом.

На вход переключателя 1 поступает входной сигнал, представляющий последовательность двоичных кодовых символов. Переключатель I разделяет входную последовательность символов на две последовательности $ 1 и SI,, < сбответствующие двум генераторным полиномам сверточного кода с учетом правила перфорации 1выкалывания или стирания символов), выбранного для данного перфорированного сверточного кода. Индекс i обозначает порядковый номер временного. интервала, в котором появляется символ SI,g .В начальный момент времени ключи 2 и

3 открыты на время, пока регистры

4 и 5 не заполняются. По заполнении регистров 4 и 5 содержимое их подает ся на вычислитель 8, который определяет сигналы начальной установки для регистров 9 и 10.

Последовательность информационных символов обозначена через (а 1), где i — порядковый номер символа.

Тогда кодовый символ S;,q определяется как

S j, q = f a; 3 G1 (x) =a; Оа - Э а1- з О+а; ч ф а -5 °

Из последнего уравнения следует, что если известны информационные символы а;,-а1, а также принимаемые безошибочно кодовые символы

S; 1, то можйо составить рекуррент-.

< ное уравнение для определения информационной последовательности а =а; 0+а1 э&а; Эа; ь О+81,1 . (I)

По последовательностям кодовых символов Б i 1 где =1,2,3,... и ,!

S, где =1,4,7,... путем составле1 ния и решения системы алгебраических уравнений однозначно определить пять последовательных информационных символа невозможно. Условно определяются пять информационных символов в предположении известного значения шестого символа. Поскольку данныйсимвол может иметьтолько два значения 0 и I, то длякаждого из этих значений можно определить набор информационных символов по следующим уравнениям:

О< 1=-5,1®5 <,L®+<-<, . О = 5<+1,1Е Sl+2,1® 5 i+3,19 5 эд Юа,-4, «+1-5<+31© 5 <+3

9;,g 19SI+ g 195;+э,195;+ эд, 1+2 = 5<,1®51Л@5 +319 SI+3,2++1-9

+ i+3 = Si + Q 19 8 <+5<19 S i+ 6 q 9 S I+ Ä9

®5,„ S; +о<-q.

Полагая, что а1. к =0 и а; „=1, получаем два набора а<-1, а< ° а< 1 а<г ° <+3 и а;„;а;„;а;+,, а;„, а;+, начальных информационных символов, иэ которых один является истинным.

Решение укаэанных уравнений путем суммирования по модулю два набора канальных символов производится в вычислителе 8, функциональная схема которого приведена на фиг. 2.

В результате решения рекуррентного уравнения (1) с двумя разными начальными условиями получаются две разные информационные последовательности. Решение рекуррентного уравнения производится на регистре

9 с обратной связью через блок II сумматоров по модулю два, на кото» рый через блок 6 задержки поступают кодовые символы S 1 от переключателя 1. На выходе блока 11 сумматоров формируется кодовая последователь 1213493 ность, которая поступает на вход регистра 9. Аналогично соединены регистр 10 и блок 12 сумматоров по модулю два, на которых производится решение рекуррентного уравнения (1 ) с другими начальными условиями.

Выходные кодовые последовательности с блоков 11 и 12 сумматоров подаются на переключатель 18,. а также на входы блоков 13 и 14 сумматоров,. на которые также поступают кодовые последовательности с регистров 9 и 10 и от переключателя

1 через блок 7 задержки кодовые символы S; . Так как кодовые после»

I довательнос ги с регистров 9 и 10 на блоки 12 и 14 сумматоров соответствуют генераторному полиному Gz, (X), то при правильной информационной последовательности на входе, на выходе одного из блоков 13 и 14 сумматоров будут одни нули в то время, как на выходе другого появятся и

Г единицы, которые указывают на ошибки.

Выходы блоков !3 и !4 сумматоров через счетчики 15 и 16 ошибок под-; ключены к блоку 17 управления. Блок

17 управления проводит сравнение с некоторым порогом, хранящимся в блоке 38 памяти, показаний . M и р соответственно счетчиков 13 и 14.

По. результатам сравнения выдаются следующие сигналы: о (П; у >Псигнал управления на переключатель

18 для выдачи информации с блока

11 сумматоров, о > П; Р< П - сигнал управления на переключатель 18 для выдачи информации с блока 12 сумматоров, П; В )П - управляющий сигнал -на переключатель 1 и одновременно сигнал открытия ключей

2 и 3 на время, необходимое для заполнения регистров 4 и 5, запрет .выдачи информации.

Переключатель 1 входную кодовую последовательность преобразует в две последовательности $! j и S 1,, соответствующие двум кодовым полиномам С4(Х) и Gg(X). Так как последовательность S1 представляет перфорированную (выколотую) кодовую последовательность, то на выход переключателя символы подаются с периодом, равным перйоду ветви кода.

Начало ветви (узловая синхронизация ) устанавливается путем после1 довательного сдвига на такт (или пропуска такта) тактовой сетки переключателя 1 по уйравляющему.сигналу блока 17 управления.

Таким образом, при отсутствии

5 ошибок в канальных символах устрой ство. безошибочно I.: выдает на выход, информационную последовательность.

При наличии даже одиночных ошибок в канальной последовательности !

О . S за счет того, что восстановление информации производится рекур рентным методом — регистром 9 с обратной связью через блок 11 сумматоров (ипи соответственно 10 и 12), происходит последовательное накопление ошибок в счетчиках 15 или 16, что фиксируется блокбм 17 управления °

ОдиноЧная ошибка в канальной

20 последовательности будет зафиксирована .в счетчиках 15 и 16 как одиночная ошибка.

Формула изобретения

1. Устройство для приема и обратного кодирования информации, содержащее первый переключатель, информационный вход которого является входом устройства, первый выход первого переключателя соединен через первый блок задержки с первым входом первого блока сумматоров, второй выход первого переключателя

З5 соединен через второй блок задержки с первым входом второго блока сумматоров, о т л и ч а.ю щ е е с я

t тем, что, с.целью повышения быстродействия,в него введены ключи, ре40 гистры, счетчики, блок управления, третий, четвертый, пятый блоки сум. маторов и второй переключатель, информационные входы первого и вто- . рого ключей подключены соответствен»

45 но к первому и второму выходам первого переключателя, выходы первого и второго ключей соединены с входа".. ми.соответственно первого и второгб регистров, выходы первого и второго

5О регистров соединены соответственно с первыми и вторыми входами третьего блока сумматоров, первые и вторые выходы третьего блока сумматоров сое;, динены с первыми входами соответственно третьего и четвертого регистров, первые и вторые выходы третьего ре гистра соединены с вторыми входами соответственно первого и второго бло1213493 ков сумматоров, выход первого блока сумматоров соединен с вторым входом третьего регистра, третьим входом второго блока сумматоров и первым информационным входом второго переключателя, первые и вторые выходы четвертого регистра соединены с первыми входами соответственно четвертого и пятого блоков сумматоров, вторые входы которых подключены к выходам соответственно первого и второго блоков задержки, выход четвертого блока сумматоров соединен с вторым входом четвертого регистра, третьим входом пятого блока сумматоров и вторым информационным входом второго переключателя, выходы второго и пятого блоков сумматоров соединены соответственно через первый и второй счетчики с первым и вторым входами блока управления, первый, второй и третий выходы блока управления соединены соответственно с управляющим входом первого переключателя, объединенными управляющими входами первого и второго ключей и управляющим входом второго переключателя, выход второго переключателя является выходом устройства.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок управления содержит элемент памяти, эле-

5 менты сравнения, элементы И, шифратор и формирователь импульсов, выход элемента памяти соединен с первыми входами первого и второго элементов сравнения, первый и второй

>0 выходы первого элемента сравнения соединены соответственно с первым входом первого элемента И и объединенными первыми входами второго и третьего элементов И, первый и вто15 рой выходы второго элемента сравнения соединены соответственно с объединенными вторыми входами первого и второго элементов И и вторым входом третьего элемента И, выходы первого

20 и третьего элементов И соединены соответственно с первым и вторым входами шифратора, выход второго элемента И соединен с входом формирователя импульсов, вторые входы первого и второго элементов сравнения являются соответственно первым и вторым входами блока управления, . выходы второго элемента И, формиро- . вателя импульсов и шифратора являют30 ся соответственно первым, вторым и третьим выходами блока управления.! 2! 3493

g„g,) 8п в у) е ga мевмлаМ Ьмжклюе- i%rаюмг 2иЮ тыа f

ФАЗ

Составитель М. Никуленков

Редактор Н. Гунько Техред С.Мигунова Корректор Г. Решетник (Заказ 782/58 Тираж 516 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

l l3035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4