Логическое устройство

Иллюстрации

Показать всеРеферат

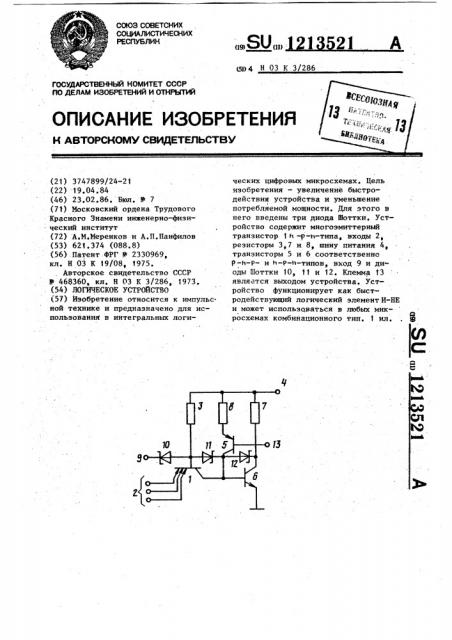

Изобретение относится к импульсной технике и предназначено для использования в интегральных логических цифровых микросхемах. Цель изобретения - увеличение быстродействия устройства и уменьшение потребляемой мощности. Для этого в него введены три диода Шоттки. Устройство содержит многоэмиттерный транзистор 1h -p-h-типа, входы 2, резисторы 3,7 и 8, шину питания 4, транзисторы 5 и 6 соответственно p-h-p- и h-p-h-типов, вход 9 и диоды Шоттки 10, 11 и 12. Клемма 13 является выходом устройства. Устройство функционирует как быстродействующий логический элемент И-БЕ и может использоваться в любых микросхемах комбинационного тип. 1 ил. , ю sH

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТ ИЧЕСНИХ

РЕСПУБЛИН (19) (И) (51) 4 Н 03 К 3/286 (21) 3747899/24-21 (22) 19.04.84 (46) 23.02.86. Бюл. Ф 7 (71) Московский ордена Трудового

Красного Знамени инженерно-физический институт (72) А,И.Меренков и А.П.Панфилов (53) 621,374 (088,8) (56) Патент ФРГ Ф 2330969, кл. Н 03 К 19/08, 1975.

Авторское свидетельство СССР

Ф 468360, кл. Н 03 К 3/286, 1973. (54) ЛОГИЧЕСКОЕ УСТРОЙСТВО (57) Изобретение относится к импульсной технике и предназначено для использования в интегральных логи1 21 А ческих цифровых микросхемах. Цель изобретения — увеличение быстродействия устройства и уменьшение

1 потребляемой мощности. Для этого в него введены три диода Шоттки. Устройство содержит многоэмиттерный транзистор 1 h --p-h-типа, входы 2 ° резисторы 3,7 и 8, шину питания 4 ° транзисторы 5 и 6 соответственно р-и-Р- и h-P-h-типов, вход 9 и диоды Шоттки 10, 11 и 12. Клемма 1 3 является выходом устройства. Устройство функционирует как быстродействующий логический элемент И-НЕ и может использоваться в любых микросхемах комбинационного тип. 1 ил. . Е

1 12

Изобретение относится к импульс-— ной технике и предназначено для использования в интегральных логических цифровых микросхемах.

Цель изобретения — увеличение быстродействия устройства и уменьшение потребляемой мощности, На чертеже представлена принципиальная схема предлагаемого логического устройства.

Логическое устройство содержит многоэмиттерный транзистор 1 п-р-итипа, эмиттеры которого подключены к информациочньпк входам 2 устройства, база через первый резистор 3 соединена с шиной питания 4, база и коллектор первого транзистора 5 р-п-р-типа подключены соответственно к коллектору и базе второго транзистора 6 п-р-п-типа, коллектор которого через второй резистор 7 подключен к шине питания 4, эмит-. тер — к общей шине, эмиттер первого транзистора 5 через третий резистор 8 соединен с шиной питания 4, управляющий вход 9 устройства.через третий диод Шоттки 10 соединен с базой многоэмиттерного транзистора 1, которая через первый диод Шоттки 11 соединена с коллекторами многоэмиттерного транзистора 1 и первого транзистора 5, которые через второй диод Шоттки 12 соединены с выходом 13 устройства и коллектором второго транзистора 6, Логическое устройство работает следующим образом.

При подаче на все информационные входы (2) и управляющий вход 9 уровней логической единицы V ток, протекающий через первый резистор 3, поступает на базу второго транзистора 6, вызывая отпирание тиристора, выполненного на первом и втором транзисторах 5 и 6, и втором диоде

Шоттки 12. Ток первого резистора 3 выбирается достаточным для насыщения второго транзистора 6. Таким образом, на выходе 13 устройства устанавливается уровень логического ну6 ля U .,При подаче на управляющийвход 9 уровня логической единицы, а хотя бы на один из информационных о входов 2 уровня логического нуля V многоэмиттерный транзистор 1 насыщается и напряжение на базе второго транзистора 6 падает до величины о

Ч Ч +Ч„.„, где V< < - напряжение между эмиттером и коллектором насы1352! 2

5

f5

50 щенного многоэмнттерного транзистора !. Так как V„

К вЂ” число змиттеров многоэмиттерного транзистора 1.

Если на управляющий вход 9 постуо пает уровень логического нуля V то многоэмиттерный транзистор 1 закрывается при любых потенциалах на информационных входах 2, так как потенциал на его базе Vg Ч +V где V — падение напряжения на открытом третьем диоде Шоттки 10 в то время, как на любом эмиттере многоэмиттерного транзистора 1 потенциал не опускается ниже величины

V поэтому падение напряжения на переходах база-.эмиттер многоэмиттерного транзистора 1 не превьппает величины Ч, что недостаточно для удержания транзистора в открытом состоянии. Тиристор на первом и втором транзисторах 5 и 6 сохраняет то состояние (открытое или закрытое), которое он имел в момент запираиия многоэмиттерного транзистора 1 вследствие уменьшения потенциала

О на управляющем входе 9 до уровня Ч

Третий резистор 6 ограничивает величину тока, протекающего через тиристор в открытом состоянии. Сохранение исходного состояния осуществляется за счет наличия глубокой положительной обратной связи в первом и втором транзисторах 5 и 6.

Таким образом, предлагаемое устройство позволяет записывать при подаче на управляющий вход 9 уровня логической .единицы, инвертированное логическое произведение состояний

213521

Составитель А.Янов

Редактор Н,Гунько Техред Т.Дубинчак Корректор Л.Патай

Заказ 785/60 Тираж 818 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб;, д. 4/5

Филиал ?IIIII "Патент", r. Ужгород, ул. Проектная, 4

3 1 на информационных входах 2 и сохранять его при подаче на управляющий вход 9 уровня логического нуля и выполняет функцию Р-триггера с логикой И-НЕ на входе. При удержании потенциала логической единицы на информационном входе 9 или если этот вход не подключен больше ни к какМм источникам сигнала, предлагаемое устройство функционирует как быстродействующий логический элемент И-НЕ и может быть использовано в любых микросхемах комбинационного типа.

Формула изобретения

Логическое устройство, содержащее управляющий вход, информационные входы, подключенные к эмиттерам мнагоэмиттерного транзистора.и -р-мтипа, база которого подключена к первому выводу первого резистора, база и коллектор первого транзистора р --И-Р-типа подключены соответственно к коллектору и базе второго транзистора и -р-п-типа, коллектор которого соединен с выходом устройства и через второй резистор подключен к шине питания, а эмиттер подключен к общей шине ° эмиттер первого транзистора через третий резистор подключен к шине питания, t0 о т л и ч а ю щ е е с я тем, что, с целью увеличения его быстродействия и уменьшения потребляемой мощности, в него введены три диода

Шоттки, анод первого из которых соединен с базой многоэмиттерного транзистора, катод — с его коллектором, базой второго транзистора и анодом второго диода, катод которого соединен с коллектором второго.

ZO транзистора, катод третьего диода соединен с управляющим входом, а анод — с первым выводом первого резистора, второй вывод которого соединен с шиной питания.