Измеритель отношения амплитуд двух синусоидальных напряжений

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано для измерения амплитудно-частотных характеристик четьгрехполюсников. Цель изобретения - повышение точности измерений. Устройство содержит коммутаторы 1,2 и 4, усилитель 3 с детектором, блок 5 выборки-хранения , дифференциальный усилитель 6, управляемый генератор 7 кодов, источник 8 опорного напряжения , цифроаналоговый преобразователь 9, блок Ю управления, блок 11 оперативнрй памяти, вычислительный .блок 12, входы 13 и 14 и выход 15 устройства. В описании даны математические формулы для определения кодов управляемого генератора кодов, временные диаграммы работы блока 10 управления и приведен пример его реализации . 3 нл. (Л с /

СОЮЗ СО8ЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (И) ol) сю 4 G 01 R 19/10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPGHOMY СВИДЕТЕЛЬСТВУ

Ф

13

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЬГГИЙ (21) 3720537/24-21 (22) 06.01.84 (46) 28.02.86. Бюл. У 8 (72) В.Н.Лукинов и М.А.Стефанович (53) 621 ° 317.661(088.8) (56) Авторское свидетельство СССР

9 834551, кл. G 01 R 19/10, 1979.

Авторское свидетельство СССР и 866489, кл. G 01 R 19/ 10, 1979. (54) ИЗМЕРИТЕЛЬ ОТНОШЕНИЯ АМПЛИТУД

ДВУХ СИНУСОИДАЛЬНЫХ НАПРЯЖЕНИЙ (57) Изобретение может быть использовано для измерения амплитудно-частотных характеристик четырехполюсников. Цель изобретения — повышение точности измерений. Устройство содержит коммутаторы 1,2 и 4, усилитель 3 с детектором, блок 5 выборки-хранения, дифференциальный усилитель 6, управляемый генератор 7 кодов, источник 8 опорного напряжения, цифроаналоговый преобразователь 9, блок 10 управления, блок 11 оперативной памяти, вычислительный .блок 12, входы 13 и 14 и выход 15 устройства. В описании даны математические формулы для определения кодов управляемого генератора кодов, временные диаграммы работы блока 10 управления и приведен пример его реализации. 3 ил.

1215036

Изобретение относится к измерительной технике и может быть использовано для измерения амплитудно-частотных характеристик четырехполюсников.

Цель изобретения — повыпение точности измерения.

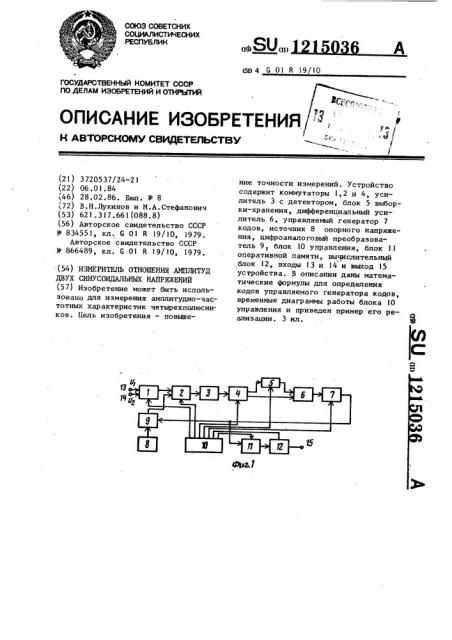

На фиг.! приведена структурная схема устройства, на фиг.2 — пример реализации блока управления; на фиг.3 — временные диаграммы работы блока управления.

Устройство содержит первый 1 и второй 2 коммутаторы, усилитель

3 с детектором, третий коммутатор

4, блок 5 выборки-хранения, дифференциальный усилитель 6, управляемый генератор 7 кодов, йсточник 8 опорного напряжения, цифроаналоговый преобразователь (ЦАП) 9, блок

10 управления, блок 11 оперативной памяти, вычислительный блок 12, первый 13 и второй 14 входы и выход

15 устройства.

Измеряемые напряжения 06 и ц . подаются на входы коммутатора l выход которого соединен с первым входом коммутатора 2, к второму входу которого через ЦАП 9 подключен источник 8 опорного напряжения.

Выход коммутатора 2 через усили- тель 3 с детектором соединен с sxoдом коммутатора 4, первый выход которого через блок 5 выборки-хранения соединен с первым входом дифференциального усилителя 6, а второй выход — с вторым входом последнего.

Выход дифференциального усилителя

6 подключен к первому входу управляемого генератора 7 кодов, выход которого соединен с вторым входом ЦАП 9 и первым входом блока 11 оперативной памяти, причем выход последнего соединен с информационным входом вычислительного блока 12.

Выходы блока 10 управления под-. . ключены к управляющим входам коммутаторов 1,2 и 4, блока 5 выборки-хранения, управляемого генератора 7 кодов, блока 11 оперативной памяти и вычислительного блока 12.

Блок управления содержит 0-триггеры 16 и 17, элементы И 18-20,элементы HE 21-22, 0-триггеры 23 и 24, а также генератор 25 тактовых импульсов.

Устройство работает следующим образом.

Измерение отношения напряжений производится за четыре такта. . В первом такте блок )О управления обеспечивает подключение напряжения U) на вход усилителя 3 с детектором. Результат U< преобразования запоминается в блоке 5 выборки-хранения и определяется выражением

)),=1), „, (1> где К,6 — коэффициент передачи усилителя 3 в первом такте.

При наличии нелинейности ампдитудной характеристики усилителя 3 и неравномерности его амплитудночастотной характеристики коэффициент его передачи является функцией амплитуды и частоты сигнала на входе усилителя 3 к„=к „(1 6,(uÄraÄi), (2)

25 где К „-. номинальное значение коэффициейта передачи усилителя 3, о (О,, ы„ ) - относительная погрешность козффици30 ента передачи усилителя 3 при амплитуде входного сигнала

U и частоте сигнала 4)„.

Во втором такте напряжение Uz

35 источника 8 опорного сигнала с частотой 4), через ЦАП 9 поступает на второй вход дифференциального усилителя 6, на первый вход которого поступает напряжение О, с выхода

40 блока 5 выборки-хранения. Напряжение с выхода дифференциального усилителя 3 при наличии разрешающего сигнала от блока 10 управле45 ния на управляющем входе управляемого генератора 7 кодов производит изменение выходного кода этого блока и, соответственно, коэффициента передачи ЦАП 9 до выравнивания значений напряжений 0 и U на вхо50 1 2i дах дифференциального усилителя 6.

Выходной код И1 управляемого генератора 7 кодов по окончании второго такта запобынается в блоке 11 оперативной памяти. При этом напряжение

О на втором входе дифференциально55 го усилителя б в конце второго такта определяется выражением ц - о к„к „(3) 1215036 где К, — коэффициент передачи ЦАП 9 в конце второго такта.

f«S,(N„ ) (4) = " н C1+ 3 ("о 9 И 1) (5) где N) и Nù — управляющ и код и максимальное значение . кода на входе ЦАП 9;

S

Из выражений (I.)-(5), пренебрегая погрешностью выравнивания напряжений 0,.и 0 можно записать

") (<4(0< ы )1

0, (! (+ )1 (14 3(0 +o)j

В третьем такте производится запоминание в блоке 5 выборки-хранения напряжения U>,являющегося результатом преобразования усилителем 3 напряжения 0, определяемое по аналогии с U выражением

u,=u, К,„(< а,(UÄ „Ц. (7)

В четвертом такте по аналогии с вторым производится уравновешивание этого напряжения и запоминание кода

N в блоке 11 оперативной памяти .

Ю («E,(u,, ы„)

t «3,(М„Ы.11 t«8,((1,,У,13

По окончании четвертого такта вычислительный блок 12 по команде от блока 1О управления проводит вычисле ние отношения кодов Й, и Й, которое с учетом малых значений относительных погрешностей имеет вид

М! 01 г

, p t»" Г4e(.)- („ .)1 (8,(и„,1<,lu„,))-(Бр)u„a,j-6,iu„,))1, (9)

Как следует из выражения (9), первая составляющая погрешности предлагаемого устройства определяется нелинейностью ЦАП 9, которая на фиксированной частоте сигнала может быть сведена с помощью известных технических решений, например . индуктивных делителей, к пренебрежимо малой величине. Вторая и третья составляющие погрешности предлагаемого устройства определяются нелинейностью участка U - 0 амйлитудных характеристик усилителя с детектором на частотах входного M и опорного () сигналов. В соответствии с изложенным выражение (9) можно записать как

0,,(«,S (u,(, .и„) )) ()о)

02 u„)„!

1О . где а3 1 —; — - частотная неравномерность нелинейности амплитудной характеристики усилителя с детектором.

Перегруппировав члены выражения (9), получаем

1 — — «(Р,)и,,и,)-),(u„è.)1 (),(н„и,)2 (12

1О - 8,(0„ы,Я-(R,((j„c „)- R, (0,.c .))) . (1 1 ) Отсюда по аналогии с выражени ем (10) можно записать ц "о 0

3О 4

При отсутствии сигнала "Пуск" на выходе Q триггера 23 формируется сигнал "0", запрещающий работу триггеров 16, !7 и 24. Сигнал "0" с

55 выхода Q триггера 24 формирует на выходах элементов И 18-20 сигнал

"0". При поступлении сигнала "Пуск" на выходе Q триггера 23 появляется

/ 1, 0 1где о ) — 1- отклонение частот ыо () и ной характеристики усилителя с детектором при изменении амплитуды входного сигнала.

З5 Из выражений (10) и (12) следует

r — = — (1 3, (13)

"a

В сравнении со значениями пог решности амплитудной характеристики усилителя с детектором или не45 равномерности его амппитудно-частотной характеристики рассматриваемая погрешность является величиной следующего порядка малости.

Блок управления работает следую5О щим образом.

1215036 сигнал 111", разрешающий формирование выходных сигналов блока управления в соответствии с диаграммой на фиг.3

Выходные сигналы блока управления поступают на обозначенные в скобках блоки измерителя отношения по схеме на фиг.1.

В режиме однофазового измерения отрицательным перепадом сигнала

U 1, с выхода элемента И 19 обеспечиваются перевод триггера 23 в состояние "0 на выходе Q и останов работы схемы.

Блок управления обеспечивает возможность проведения циклических измерений путем подачи, на вход

"Пуск" сигнала 0", непрерывного на время проведения циклических измерений.

Формула изобретения

Измеритель отношения амплитуд двух синусоидальных напряжений, содержащий первый коммутатор, первый и второй входы которого являются соответственно первым и вторым входами устройства, блок управления, первый выход которого подключен к управляющему входу перво1 го коммутатора, вычислительный блок, выход которого является выходом устройства, а первый вход подключен к второму выходу блока управления, источник опорного напряжения, дифференциальный усилитель и усилитель с детектором, о т л и ч а ю щ и й— с я тем, что,с целью повышения точности измерения, в него дополнительно введены второй и третий коммутаторы, блок выборки-хранения, управляемый генератор кодов, цифроаналоговый преобразователь и блок оперативной памяти, причем выход первого коммутатора соединен с nep1ð вым входом второго коммутатора, вто. рой вход которого соединен с выходом цифроаналогового преобразова— теля, к первому входу которого подключен источник опорного напря15 жения, выход второго коммутатора через усилитель с детектором подключен к входу третьего коммутатора, первый выход которого связан с первым входом блока выборки-хра-!

2О нения, выход которого соединен с первым входом дифференциального усилителя, второй вход которого соединен с вторым выходом третьего коммутатора, а выход — с первым входом управляемого генератора кодов, выход которого связан с вторым входом цифроаналогового преобразователя и первым входом блока оперативной памяти, выход которого подключен к второму входу вычислительного блока, третий выход блока управления подключен к управляющему входу второго коммутатора, четвертый — к управляющему входу третьего коммутатора, пятый — к второму входу блока выбор35 ки-хранения, шестой — к второму входу управляемого генератора кодов, а седьмой — к второму входу блока оперативной памяти.

1215036

"е )

4е (цу ие(72) (/el>i

%elle

Составитель В.Савинов

Техред Т. Тулик. Корректор С.Шекмар

Редактор А. Огар

Подписное

Заказ 903/53 Тираж 730

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий!

13035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 дум

Яия

%(r,е,sg ю()

QfrJ

4щю.) йв(у