Устройство для интерполяции

Иллюстрации

Показать всеРеферат

Изобретение предназначено для вычисления значений функции в микропроцессорных системах и может применяться в приборостроении, управляющих и информационно-измерительных системах. Целью изобретения является сокращение объема памяти за счет использования узловых точек функции с произвольным взаиморасположением. Привязка к узловой точке осуществляется путем выполнения процедуры поразрядного поиска адреса. Устройство содержит регистр последовательного приближения адреса, регистр аргумента , блок памяти, триггер, регистр промежуточных значений, три коммутатора и блок умножения. 1 ил. i (Л ю С71

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1215118 (я) 4 С, 06 F 1 5/353

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOIVIV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3692851/24-24 (22) 20.01.84 (46) 28.02.86. Бюл. Ф 8 (71) Ленинградский ордена Ленича электротехнический институт им. В.И.Ульянова (Ленина) (72) А.В,Анисимов, А.В.Крайников, Б.А.Курдиков и В.Б.Смолов (53) 681,32 (088.8) (56) Патент ФРГ В 2853560, кл. С 06. F 15/353, опублик. !981, Патент Великобритании, 9 2010545, кл. G 06 F 15/353, опублик. 1980. (54) УСТРОЙСТВО ДЛЯ ИНТЕРПОЛЯЦИИ (57) Изобретение предназначено для вычисления значений функции в микропроцессорных системах и может применяться в приборостроении, управляющих и информационно-измерительных системах. Целью изобретения является сокращение объема памяти за счет использования узловых точек функции с произвольным взаиморасположением.

Привязка к узловой точке осуществляется путем выполнения процедуры поразрядного поиска адреса. Устройство содержит регистр последовательного приближения адреса, регистр аргумента, блок памяти, триггер, регнстр промежуточных значений, .три коммутатора и блок умножения. I ил.

1215118

Изобретение относится к вычисли тельной технике, предназначено для использования в качестве ацпаратного расширителя в микропроцессорных системах и может найти применеййе в приборострбении, управляющих и информационно-измерительных системах.

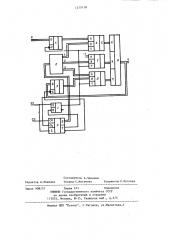

Целью изобретения является упрощение устройства за счет сокращения объема блока памяти, На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит триггер 1, блок 2 памяти, блок 3 последовательного приближения, регистр 4 аргумента, регистр 5 промежуточных результатов, первый, второй и третий коммутаторы 6, 7 и 8 соответственно, блок 9 вычисления функции (Х» у +к).

Устройство работает следующим образом.

Интерполяция функции 1(х), заданной на конечном множестве точек

К, Х, Хэ. ° . Х1, ° .. Х двумя координатами „(X;), F(Z;), производится в соответствии с выражениями следующего вида:

y(x),(Х;)+Г,(Х;) г, (Ч) где

Х;а Хс X,„, (2) Реализация интерполяционных выражений {1)-(3) осуществляется в устройстве:в два такта. Управляющие1 сигналы, формируемые триггером 1 и блоком 3, определяют состояние ре гистров 4 и 5 и коммутаторов 6 - 8 в зависимости от такта работы устройства для интерполяции.

В первом такте производится нахождение номера узловой точки интерполируемой функции и величины 1 вычисляемой в соответствии с формулой (3). Начинается первый такт вычисления при поступлении на вход Сl устройства для интерполяции сигнала начального установа, Триггер 1 устанавливается при этом в единичное состояние, и на информационном вы-» ходе блока 3 формируется начальный код для процедуры поразрядного поиска, Блок 3 реализован на основе ИС

К155ИР17. Начальное значение кода В будет 0111111111111111; Установление григгера 1 в единичное состояние обеспечивает прием кода аргумента X в регистр 4. Синхронизация регистра

40 слагаемого К, 45 Завершается первый такт интерпо50

5

1О t5

4 — динамическая, по положительному фронту импульса на выходе триггера

Единичный сигнал на входах управления коммутаторами 6 — 8 приводит к тому, что на выход С этих коммутаторов поступает сигнал с входа А.

При этом на вход К блока 9 поступает выход регистра 4, в котором записан код аргумента X,,на вход Х блока 9 подается константа — 1, представленная в дополнительном коде, а на вход -У вЂ” значение узловой точки Х, считываемой с выхода блока 2 памяти по адресу» формируемому на информационном выходе блока 3, Процедура поразрядного поиска значения 1 производится в устройстве по методу деления отрезка пополам, т.е. путем нахождения корня уравнения

Х вЂ” Х;=О, (4) в котором в качестве переменной выступает значение X;, считываемое из блока памяти. Процедура поразрядного поиска, значения 1 тактиру-: ется синхроимпульсами С2, поступающими на вход синхронизации блока 3. В качестве результата сравнения величин

Х и Х; в процессе поразрядного поиска величины 1 используется знаковый разряд выхода блока 9. При поступлении каждого текущего синхроимпульса С2 в блоке 3 производится вычисление одного разряда кода 9

В связи с этим длительность первого такта процедуры интерполяции равна количеству разрядов в коде )1, счи-. тываемом с информационного выхода блока 3, умноженном на период следования импульсов С2. В качестве блока 9 удобно использовать матричный умножитель, так как в матричных умножителях имеется свободный вход ляции после получения значения номе- . ра узловой точки t на -информационном выходе блока 3. При этом на выходе управления этого блока появляются прямой сигнал управления, обнуляю-. щий триггер 1, и инверсия этого сигнала, обеспечивающая запись кода 1 с выхода блока 9 в регистр 5. В качестве выхода управления при реализации блока вычисления адреса на основе

ИС К155ИР17 используется выход, непосредственно следующий за информационными. В процессе поразрядного

1215118 поиска на этом выходе устанавливается нулевое.значение, которое и сбрасывает триггер 1.

Во втором такте интерполяции произ- 5 водится собственно вычисление по интерполяционной формуле (!). Управляющий сигнал, поступающий с триггера I, .переводит коммутаторы 6. — 8 в состояние, при котором код с входа В поступает на выход С, При этом на входы К и Х блока 9 поступают интерполяционные коэффициенты F,(Х;) и Г (Х;), считываемые с первого и второго выходов блока 2 памяти по адресу:i вычисленному на первом такте интерполяции. На вход У блока 9 поступает с регистра 5 код i

Процедура вычисления в соответствии с формулой (1)при подаче соответствую †щих аргументов на входы блока 9 не требует каких-либо сигналов управления. В результате выполнения второго такта работы устройства для интерполяции на выходе блока 9 формирует- 25 ся искомое значение интерполируемой функции. б

Формула изобретения

Устройство для интерполяции, содер- З0 жащее блок последовательного приближения, регистр аргумента и блок памяти, причем информационные входы регистра аргумента соединены с входами аргумента устройства, вход запуска устроиства соединен с входом наЭ5 чальной установки блока последовательного приближения, информационные выходы которого соединены с адресными входами блока памяти, а тактовый вход соединен с тактовым входом уст40

poAcTBG отличающееся тем, что, с целью упрощения уст ройства за счет сокращения объема блока памяти, оно содержит триггер, регистр промежуточных результатов, 45 три коммутатора и блок вычисления функции Х У<К, причем вход запуска устройства соединен с входом устаII II и ов к и в 1 триггера, выход которого соединен с управляющими входами первого, второго и третьего коммутаторов и входом синхрониз а ции регис тра аргумента, выходы которого соединены с первой группой информационных входов первого коммутатора, выход которого соединен с К -входом блока вычисления функции X У > К ., выход модуля результата которого соединен с информационным входом регис тра промежуточных результатов, и выходом устройства, а знаковый выход соединен с информационным в ходом блок а последовательного приближения, прямой выход признака приближе нля которого соединен с входом установки в "О " триггера, а инв ерсный выход признака приближения — с входом синхронизации регистра промежу т очных результатов, первая группа информационных входов второго коммутатора соединена с группой входов задания кода " - 1 " ус тр ойс тв а, выход второго коммутатора подключен к -входу блока вычисления функции х - у + V, выходы первого интерполяционного коэффициента блока памяти соединены с второй группой информационных входов первого коммутатора, выходы второго интерполяционного коэффициента блока памяти с оединены с второй группой информационных входов второго коммутатора, выходы кода узловой точки блока памяти соединены с перв ой группой информационных входов третьего коммутатора, выход которого соединен с Я -входом блока вычисления функции М Ч t5, вторая группа информационных входов третьего коммутатора подключена к выходам регистра промежуточных результатов.

1215118

Составитель А.Чеканов

Техред С.Мигунова Корректор О.Луговая

Редактор А.Лежнина

Заказ 908/57

Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., ц,4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная,4