Цифровой накопитель импульсных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использоваи но в различных цифровых измерительных комплексах для вццелення повторяющихся импульсных сигналов из смеси с шумами и другими помехами. Цель и изобретения - повышение быстродейст- : ВИЯ. Устройство содержит аналогоW

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ь»4

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

/ ю;Ф у

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

fl0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3764602/24-21 (22) 05.07.84 (46) 28.02.86. Бюл. 9 8 (72) Ю.Н.Городецкий, Ю.С.Ицкович, Л.В. Казачков, Ю.С.Парижский и А.Н Д1полянскнй (53) 621 . 391 ° 27 2 (088. 8) (56) Лихарев В.А. Цифровые методы и устройства в радиолокации. М.: Советское радио, 1973, с. 108, 109, рис. 2.1,2.

Лезин Ю.С. Оптимальные фильтры и накопители импульснык сигналов . М.:

„„SU„, 121 168 А

Советское радио, 1969, с. 402, 403, рис. 12.3.1. (54) ЦИФРОВОЙ НАКОПИТЕЛЬ ИМПУЛЬСНЫХ

СИГНАЛОВ (57) Изобретение относится к импульсной технике и может быть использовано в различных цифровык измерительных комплексах для выделения повторяющихся импульсных сигналов из смеси с шумами и другими помехами. Цель изобретения †. повышение быстродействия. Устройство содержит аналого12151 цифровой преобразователь 1 с выходным сигналом 20, блок 2 памяти вход1 ных сигналов с сигналами 21 и 22 на его выходах, регистр 3 сдвига, шину 4 логической "1" с сигналом 23, двухвходовые сумматоры 5 и 6 с сигналами 24 и 25 на их выходах, генератор 7 тактовых импульсов с сигналом 17 на его выходе, элемент 8 задержки с выходным сигналом 18, блок 9 сравнения с порогом, регист68 ры ll блока 10 памяти выходных сигналов 26 и 27, блок 12 начальной установки с сигналом 16 на его выходе, резистор 13, конденсатор 14 и ннвертор 15. На информационный вход аналого-цифрового преобразователя 1, являющегося входом накопителя, подается сигнал 19. Выходной сигнал накопителя — 28. В описании приведены временные диаграммы, поясняющие работу накопителя. 2 ил.

Изобретение относится к импульсной технике, в частности к устройст-1 вам преобразования серий импульсных сигналов, и может быть использовано в различных цифровых измерительных комплексах для выделения повторяющихся импульсных сигналов из смеси с шумами и другими помехами.

Целью изобретения является повышение быстродействия.

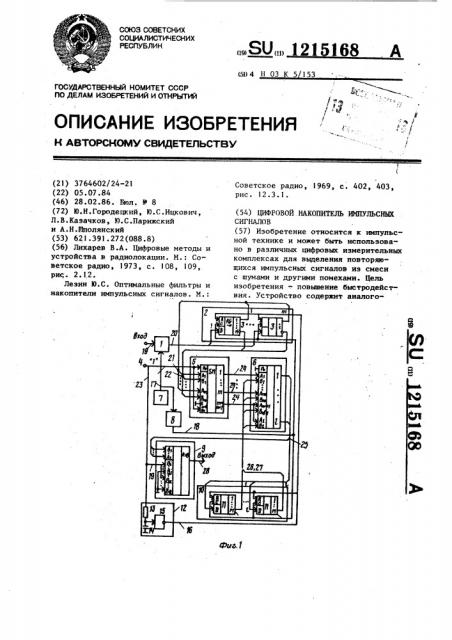

На фиг.l приведена функциональная схема цифрового накопителя; на фиг.2 — временные диаграммы, поясняющие его работу.

Цифровой накопитель импульсных сигналов содержит аналого-цифровой преобразователь 1, блок 2 памяти входных сигналов, регистры 3 сдвига, шину 4 логической "l", двухвходовые сумматоры 5 и 6, генератор 7 тактовых импульсов, элемент 8 задержки, блок 9 сравнения с порогом, например цифровой компаратор, блок 10 памяти выходных сигналов, регистры

ll сдвига, блок 12 начальной установки, резистор 13, конденсатор 14, инвертор 15.

На фиг.2 введены следующие обозначения; 16 — сигнал на выходе блока начальной установки; 17 - тактовая последовательность на выходе генератора 7 тактовых импульсов; 18тактовая последовательность на выхо" де,, элемента 8 задержки; )9 - сигнал на входе накопителя; 20 - сигнал на выходе аналого-цифрового преобразователя; 21 — сигнал на первом выходе блока 2 памяти входных сигналов, 22 — сигнал на втором выходе бло10

30 дов каждый (М вЂ” число каналов, n—

Ф число накапливаемых импульсов ). Общее число регистров 3 сдвига составляет m и равно разрядности аналого" цифрового преобразователя 1. Тактовые входы регистров 3 сдвига объединены и подключены к выходу элемента 8 задержки, Входы начальной установки регистра 3 сдвига объединены и подключены к выходу блока 12 начальной установки.

Первый выход блока 2 памяти входных сигналов, образованный прямыми выходами первых разрядов регистров

3 сдвига, и второй выход блока 2, образованный инверсными выходами последних разрядов регистров 3 сдвига, соединены соответственно с. первым и вторым входами (входами первого и второго операндов) сумматора 5. Вход переноса в младшие разряды сумматора

2 ка 2 памяти входных сигналов;

23 — сигнал на шине 4 логической

"1", 24 — сигнал на выходе сумматора 5; 25 — сигнал на выходе сумматора 6.; 26 — сигнал в первых разрядах регистров 11 сдвига блока 10; 26сигнал на выходе блока 10 памяти выходных сигналов; 28 — выходной сигнал накопителя.

Информационный вход аналого-цифрового преобразователя 1 является входом накопителя, его тактовый вход соединен с выходом генератора 7 тактовых импульсов и с входом элемента 8 задержки, а выход — с информационным входом блока 2 памяти входных сигналов. Регистры 3 сдвига блока 2 памяти имеют по Н Мх п+1 разря1215168

5 обьединен r (и+! ) -м (знаковым) разрядом второго операнда и подключен к шине 4 логической "1", а (m+1) -й (знаковый) разряд первого операнда подключен к нулевой шине.

Такое включение сумматора 5 обеспечивает использование его в ка;честве вычитающего блока, когда первый операнд является положительным числом, а второй операнд — отрицательным числом. Выход сумматора

5 соединен поразрядно (с 1-го по (ш+1) -й разряды) с первым входом

1 -разрядного сумматора 6. В сумматоре 6 старшие разряды первого операнда, начиная с (m+1) -ro разряда, объединены, а вход переноса в младший разряд подключен к нулевой шине. Такое включение является естественным (следует непосредственно из правила двоичной арифметики) при суммировании двух операндов, первый из которых знакопеременный и имеет меньшую разрядность, чем второй (т.е. первое слагаемое меньше по абсолютной величине), а второй операнд всегда положителен. Второй вход сумматора подключен поразрядно к выходу блока 10 памяти выходных сигналов образованному прямыми выходами последних разрядов регистров 11 сдвига, а выход — к информационному входу блока 10 и к первому входу блока 9 сравнения с порогом. Регистры 11 сдвига блока 10 памяти выходных сигналов имеют по М разрядов каждый, а их общее число составляет 8 и равно разрядности сумматора 6. Тактовые входы регистров 11 сдвига объединены и подключены к выходу элемента 8 задержки. Входы начальной установки регистров 11 сдвига объединены и подключены к выходу блока 12 начальной установки. В последнем резистор 13 и конденсатор 14 включены последовательно между шиной 4 логической "1" и нулевой шиной, образуя . времязадающую цепь, к которой подключен выходной инвертор 15. Разряды второго входа блока 9 сравнения подключены к шине 4 логической "1" и к нулевой шине в соответствии с требуемым значением порога. Выход блока 9 сравнения является выходом накопителя.

Данное устройство выполняет накопление импульсных сигналов в одном (г-м) канале (элементе дальности) и

/ последующее сравнение накопленного сигнала с порогом в соответствии с правилом накопления на скользящем интервале

5 Н-1 (.1)

i-o где n — число накапливаемых импульt0 сов (ширина скользящего интервала); х - квантованные по амплитуде к-i и времени значения входного сигнала, задержанные на i

)5 (г) тактов; у — квантованные по амплитуде к и времени значения выходного сигнала; с - цифровой порог.

Для пояснения принципа работы накопителя применяем правило накопления на скользящем интервале в г-м канале. Запишем выражение или k-ro u (k-1)-го периодов работы:

П-1 () с — () () „(t),, (М, о)

Ук Z x -, к z.1 к w+t к и+! Р

1 (2.)

Ь-1. () X() (С ) + X() + X () +X(t ) 30 1 -1 — "„1 " -1+ .-a " r- + к-

i=o

Вычитая у „ из у„ и переноса () ) ()

К-1 у(") в правую часть, получим посВе приведения подобных членов рекурентное правило работы накопителя в г-м канале

I а

40 Принцип работы накопителя в соответствии с выражением(4 ) поясняется на примере его функционирования при конкретных значениях числа каналов

М=4 и числа накапливаемых импульсов

45 И=3. Указанному примеру соответствуют и временные диаграммы на фиг.2, причем на временных диаграммах значения сигналов на всех информационних цифровых многоразрядных входах и выходах (двончные многоразрядные числа) представлены условно в виде импульсов с амплитудой, пропорциональной величине соответствующих сигналов. Для определенности вре55 eeHHve диаграммы приведены для слу чая, когда на входе накопителя действует сигнал, соотгетствующий наличию трех импульсов в первом и третьl2!5168 ем каналах, причем амплитуды импульсов в каждом из каналов составляют соответственно три и одну условную единицы.

После включения питания накопитель автоматически приводится в исходное положение, при котором регистры 3 и 11 сдвига блоков 2 и 10 памяти сброшены в нулевые состояния. Сиг- 10 нал сброса вырабатывается блоком 12 начальной установки следующим образом.

Конденсатор 14 блока 12 до включения .питания разряжен. В момент включения питания напряжение на конденсаторе не изменяется скачком, поэтому на входе инвертора 15 оказывается уровень логического "0", а на .eI o выходе — уровень o» ической "1" °

По мере заряда конденсатора 14 через резистор 13 напряжение на конденсаторе растет и через время, определяемое постоянной времени заряда времязадающий цепи, достигает уровня, при котором инвертор переходит из единичного в нулевое состояние. В результате на выходе блока 12 начальной уста" новки оказывается сформированным положительный импульс (16 на фиг.2), который поступает на входу начальной установки регистров 3 и 11 сдвига и устанавливает их в нулевое состояние.

Входной сигнал (19 на фиг.2) по- 35 ступает на информационный в:-.од аналого-цифрового преобразователя 1, на тактовый вход которого поступают импульсы с выхода генератора 7 тактовых импульсов (17 на фиг.2) с .пери 40 одом, равным длительности накапливаемых импульсов. Проквантованный по амплитуде и времени сигнал 20 фиг.2 ), представленный двоичным

45 и -разрядным кодом, с выхода аналогоцифрового преобразователя 1 поступает поразрядно в регистры 3 сдвига блока 2 памяти входных сигналов, на тактовые входы которых с выхода элемента 8 задержки поступает после. »О довательность импульсов сдвига (18

Т Т на фиг.2) с периодом T« = определяющим время обработки одного канала (T - период следования входных импульсов в каждом из каналов). Отсчеты входного сигнала, относящиеся к смежным каналам, оказываются всегда в смежных разрядах регистров 3 сдвига и последовательно продвигаются в них. Так как число разрядов регистров 3 сдвига составляет N = M « и+1 = 13, то полностью хранится информация о входном сигнале в и (трех)предьщущих периодах всех М (четырех) каналов и очередное значение обрабатываемого канала.

Как видно из изложенного B первом и последнем разрядах регистров 3 сдвига находится информация, относящаяся к одному и тому же обрабатываемому в данном такте каналу, причем в первых разрядах это х ("» = х, а в последних разк (» к

РЯДах — хк = х „.> . Указанные значения входного сигнала поступают одновременно в сумматор 5, при" чем х(, — в прямом коде, а х(„ (i» (1» в обратном коде 121 и 22 на фиг.2), так как х„ подается с инверсных выходов последних разрядов регистров 3 сдвига. Обратный код числа х „ вместе с сигналом логической (М

"1", подаваемой в сумматор 5 с шины 4 логической "1" (23 на фиг.2), образует дополнительный код числа х так, что на выходе сумматора 5 (e» оказывается число, равное разности х(— х("» = х(1 - х() (24 к к» к к-3 фиг.2). Это число поступает в сумматор 6, на второй вход которого одновременно подается предыдущее значение выходного накопленного сигнала обрабатываемого канала у(к» =у(, с выходов последних разрядов регистров 11 сдвига блока 10 памяти (17 на фиг.2). После суммирования на выходе сумматора 6 образуется положительное число, представляющее накопленное значение выходного сигнала обрабатываемого канала у „"1=

= ук, которое поступает на вход блока 9 сравнения с порогом и на вхо" ды регистров 11 блока 10 памяти выходных сигналов. Значение у(к » сравнивается с порогом, величина которого в виде двоичного числа постоянно действует» на втором входе блока

9 (25 на фиг.2). При превышении выходным сигналом у (" порога на выхок де накопителя появляется нормированный по амплитуде импульс, наличие которого свидетельствует об обнаружении накопленного сигнала в данном канале (28 на фиг.2). При поступ12! 5168 ленин очередного импульса сдвига чис(1} ло у „записывается в первые разряды регистров 11 сдвига блока О памяти (26 на фиг.2), очередное значение входного сигнала записывается в первые разряды регистров 3 сдвига блока 2 памяти, вся информа ция в регистрах 3 и 1! сдвигается на один разряд, и накопитель переходит к обработке второго канала.

Ровно через четыре такта сдвига, т.е. через время Т, равное периоду следования импульсов, когда накопитель вновь будет обрабатывать первый канал в (k+I)-м такте, число у1„ 1 окажется в последних разрядах регистров 11 сдвига, так как число разрядов регистров 11 равно числу каналов M=4.

В процессе накопления п импульсов в смежных периодах накопленный сигнал может оказаться в и раз больше входного сигнала, поэтому разрядность чисел для его представления должна быть на ) Log n ((! ° !" — обозначение ближайшего целого числа, большего или равного самому числу) больше разрядности входного числа, чтобы исключить возможность переполнения разрядной сетки. Это достигается выбором числа регистров 1! сдвига, равным У ш + j 2og n f, и соответствующей разрядностью сумматора 6.

Формула изобретения

Цифровой накопитель импульсных сигналов, содержащий аналого-цифровой преобразователь, информационный вход которого является входом накопителя, тактовый вход соединен с выходом генератора тактовых импульсов, а выход — с информационным вхо1 дом блока памяти входных сигналов, состоящего из м регистров сдвига с объединенными тактовыми входами, образующими тактовый вход блока, и блок сравнения с порогом, выход которого является выходом накопителя, отличающийся тем, что, с целью повышения быстродействия, в него введены первый сумматор, второй сумматор, блок начальной установки, элемент задержки и блок памяти ьыходных сигналов, состоящий из < = w+37og n)H -разрядных регистров сдвига с объединенными такто1О выми входами и входами начальной установки, образующими соответственно тактовый вход и вход начальной установки блока, где М вЂ” число каналов, — число накапливаемых

15 импульсов, j Xog e(— ближайшее число, большее или равное fog h, при этом регистры сдвига блока памяти входных сигналов выполнены М х 1 + 1разрядными, а их входы начальной

2р установки объединены и образуют вход, начальной установки блока, а первый и второй его выходы, образованные соответственно прямыми и инверсны.ми выходами первых и последних раз25 рядов регистров сдвига, подключены соответственно к первому и второму

: входам первого сумматора, вход пе реноса младшего разряда которого подключен к шине логической "1", а выход — к первому входу второго сум-. матора, второй вход которого соединен с выходом блока памяти выход-. ных сигналов, образованным прямъии выходами последних разрядов регист" ров сдвига блока, информационный его вход соединен с входом блока сравнения с порогом и с выходом вто" рого сумматора, тактовые входы блоков памяти входных н выходных сиг4О налов подключены к генератору тактовых импульсов через элемент задержки, а вход начальной установки блоков

Ф

-памя ти в ХОдных и выходных с игналоВ к выходу блока начальной установки, 45 вход которого соединен с шиной логической "1", причем разряды порогового сигналы блока сравнения с порогом подключены к шине логической "1" и Ьулевой шиg!! не.

1215168

По

Фиг.2

Составитель Е. Суров

Редактор М.Келемеш Техред О.Неце Корректор И.Муска

Заказ 911/59 Тираж 818 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Г

Филиал ППП "Патент", г.Ужгород, ул.Проектная, 4