Регистратор

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и может быть использовано в регистрирующих приборах непрерывной записи, например осциллографах с памятью, регистраторах аварийных процессов и т.д.. Цель изобретения - повьшение точности регистрации, снижение требований к точности цифроаналогового преобразователя (ЦАП) и упрощение его конструкции. Регистратор содержит ЦАП 1, компаратор 2, клеммы 3, элементы 4-7 памяти, счетчик 8 адреса , формирователь 9 импульсов, регистр 10 сдвига, генератор II тактовых импульсов, резисторы 12-15, клемму I6 управления, источники 17 и 18 единичного и нулевого сигналов соответственно, элементы ИСКПКН ЧАЮЩЕЕ ИЛИ 19-21. В регистраторе заложена логика метода поразрядного уравновешивания. Погрешность веса каждого разряда учитывается выбором веса последующих младших разрядов , при этом вес последнего младшего разряда может быть сколь угодно малым и определяется требованиями к разрешающей способности регистратора . I ил.

СО1ОЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (191 (И) (51) 4 G 01 D 9/12

КГСО1()Щ Л

13,",. .13

liMMN8 =: яi.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 3766811/24-10 (22} 30.05.84 (46) 07.03.86. Бюл. Р 9 (.71) Всесоюзный научно-исследовательский, проектно-конструкторский и технологический институт силовых и полупроводниковых устройств

"ВНИИпреобразователь (72) В.А. Мнзев (53) 53.087.61,(088.8) (56) Калоянов С, Устройство за запис на бързи процессы. Радио, телевизия, электроника. 1982, Р 8, с. 21.

Промышленный каталог.

УДК 621.317.757, Япония, ПК 20532-75.

Transient Time Converter, Riken

Denshi С„, Ltd. с. 18-20. (54) РЕГИСТРАТОР (57) Изобретение относится к измерительной технике и может быть иснользовано в регистрирующих приборах непрерывной записи, например осциллографах с. памятью, регистраторах аварийных процессов и т.д..

Цель изобретения — повышение точности регистрации, снижение требований к точности цифроаналогового преобразователя (ЦАП) и упрощение

его конструкции. Регистратор содер» жит ЦАП 1, компаратор 2, клеммы 3, элементы 4-7 памяти, счетчик 8 адреса, формирователь 9 импульсов, регистр 10 сдвига, генератор 11 тактовых импульсов, резисторы !2-15 клемму 16 управления, источники 17 и 18 единичного и нулевого сигналов соответственно, элементы ИСКЛЮ

ЧАЮИЕЕ ИЛИ 19-21. В регистраторе заложена логика метода поразрядного уравновешивания. Погрешность веса каждого разряда учитывается выбором веса последующих младших разрядов, при этом вес последнего мпа шего разряда может быть сколь угодно малым и определяется требованиями к разрешающей способности регистратора. I ил.

12!6652 2

Изобретение относится к измерительной технике и может быть использовано в регистрирующих приборах непрерывной записи, например осциллографах с памятью, регистраторах аварийных процессов и т.д.

Цель изобретения — одновременное повышение точности регистрации, снижение требований к точности цифроаналогового преобразователя и упрощение.

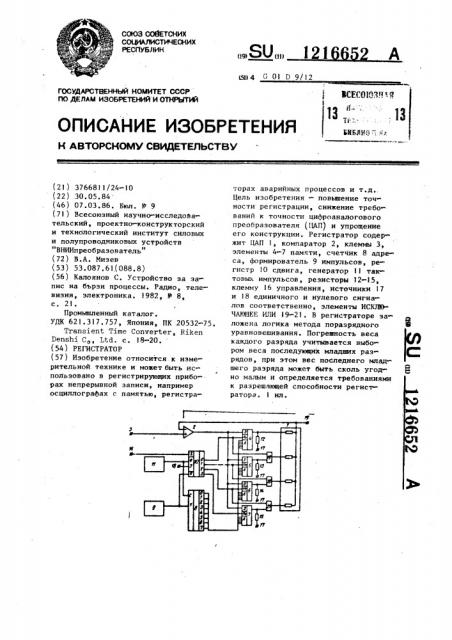

На чертеже изображен предлагаемый регистратор.

Регистратор содержит цифроаналоговый преобразователь (ЦАП) 1, компаратор 2, адин вход которого соединен с входной клеммой 3, а второй вход комнаратора 2 — с выходом

UAH 1, элементы 4-7 памяти, счетчик 8 адреса, выходы которого со.единены с адресными входами элемен.тов 4-7 памяти, формирователь 9 импульсов, регистр 10. сдвига, выход формирователя 9 импульсов соединен с входом разрешения счетчика 8 адреса и входом установки в единицу регистра 10 сдвига, генератор 11 тактовых импульсов, выход которого соединен с тактовыми входами формирователя 9 импульсов, счетчика 8 адреса и регистра 10 сдвига, вход старшего разряда ЦАП 1 подключен к выходу соответствующего элемента 4 памяти, резисторы 12-15, входную клемму 16 управления, соединенную с входом установки в ноль регист ра 10 сдвига, источник 17 единичного сигнала и источник 18 нулевого сигнала, элементы ИСКЛИЧАИЩЕЕ ИЛИ 19 21. !

Входы элементов 4-7 памяти соединены вместе и. подключены к выходу комнаратора 2, первый выход регистра 10 сдвига подключен к входу "Запись-чтение" элемента 4 памяти старmего разряда, остальные выходы регистра 10 сдвига подключены к соответствуюпрпч входам "Запись-чте.ние" .элементов 5-7 памяти младших разрядов, выходы элементов 5-7 памяти через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ !92.1 подключены к соответствующим разрядам IQUI 1, оставшийся вход каждого элемента ИСКЛИЧАНЩЕЕ ИЛИ 19-21 соединен с входом "Запись-чтение" элементов 6, 5 и 4 памяти предыдущего старшего разряда соответствен= но, выходы элементов 4-7 памяти че45

5О

Сигнал "0" с первого выхода регистра 10 сдвига переводит элемент 4 памяти в режим "Чтение" и на его выходе появляется результат сравнения веса старшего разряда ЦАП 1 с величиной аналогового сигнала на клемме 3. Далее ИСКЛ10ЧАИЩЕЕ ИЛИ 19 переводится сигналом "0" в режим

t! !! !! !! по в торит еля и 1 с выхода эл емен та 5 памяти поступает на вход

ЦАП 1 . Выходное напряжение ЦАП вновь сравнивается с ан ал о г овым сигналом компар а то ром 2, результат сравнения с е го выхода подается на элементы 4-7 памяти (эл емен т 4 и арез резисторы 12-15 соединены с источником 17 единичного сигнала, -вход регистра 10 сдвига соединен с источником 18 нулевого сигнала, 5 -вькод ЦАП 1 подключен к выходной клемме 19, Предлагаемый регистратор работает следующим образом, В режиме записи на входную клем-! м му 3 подается регистрируемый сигнал, а на клемму управления-сигнал Лог. 0".

Формирователь 9 импульсов сигналом "!" устанавливает выходы !

5 регистра сдвига в 1 и открывает вход разрешения счетчика 8 .адреса.

При этом сигнал генератора тактовых импульсов 11 устанавливает на выходе счетчика 8 адреса код ад20 реса, котОрый поступает на.адресные входы элементов 4-7 памяти.

Сигнал "!" с выходов регистра 10 сдвига поступает на вход "Запись-!! чтение элементов 4-7 памяти, пе25 реводит нх в режим Запись". На выходах зажимах элементов памяти устанавливается "1" через резисторы 12-15 источником )7 единичного сигнала. На вход ЦАП 1 поступает код !000, его выходное напряжение сравнивается с входным аналоговым сигналом компаратором 2, результат сравнения подается на элементы 4 -7 памяти и запоминается в них. По

35 окончании сигнала "1" на выходе формирователя 9 импульсов, регистр 10 сдвига разблокируется и с приходом очередного сигнала генера-. тора 11 тактовых импульсов на первом выходе регистра 10 сдвига появляется "0", подаваемый на его вход источником 18 нулевого сигнала. мяти переведен в режим ."Чтение" и не воспринимает входной сигнал) .

Очередной сигнал генератора 11 тактовых импульсов записывает "0" на второй выход регистра 10 сдвига, при этом элемент 5 памяти переводится -в режим "чтение", а ИСКЛЮЧАЮ

ЩЕЕ ИЛИ 20 в "Повторитель". Результат сравнения двух старших разрядов ЦАП сохраняется .в элементах 4 и 5 .памяти, "1" с выхода элемента 6 памяти через ИСКЛЮЧАЮЩЕЕ

ИЛИ 20 поступает на вход третьего разряда ЦАП 1, а на первый и второй разряды подают содержимое элементов 4 и 5 памяти.

Выходной сигнал на выходе ЦАП сравнивается с аналоговым сигналом компаратором 3, результат сравнения запоминается в элементе 6 памяти, Последующие разряды ЦАП последовательно сравниваются с аналоговым сигналом, а результаты за-. носятся в элементы памяти младших разрядов. После того, как все выходы регистра 10 сдвига установлены в "0", преобразование завершено.

В элементах 4- 7 памяти хранится,код числа, уравновешивающего весами разрядов ЦАП входной аналоговый сигнал °

Новый цикл преобразования наступает после подачи очередного сигнала "1" формирователем 9 импульсов на вход разрешения счетчика 8 адресов; который увеличивает код адреса на единицу, В процессе записи происходит циклическое изменение содержимого счетчика адреса 8 от 0 до переполнения, при этом также циклически сменяется информация в ячейках элементов 4-7 памяти. Прекращение регистрации сигнала и его воспроизведение происходит после подечи "1" на клемму 16 управления, при этом выходы регистра 10 сдвига блоки руются в состоянии "0".

Сигналы "0" с выходов регистра переводят элементы 4-7 памяти в режим "Чтение", а элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 19-21 в режим "Повторителя".

Сигналы формирователя 9 импульсов и генератора 11 тактовых импульсов поочередно в том же порядке, что и при записи, производят сиену кодов адреса на выходе счетчика 8 адреса,, в результате чего на выходах элементов 4-7 памяти поочередно устанав .

216652 4

35

45 дом формирователя импульсов, гене50

5 !

О !

25 ливаются коды аналоговых сигналов, хранимые в элементах 4-7 памяти.

ЦАП 1 по кодам с выходов элементов .4-7 памяти формирует значения аналоговой величины, воспроизводя записанную аналоговую величину во времени. Поскольку ЦАП 1 участвует в аналого-цифровом, а потом он же и в.цифроаналоговом преобразовании, то, в общем случае, конкретная величина веса каждого разряда не имеет существенного значения, а только важно ее постоянство в течение времени между записью и воспро- . изведением. Однако поскольку в предлагаемом регистраторе заложена логика метода поразрядного уравновешивания, то необходимым условием нормальной работы является требование, чтобы вес каждого разряда был не больше, чем сумма веса последующих за ним младших разрядов с учетом возможных разбросов веса старшего и младших разрядов.

Таким образом, погрешность веса кажд -го разряда учитывается выбором веса последующих младших разрядов, при этом вес последнего младше го разряда может быть сколь угодно малым, и определяется требованиями к разрешающей способности регистр» ратора.

Формула изобретения

Регистратор, содержащий компара» тор, первый вход которого соединен с входной клеммой, а второй — с выходом цифроаналогового преобразователя, элементы памяти, адресные входы которых соединены с выходами счетчика адреса, вход "Разрешение" которого соединен с входом установки в "1" регистра сдвига и с выхоратор тактовых импульсов,- соединенный с тактовыми входами счетчика адреса и регистра сдвига, входная, клемма управления соединена с вхо дом установки в "0" регистра сдвига, резисторы, источник единичного сигнала, источник нулевого сигнала, отличающийся тем, что, с целью повышения точности регистрации, в него введены элемен гы HCKJ!!0ЧАЮЩЕЕ ИЛИ, причем входы элементов памяти соединены вмест и подключены к выходу компаратора, второй

l2I6652

Составитель Н. Ланьков

Редактор И. Дербак Техред А.Бабинец Корректор И. Эрдейи

Заказ 994/52 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и.открытий

113035, Иосква, Ж-35, Раушская наб,,д..4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 вход которого соединен с выходной клеммой, выходы регистра сдвига подключены к входам "Запись-чтение" элементов памяти и, кроме младшего разряда, к первыч входам элементов

ИСКЛИЧАЮЩЕЕ ИЛИ, выход элемента памяти старшего разряда соединен иа прямую с первым входом цифроаналогового преобразователя, а выходы остальных элементов памяти через вторые входы элементов ИСКЛИЧА0Т ЕЕ ИЛИ соединены с остальными входами цифроаналогового преобразователя.