Демодулятор сигналов с фазоразностной модуляцией

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и обеспечивает повьшение помехоустойчивости . N канальных сигналов , поступающих на вход демодулятора , отличаются только фазой fK . Из суммарного сигнала выделяется канальный сигнал, частота которого совпадает с частотой генератора опорных сигналов (ГОС)7 . Блок 2 синхронизации определяет моменты смены фазы во входном сигнале. Его импульсы, соответствующие границам посылок, поступают на тактовый выход демодулятора , на синфазные и квадратурные подканалы (ПК) 4,8 и 3,9 и на формирователь 3 импульсов, импульсы которого поступают на управляющие входы ПК 4,8 и 5,9. Входной групповой сигнал через распределитель 1 мощности поступает на сумматоры мощности (см) 21 и 22 подканалов 4 и 8 непосредственно,а на СМ 21 и 22 подканалов 5 и 9 - через соот- О ветствующие фазовращатели на 90 6 и 10. На другие входы СМ 21, 22 поступают колебания ГОС 7, причем на СМ 21 опорные колебания проходят чекл ff

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТ ИЧЕСНИХ

РЕСПУБЛИН

glPP(8)%gq Yt r

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3785244/24-09 (22} 28.08.84. (46) 07.03.86. Бюл. У 9 (.?1) Одесский электротехнический институт связи им. А.С.Попова (72) А. Г.Лашко, Т.В.Макаров, А.Л.Отливанский, Ю.А.Павличенко и Л.М.Рахович (53) 621.394.62(088.8) (56) Заездный А.М. и др. Аппаратура передачи дискретной информации

МС-5, М.: Связь, 1970, -с.- 17.

Авторское свидетельство СССР

В 946007, кл. Н 04 L 27/22,,1980. (54) ДЕМОДУЛЯТОР СИГНАЛОВ С ФАЗОРАЗ НОСТНОЙ МОДУЛЯЦИЕЙ (57) Изобретение относится к радиотехнике,и обеспечивает повьппение помехоустойчивости. N канальных сигналов, поступающих на вход демодулятора, отличаются только фазой Т„ . Из

ÄÄSUÄÄ 121 8 4 A

1511 с Н 04 L 27/22 суммарного сигнала выделяется канальный сигнал, частота которого совпадает с частотой генератора опорных

=игналов (ГОС) 7.. Блок 2 синхронизации определяет моменты смены фазы во входном сигнале. Его импульсы, соответствующие границам посылок, поступают на тактовый выход демодулятора, на синфазные и квадратурные подканалы (ПК} 4,8 и 5,9 и на формирователь 3 импульсов, импульсы ко" торого поступают на управляющие входы ПК 4,8 и 5,9. Входной групповой сигнал через распределитель 1 мощности поступает на сумматоры мощности (СМ) 21 и 22 подканалов

4 и 8 непосредственно,а на СМ 21 и

22 подкананов 5 и 9 — через соото ветствующие фазовращатели на 90

6 и 10. На другие входы СМ 21, 22 поступают колебания ГОС 7, причем на и с

CM 21 опорные колебания проходят чеl

12 реэ фазовращатель на 180 23. Кроме того, колебания с ГОС 7 на дополнительные синфазный и квадратурнь»й ПК 8 и 9 поступают через переключатель ll мощности, управляемый импульсам с формирователя 3 импульсов. В результате опорные колебания на них проходят либо непосредственно,либо через фазовращатель на

180 12, т.е. нри нечетных посылках

16834 изменяется знак у проекций канального сигнала., С ПК 4 и 5 сигналы поступают на сумматор 13, а с IIK 8 и

9 — на сумматор 14, С сумматорон 14 сигналы поступают на компаратор 15.

Знаки напряжения на выходе компаратора 15, т.е. на информационном выходе демодулятора, соответствуют знакам символов переданной информации. 4 з.п. ф-лы. 1 ил.

Ф

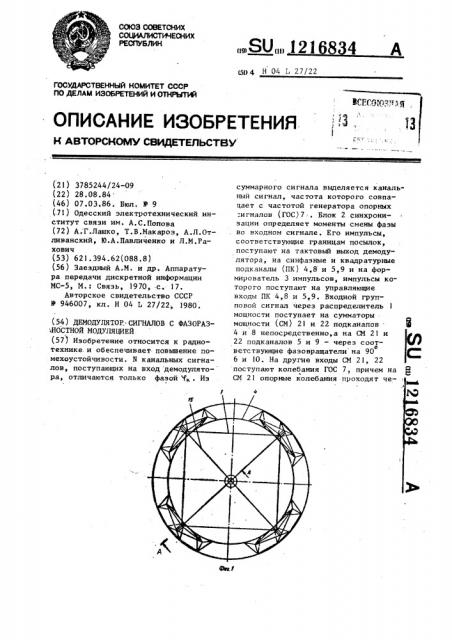

Изобретение относится к радиотехнике и может быть использонано для детектирования многочастотных взаимоортогональных сигналов, Цель изобретения — повышение помехоустойчивости. .На чертеже изображена структурная электрическая схема предложенного демодулятора.

Демодулятор сигналов с фаэоразностной модуляцией содержит распределитель I мощности, блок 2 синхронизации, формирователь 3 импульсов, основной синфаэный подканал 4, основной квадратурный подканал 5, о первый фазовращатель на 90 6, генератор 7 опорных сигналов, дополнительный синфазный подканал 8, дополнительный квадратурный подканал 9, второй фазовращатель на 90

10, переключатель 11 мощности, фазо.б вращатель на 180 12, первый и второй сумматоры 13 и !4, компаратор 15>

Каждый основной .и дополнительный синфазный и квадратурные под— каналы содержат первый и второй детекторы 16 и 17, разностньп» интегратор 18, вычитатель 19, блок

20 памяти, первый и второй сумматоры 21 и 22 мощности, фазовращатель

23, выпрямитель 24. Каждый детектор одержит первый и второй конденсаторы 25 и 26 и диод 27.

Разностный интегратор 18 содер— жит транзистор Р -и- р 28, первый и второй резисторы 29 и 30, переключатель 31 тока заряда, повторитель

32 напряжения, ключ 33 сброса, интегрирующий конденсатор 34,транзистор -p- » 35. Формирователь импульсов содержит инвертор 36, перг

2 ный и второй ждущие мультивибраторы 37 и 38, делитель 39 частоты .

Вычитатель содержит сумматор 40 и инвертир 41.

Демодулятор работает следующим образом.

На вход демодулятора поступает групповой сигнал $ (4 ), который представляет собой сумму И каналь l0 ных сигналов. Каждый из канальных сигналов имеет частоту 0)к, амплитуду Я и фазу . Посылки канальных сигналов разл»лчаются между собой только фазами 1, поэтому

l5 фазы канальных сигналов будем обозначать „, где индекс » означает

Ъ номер посылки.

С учетом вышеуказанного групповой сигнал íà и-ой посылке Sq(t)

20 можно записать как сумму

Я„(Е1= 5 sin(u3

Демодулятор выделяет иэ этой суммы один канальный сигнал, частота которого совпадает с частотой гене— ратора 7 опорных сигналов )о данного демодулятора.

Блок 2 синхронизации выявляет границы посылок группового сигнала, т.е. моменты смены фазы. В соответствии с выявленными .границами посылок формирователь 3 импульсов выра35 батывает последовательность управляющих импульсов,.поступающих на управляющие входы синфазных и кнадратурных подканалон 4, 8 и 5, 9 демодулятора. При этом сначала пода40 ется импульс от блока 2 синхрониза121б

10 а напряжение на выходе сумматора 21 мощности равно разности

S, (t) — Я, (), так как групповой сигнал на вход сумматора 21 мощности поступает в противофазе.

В результате детектирования этих сигналов на детекторах 16 и .17 -появится ток I через резистор. 29 и ток через резистор 30 разностного ции, соответствующий. границе меж— ду посылками. Во время действия этого импульса. происходит запись в блок

20 памяти. результата обработки очередной посылки из разностного 5 интегратора 18. Одновременно срабатывает ждущий мультивибратор 37, которь)й подключает переключатель 31 тока заряда к. заземленной шине.

Задний фронт импульса.от блока 2 синхронизации через.инвертор Зб запускает ждущий мультивибратор 38, который замыкает ключ 33 сброса и происходит разряд интегрирующего конденсатора 34. После возврата в исходное состояние ждущего мультивибратора 38 и ключа 33 сброса возвращается в исходное состояние ждущий мультивибратор- 37.и переключатель 31 тока заряда. Начинается обработка следующей сигнальной посылки. Длительность неустойчивого состояния.ждущего мультивибратора 37 выбрана равной длительности защитного промежутка, причем длительность g5 посылки равна сумме интервала ортогональности группового сигнала и длительности защитного промежутка.

Поэтому длительность заряда интегрирующего конденсатора 34 равна интервалу ортогональности.

Входной многочастотный групповой сигнал поступает также через распределитель 1 мощности на входы сумматоров 21 и 22 мощности, на другие входы которых поступает колебание от генератора 7 опорных сигналов, причем фаза опорного колебания на первом входе сумматора 21 мощности отличается на 180 от фазы этоro о колебания на втором входе суммато- . ра 22 мощности.

На выходе сумматора 22 мощности будет сумма группового сигнала

Sc(t) и опорного колебания Sî(t)=

=S sin<3 t, т. е.

Ф

+ "с() 834 4 интегратора 18. Низкочастотные составляющие этих токов при выполнении условия, что амплитуда опорного колебания значительно больше групповоro сигнала, равны

I,=.— " "(.s (8,+s,), s (<) s .(e.)1, К2Ч где о(u P — коэффициенты, зависящие ! от характеристик диода 27, а Б и

S — амплитуды группового сигнала о и опорного колебания.

) налогично ток Iz равен 2=- — (d.,(SC+S.)-P а. () S.(t) j. ьо

В этих выражениях знак минус для тока

Т определяется направлением включения диода 27, а знак минус перед вторым членом этого выражения определяется тем, что на первый вход сумматора 21 мощности опорное колебание подается в противофазе по сравнению с опорным колебанием на втором входе сумматора 22 мощности.

Ток заряда I интегрирующего.конденсатора 34 практически равен сумме токов Х1 и 1, т. е.

ic. I„+12= Ьс 5О

) 2 ()) + + )Я() Б )

Учитывая, что S » S и обозначая

ы м ьЫ 6, Ь Ь

+ т а и запишем

I,= — „s.+ — s,(t) к(), дс

Этот ток заряжает. интегрирующий конденсатор 34 в течение интервала ортогональности Т, который определяется состоянием переключателя 31 тока заряда. Напряжение U на интerс рирующем конденсаторе 34 в конце заряда будет т — с 5(aoL s,+)) 5, ви).t

1 о

° +S, sí(ü)„Ü:+ V, )) d t.

К=)

При интервале между частотами группового сигнала, кратном 2)Г/Т, результат накопления заряда на интегрирующем конденсаторе 34 определяется параметрами только того канального

121b834 у -у,1

+ у — у 4

UT — Uh„, = Х„x„l ° сигнала, частота которого совпадает с частотой опорного колебания.

При этом

Ос = (ЬО о+f Sо Sр сов 1 с).

Т

° -р, Второй член этой суммы пропорционален амплитуде и косинусу фазы вы.деляемого -ro канального сигнала, т.е. проекции канального сигнала на опорное колебание.. Обозначим сиифазную пооекцию канального сигнала .Хр, т.е., р S . с,>з Х -, тогТ

Я,с а а да

Полученное напряжение U< запишется в блоке 20 памяти, после чего ключ 33 сброса разрядит интегрирующий конденсатор 34.

Рассмотрим теперь обработку одного канального сигнала на двух (и-1)-й и и-й посылках сигнала.

На (и-1)-й посылке на интегрирующем конденсаторе 34 накопится напрят жение U„= Х„,+ — -hg Я .

КС

Отметим, что второй член этой суммы независим от номера посылки.

Напряжение (U„<) запишется в блок 20 памяти. На следующей и-й посьатке в интегрирующем конденсаторе 34 накопится напряжение

Т

U = Х + — — — Яс.

RQ йсi

Напряжение на выходе вычитателя

19 равно разности

После выпрямителя 27 получим абсолютную величину разности проекций Х и Х „соседних посы1 лок данного канального сигнала.

Аналогичные процессы происходят в. квадратурном подканале 5. Однако вследствие того, что групповой сигнал поступает на вход квадра,турного подканала 5 через фазовращатель на 90 6, дающий фазовый сдвиг на 90, на интегрирующем конденсатоо ре 34 разностного интегратора 18 этого квадратурного подканала 5 накопится напряжение (U ) g —.(с Sî+P S S " е)Т

Второй член этой суммы пропорци онален квадратурной проекции канального сигнала У<. Б результате на вы5 ходе. вычитателя 19 квадратурного подканала 5 получим величину

Выпрямитель 24 сформирует абсолютную величину разности квадратурных проекций

На выходе сумматора 13 получим сумму

Рассмотрим теперь процессы в дополнительных синфазном и квадра 0, турном подканалах 8 и 9. Опорное коле— бание на их опорные входы проходит через переключатель 11 мощности. Состояние переключателя 1! мощности определяется импульсами от формирователя

3 импульсов, причем на четных посылках переключатель 11 мощности находится, например, в правом положении, а на нечетных посылках — в левом положении. Это приводит к изменению знаков на противоположные у проекций канального сигнала на нечетных поГ сылках (из-за сдвига фазы опорного колебания на 180 j. В результате, если и-я посылка окажется нечетной, 35 получим для синфазного подканала 8, что (U U, „) „ =-Х„ - Х„, = -(Х„

+ Х,1!) 40

Если же и-я посылка окажется четной, а (п-1) ÿ нечетной, тогда получим

1 п 11т-1) и Хг + Хп 1 °

На выходе выпрямителей 24 дополнительных синфазного и квадратурного подканалов 8 и 9 всегда получаем сумму проекций, а на выходе сумматора 14 получим сумму

50 (X, + Х„, + I У.",„+ У .

Напряжение. на выходе компаратора

15 будет положительным> если

1к. х +1 У .- .-. - - ..}

Зтот случай соответствует нулевой разности фаз между и-й и (п-1)-й посылками. Если разность фаз между! 216834

20

55 посылками на передаче 180, тогда разность проекций окажется больше их суммы.

Таким образом, знаки напряжения на выходе компаратора 15 соответствует знакам символов переданной информации по 1 — ому канальному сигналу, При детектировании сигналов путем нелинейной обработки в диодных детекторах 16 и 17 на сигнальных выходах диодных детекторов 16 и 17 помимо полезного сигнала возникает еще постоянное напряжение, обусловленное детектированием опорного колебания, которое в данном случае значительно больше полезнога сигнала. Полезный сигнал на каждой посылке представляет собой также постоянное напряжение.

Вследствие того, что сигнал представляет собой постоянное напряжение, его невозможно выделить обычными методами.

Постоянная составляющая напряжения, обусловленная детектированием опорного колебания, на выходах диодных детекторов 16 и 17 имеет противоположные полярности вследствие различного включения диодов

27. Токи через транзисторы -Р- и p ->-p 35 и 28 разностного интегратора 18, вызванные этой составляющей, протекают в противоположных направлениях и взаимно компенсируются в их коллекторной цепи. IIoстоянные составляющие токов, обусловленных детектированием полезного сигнала, будут протекать в одинаковых направлениях и сложатся в коллекторной цепи транзисторов

h -p -и ир-п -p 35 и 28 разностного интегратора 18. Таким образом, в коллекторной цепи транзисторов

v-p - и p-n — р 35 и 28 происходит компенсация постоянных составляющих, обусловленных детектированием опорного колебания в детекторах 16 и 17 и сложение постоянных токов, обусловленных детектированием полезного сигнала.

Вследствие этого составляющая, обусловленная детектированием опорного колебания, проявляется только изза различия в параметрах диодов 27, транзисторов h -р - и p - -p 35 и 28 и сумматоров 21 и 22 мощности.

Однако даже такой остаток некомпенсированчой постоянной составляющей, обусловленной детектированием опорного колебания, может оказаться близким к величине. полезного сигнала. Попытка устранить разброс параметров указанных компонентов привела бы к значительному ухудшению технологичности аппаратуры.

В предлагаемом демодуляторе влияние нескомпенсированной постоянной составляющей устраняется тем, что на выход каждого синфазного и квадратурного подканала 4, 8 и 5, 9 поступает всегда разность проекций канальных сигналов, поступивших на их выходы.

Формула изобретения l . Демодулятор сигналов с фаэоразностной модуляцией, содержащий распределитель мощности, выход которого соединен с сигнальным входом основного синфазного подканала, с входом первого фазовращателя на

90 и с входом второго фазовращао теля на 90, выход первого фазовращателя на 90 подключен к сигнальному входу основного квадратурного показателя, опорный вход которого соединен с выходом генератора опорных сигналов и с опорным входом основного синфазного подканала, выход которого соединен с первым входом первого сумматора, второй вход которого подключен к выходу основного квадратурного подканала, управляющий вход. которого соединен с управляющим входом основного синфазного лодканала и с выходом блока синхронизации, выход первого сумматора соединен с первым входом компаратора, второй вход которого подключен к выходу второго сумматора, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены дополнительные синфазный и квадратурный подканалы, формирователь импульсов, переключатель мощности и о фазовращатель на !80, вход которого подключен к выходу генератора опорных сигналов и к первому входу переключателя мощности, выход которого соединен с опорным входом дополнительного синфазного подканала и с опорным входом дополнительного квадратурного. подканала, 1216834

35 сигнальный вход которого соединен с выходом второго фазовращателя на

90, вход которого подключен к. сигнальному входу дополнительного синфаэного подканала, управляющий вход которого соединен с управляющим входом дополнительного квадратурного подканала с выходом блока синхронизации и с входом фор- 1О мирователя импульсов, первый выход которого соединен с управляющим, входом переключателя мощности, второй вход которого. подключен к вью ходу фазовращателя на 180, при 15 этом второй и третий выходы формирователя импульсов подключены соответственно к первому и второму дополнительным управляющим входам основных синфаэного и квадратурнога подканалов и к первому и второму дополнительным управляющим входам дополнительных синфазного и квадратурного подканалов,, выходы которых подключены соответственно к перво- 25 му и второму входам второго сумматора, а вход распределителя мощности соединен с входом блока синхронизации.

2. Демодулятор по и.1, о т л ич а ю шийся тем, что каждый основной и дополнительный синфазные и квадратурные подканалы содержат выпрямитель, вычитатель, блок памяти, разностный интегратор, два детек— тора, два сумматора мощности и фазовращатель, выход. которого соединен с первым входом первого сумматора мощности, второй вход которого соединен с первым входом второго сумма- О тора мощности, второй вход которого подключен к входу фазовращателя, выходы первого и второго сумматоров мощности подключены к входам соответственно первого и второго

45 детекторов, выходы которых соединены с соответствующими сигнальными входами разностного интеграто- ра, выход которого соединен с первым входом вычитателя и с первым входом блока памяти, выход которого соеди50 нен с входом выпрямителя, выход которого является выходом каждого основного и дополнительного синфазных и квадратурных подканалов; сигнальным, опорным, управляющим, первым дополнительным и вторым дополнительным входами которого являются соответственно второй вход первого сумматора мощности, вход фазовращателя, второй вход блока памяти, первый и второй управляюшие входы разностного интегратора.

3. Демодулятор по п.l, о т -л ич а ю шийся .тем, что, формирователь импульсов содержит два ждущих мультивибратора, инвертор и делитель частоты, вход которого подключен к входу первого ждущего мультивибратора и к входу инвертора, выход которого подключен к входу второго ждущего мультивибратора, при этом выход делителя частоты выход первого ждущего мультивибратора и выход второго ждущего мультивибратора являются соответственно первым, вторым и третьим выходами формирователя импульсов, входом которого является вход делителя частоты.

4. Демодулятор по п.2, о т л ич а ю шийся тем, что каждый из детекторов содержит первый и второй конденсаторы и диод, анод (катод) которого соединен с первым выводом первого конденсатора, первый вывод второго конденсатора соединен с катодом (анодом) диода, второй вывод второго конденсатора соединен с земляной шиной, при этом второй вывод первого конденсатора является входом детектора,, выходами которого являются анод и катод диода.

5. Демодулятор по п.2, о т л и- ч а ю шийся тем, что раэностный интегратор содержит два резистора, транзистор транзистор Р— h -р, переключатель тока заряда, интегрирующий конденсатор., ключ сброса и поЬторитель напряжения, вход которого подключен к первому выводу интегрирующего конденсатора„ к первому выходу ключа сброса и к первому выходу переключателя тока заряда, сигнальный вход которого соединен с коллекторами транзистора N -p - h и транзистора Р— e -9, эмиттеры которых подключены к первым выводам соответственно первого и второго резисторов, второй выход переключателя тока заряда, второй вывод интегрирующего конденсатора и второй выход ключа сброса подключены .к земляной шине,.при этом вторые выводы первого и-второго резисторов, 12

1216834

С остави тель 0 . Геллер

ТехРеД Т.Дубинчак КоРРектоР К. СиРохман й»

Редактор Н.Пушненкова

Заказ 1005/б1 Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 415

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 база транзистора Н вЂ” Р— и база транзистора P - n — Р являются сигнальными входами разностного интегратора, управляющими входами которо-, го являются управляющие входы переключателя тока заряда и ключа сброса, выход повторителя напряжения является выходом разностного интегратора.