Устройство для определения свертки двух функций

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при обработке случайных процессов путем скользящего весового сглаживания в реальном масштабе времени. Цель изобретениярасширение функциональных возможностей за счет осуществления свертки входных сигналов с произвольной двухуровневой весовой функцией. В устройстве достигается возможность инвертировать коды с выхода формирователя унитарных сигналов в соответствии со значениями управляющих сигналов, поступающх с выходов регистра , в котором постоянно хранится код двухуровневой весовой функции , применение которой и является в устройстве новым. 1 ил. (Л 00 00 со

СОЮЭ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (I! ) (51)4 G 6 Р 15 36

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР пО ДЕЛАМ ИЗОБРЕТЕНИЙ V ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 37942!2/24-24 (22) 25.09.84 (46) 15.03.86. У 10 (71) Ивано-Франковский институт нефти и газа (72) Я.Н.Николайчук, Р.В.Доценко и ".È.Èùåðÿêîâ (53) 681.32(088.8) (56) Авторское свидетельство СССР !! - 943743, кл. G 06 F 15/36, 1978. (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ

СВЕРТКИ ДВУХ ФУНКЦИЙ (57) Изобретение относится к области вычислительной техники и может быть использовано при обработке случайных процессов путем скользящего весового сглаживания в реальном масштабе времени. Цель изобретениярасширение функциональных возможностей за счет осуществления свертки входных сигналов с произвольной двухуровневой весовой функцией. В устройстве достигается воэможность инвертировать коды с выхода формирователя унитарных сигналов в соответствии со значениями управляющих сигналов, поступающих с выходов регистра, в котором постоянно хранится код двухуровневой весовой функции, применение которой и является в устройстве новым. 1 ил.

1 12

Изобретение относится к вычислительной технике и может быть использовано при обработке. случайных процессов путем скользящего весового сглаживания в реальном масштабе времени.

Цель изобретения — расширение функциональных возможностей устройства за счет осуществления свертки входных сигналов.с произвольной двухуровневой функцией.

При прохождении унитарных сигналов через вычислительную среду осуществляется их свертка и скользящее осреднение путем вычисления модульной функции согласно выражению 2

C; ...- х;-5;I, i 2-.1 где Х; — значения входного унитарного кода, S — двоичные значения весовой функции.

В частном случае, если все значения Б; =1, устройство выполняет вычисление скользящего среднего случайного процесса.

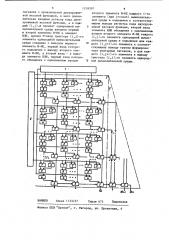

На чертеже изображена структурная схема устройства.

Устройство содержит формирователь 1 унитарных сигнаЛов, однородную вычислительную среду 2, многоканальный преобразователь 3 унитарных сигналов в двоичный код, RS-триггеры 4, сумматоры 5, регистр

6, второй элемент И-НЕ 7, первый элемент И-НЕ 8, элементы ИЛИ 9, а также выходы 101-10„ устройства.

Устройство работает следующим образом, Перед началом работы устройства в регистр 6 заносится и постоянно хранится код двухуровневой весовой функции S;. Обработка результатов измерения путем их цифровой свертки с двухуровневой. весовой функцией и скользящего осреднения происходит за один такт работы устройства. В начале каждого такта работы на первом выходе блока 1 формируется короткий импульс, по фронту нарастания которого происходит сдвиг информации, хранимой в вычислительной среде 2. При этом в сумматоры 5 вычислительной среды j -ro ряда в соответствии со значением S; двухуров- ° невой весовой функции заносятся прямые или инвертированные значения

18397

f0

55 состояний триггеров 4 элементов вычислительной среды (i-1)-го ряда.

Таким образом, после выполнения операций сдвига в вычислительной среде 2 на выходах 10„-10t устройства, являющихся выходами многоканального преобразователя 3 унитарных сигналов в двоичный код и выходами элементов последнего (i=2, j=K)-го л ряда вычислительной среды 2, формируется код скользящих средних значений модульной функции. Работа введенных элементов 7-9 описывается логическим уравнением

Формула изобретения

Устройство для определения свертки двух функций, содержащее формирователь унитарных сигналов, однородную вычислительную среду, многоканальный преобразователь унитарных сигналов в двоичный код, причем каждый (i j)-й элемент (i=2,3,...,2

j†=,3,...,К) однородной вычислительной среды содержит сумматор и RSтриггер, выходы сумматоров i-x (i=2 ) элементов однородной вычислительной среды соединены с соответствующими входами многоканального преобразователя унитарных сигналов в двоичный код, управляющие входы триггеров объединены и подключены к.выходу формирователя унитарных сигналов, первый вход сумматора (i,j)-ro элемента среды подключен к выходу суммы сумматора (i-i,j)-го элемента однородной вычислительной среды, второй вход сумматора подключен к прямому выходу триггера (i,j)-ro элемента однородной вычислительной среды, третий вход сумматора (i,j)-ro элемента однородной вычислительной среды подключен к. выходу переноса сумматора (3.,,)-l)-го элемента однороднойвычислительной среды, а выходы i-x (при )=K) элементов вычислительной среды, начиная с К-го разряда, и выходы многоканального преобразователя унитарных сигналов в двоичный код являются выходами устройства, о т л и ч а ю щ е— е с я тем, что, с целью расширения функциональных возможностей за счет осуществления свертки входных

1218397

ЯЬ-г 1 ю

ВНИИПИ Заказ 1133/57 Тираж 673 Подписное

Филиал ППБ "Патент", r . Ужгород, ул . Проектная, 4 сигналов с произвольной двухуровневой весовой функцией, в него дополнительно введены регистр кода двухуровневой весовой функции, а в каждый (i )-й элемент однородной вычислительной среды введены первый и второй элементы И-НЕ и элемент

ИЛИ, причем 3-вход триггера (i,j)-го элемента однородйой вычислительной среды соединен с выходом первого элемента И-НЕ, первый вход которого подключен к выходу второго элемента И-НЕ, а второй вход — к выходу элемента ИЛИ, первый вход которого объединен с одноименным входом второго элемента И-НЕ каждого i-го элемента (при )=const) вычислительной среды и подключен к соответствующему выходу регистра кода двухуров5 невой весовой функции, второй вход элемента ИЛИ объединен с одноименными входом второго элемента И-НЕ каждого (i,j )-го элемента однородной вычислительной среды и подключен для какдого (i,j=l)-ro элемента к соответствующему выходу группы формирователя унитарных сигналов, а для каждого (i +1)-ro элемента к выходу триггера (i J )-ro элемента однород15 ной вычислительной среды..