Цифровой синтезатор частот

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике . Уменьшается паразитная фазовая модуляция выходного сигнала. Код требуемой выходной частоты М с блока 2 установки кода частоты поступает на накапливающий сумматор (НС) 3 и на второй управляемый генератор тока (УГГ) 6. По импульсам с генератора 1 опорной частоты происходит сложение накопленного в НС 3 числа с числом М. По импульсу переполнения с НС 3 код числа PJ, оставшегося в НС 3, переписывается в регистр памяти 4. С регистра памяти 4 число Р/, определяющее величину паразитной фазовой модуляции импульсов, поступает на первьй УГТ 5. После прекращения импульса переполнения D-триггер 7 формирует импульс , по которому открывается второй ключ 9. Через открытый ключ 9 током первого УГТ 5, определяемьм числом Pj , заряжается конденсатор 10. С выхода компаратора 11, подключенного к конденсатору 10, импульс поступает на выход и на элемент И 12. После запирания ключа 9 импульс с D-триггера 7 поступает на элемент И 12. Логическая 1 с его выхода сткрьшает ключ 8 и конденсатор 10 разряжается током второго УГТ 6, величина которого определяет- . ся числом М. При достижении напряжения на конденсаторе 10 величины опорного напряжения импульс компаратора 11 закончится и через элемент И 12 закроет ключ 8. 1 ил. - -

00е3 СОВЕТСНИХ

СОЦ ИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ABTOPCHOMY СВИДЕТЕЛЬСТВУ л

° а

° °

ГЩгУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3824060/24-09 (22) 17.12.84 . (46) 15.03.86. Бюл. М 10 (72) И.Н. Гуревич и Ю.А. Никитин (53) 621.373.42(088.8) (56) Патент США В 3882403, кл. 328-14, 6.05.75.

Авторское свидетельство СССР

Н 978314, кл. К 03 В 19/00, 12.01.81. (54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ (57) Изобретение относится к радиотехнике. Уменьшается паразитная фазовая модуляция выходного сигнала.

Код требуемой выходной частоты М с блока 2 установки. кода частоты посту пает на накапливающий сумматор (НС) 3 и на второй управляемый генератор тока (УГТ) 6. По импульсам с генератора 1 опорной частоты происходит сложение накопленного в НС 3 числа с числом М. По импульсу переполнения с, НС 3 код числа P1,. оставшегося в

„SU„„121 4 8 A сЯ) 4 Н 03 В 19/00

НС 3, переписывается в регистр памяти 4. С регистра памяти 4 число Р(, определяющее величину паразитной фазовой модуляции импульсов, поступает на первый УГТ 5. После прекращения импульса переполнения 9-триггер 7 формирует импульс, по которому открывается второй ключ 9. Через открытый ключ 9 током первого УГТ 5, определяемым числом P1, заряжается конденсатор 10. С выхода компаратора 11, подключенного к конденсатору 10, импульс поступает на выход и на элемент И 12. После запирания ключа 9 импульс с D-триггера 7 поступает на элемент И 12. Логическая "1" с его выхода сткрывает ключ 8 и конденсатор 10 разряжается током второго

УГТ 6, величина которого определяет-, ся числом N. При достижении напряжения на конденсаторе 10 величины опорного напряжения импульс компаратора 11 закончится и через элемент

И 12 закроет ключ 8. 1 ил.

1 в((;= 2к ——

Р т

Твык где Тв,„ — период следования выходных импульсов.

1 рр д р

И Х,, ае, С

1 1218

Изобретечие относится к радиотех-:„ нике и может быть использовано в ра- диоприемных и радиопередающих устройствах для формирования сетки частот. 5

Цель изобретения — уменьшение паразитной фазовой модуляции выходного сигнала.

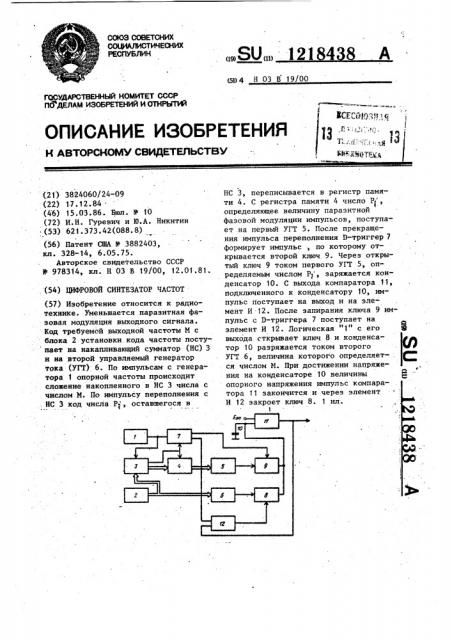

На чертеже представлена структурная электрическая схема цифрового 10 синтезатора частот.

Цифровой синтезатор частот содержит генератор 1 опорной частоты (ГОЧ), блок 2 установки кода частоты, накапливающий сумматор 3, регистр 4 15 памяти, первый 5 и второй 6 управляемые генераторы тока (УГТ), D-триггер 7, первый ключ 8, второй ключ 9, конденсатор 10, компаратор 11 и элемент И 12. 20

Цифровой синтезатор частот работает следующим образом.

Код требуемой выходной частоты М с выхода блока 2 установки кода частоты поступает на накапливающий 25 сумматор 3, имеющий емкость И, и на входы второго УГТ 6.

С частотой следования импульсов на выходе ГОЧ 1 в накапливающем сумЗ0 маторе 3 осуществляется сложение накопленного числа с числом М. Через К периодов ГОЧ 1 происходит переполнение накапливающего сумматора 3, на его выходе переполнения появляется импульс, который поступает на управляющий вход регистра 4 памяти и на D-вход 0-триггера 7, В регистр памяти 4 переписывается код числа Р, оставшегося в накапливающем сумматоре 3 после его пе.реполнения. После прихода следующего импульса с выхода ГОЧ 1 исчезает сигнал переполнения на выходе накапливающего сумматор 3, а на выходе

D-триггера 7 возникает импульс, дли- 45 тельность которого равна периоду т следования импульсов на.выходе ГОЧ 1.

Этот импульс открывает второй ключ 9 и в течение времени Тв осуществляется заряд конденсатора 10 током 50 первого УГТ 5, определяемого кодом на выходе регистра 4 памяти, т.е. числом P.. Ца выходе компаратора

11 начинается импульс, поступающий на второй вход элемента И 12. В 55 момент появления второго импульса с выхода ГОЧ 1 заканчивается импульс на выходе D-триггера 7 и запирается

438 2 второй ключ 9. Заряд конденсатора

10 прекращается. Одновременно на первом входе элемента И 12 возникает логическая "1.", передающаяся на выход, элемента И 12 и открывающая первый ключ 8. Начинается разряд конденсатора 10 током второго УГТ 6, величина которого определяется числом М.

Как только напряжение на конденсаторе 10 достигает величины опорного напряжения Е» заканчивается импульс на выходе компаратора 11 и через элемент И 12 закрывается первый ключ 8. Разряд конденсатора 10 прекращается.

При следующем переполнении накапливающего сумматора 3 весь цикл повторяется. Различие заключается в другом токе заряда первого УГТ 5, определяемом новым числом Р .

Число Р; определяет: величину паразиткой фазовой модуляции импульсов Щ на выходе D-триггера 7 .! которая приводит к временному сдвигу (в сторону опережения относительно гипотетической равномерной последовательности той же частоты} каждого выходного импульса на величину

1 P д = — ь1т = — т

2в 4 вык M в

Задержка tt t окончания импульса на выходе компаратора 11 определяется из условия равенства напряжений при заряде и разряде конденсатора 10 где С вЂ” емкость конденсатора 10;

Хо„ Хо — токи генераторов первого 5 и второго 6 УГТ соответственно, при минимальных управляющих кодах (логическая единица только в младшем разряде).

Отсюда, Составитель Ю. Ковалев

Редактор Л. Кастран Техред А„Бабинец Корректор Т ° Колб

Заказ 113?/59 Тираж 818 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4т.е. при I =I осуществляется полная компенсация паразитной фазовой импульсной модуляции заднего фронта импульсов во всем диапазоне выходных частот (при любом коде М) и независимо от изменения входной емкости компаратора 11.

При сопряжении синтезатора с последующими цифровыми устройствами используется непосредственно выход компаратора 11, при необходимос ти перехода к аналоговому сигналу необходимо введение либо расширителя импульсов (например, мультивибратора с одним устойчивым состоянием) либо триггера с последующим фильтром нижних частот. Во всех случаях последующая цифровая схема должна срабатывать от заднего фронта выходного импульса компаратора. Первый 5 и второй 6 УГТ могут быть выполнены на базе цифроаналоговых преобразователей.

Таким образом, в предлагаемом синтезаторе уменьшен уровень паразитной фазовой модуляции за счет работы на одной постоянной точке входной характеристики компаратора (определяемой

Е ) и исключения влияния нелинейности и нестабильности входной емкости компаратора и- за счет исключения генератора линейно изменяющегося напряжения. е

218.438

ФормулаизобретенияЦифровой синтезатор частот, содержащий последовательно соединенные блок установки кода частоты, накапливающий сумматор, регистр памяти и первый управляемый генератор тока,,компаратор, второй управляемый генератор тока, управляющий вход которого соединен с выходом блока установ-:

10 ки кода частоты, последовательно сое диненные генератор опорной частоты и

D — триггер, при этом выход генератора опорной частоты соединен с тактовым входом накапливающего сумматора, 15 выход переноса которого соединен с

D-входом D-триггера и с управляющим входом регистра памяти, о т л и— чающий с я тем, что, с целью уменьшения паразитной фазовой моду20 ляции выходного сигнала, между первым выходом D-триггера и сигнальным входом компаратора введены последовательно соединенные элемент И и первый ключ, а также введен второй

25 ключ и конденсатор, который включен между сигнальным входом компаратора и общей шиной цифрового синтезатора частот, при этом сигнальные входы первого и второго ключей подключены соответственно к выходу второго управляемого генератора тока и к выходу первого управляемого генератора тока, управляющий вход второго ключа соединен с вторым выходом D-триггера, а выход второго ключа подключен к сигнальному входу компаратора, второй вход которого является входом опорного напряжения цифрового синтезатора частот, а выход комнаратора соединен с вторым входом элемента И.