Усилитель с компенсацией входного тока

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может использоваться во входных каскадах операционных усилителей . Обеспечивается уменьшение входного тока. Структура первого, второго транзисторов (Т 1 и 2 и дополнительных транзисторов (ДТ) 6 и 7 противоположна структуре третьего и четвертого Т 3 и 4. Коллектор Т 1 соединен с эмиттером Т 2 и базой ДТ 6. Эмиттеры Т 1 и ДТ 6 и 7 подключены через источник тока 5 к первой щине источника питания. К второй шине источника питания подключены коллектор Т 2, эмиттеры Т 3, 4 и через то ко зад акаций элемент 8 - коллектор ДТ 6 и база ДТ 7. Базы Т 3 и 4 объединены и подключены к коллектору ДТ 7 . К базам Т 1 и 2 подключе(ны коллекторы соответственно Т 4 и 3. Входной сигнал подается на базу Т 1. С его эмиттера снимается выходной сигнал. Степень компенсации входного тока определяется равенством базового тока Т 1 и коллекторного тока Т 4. Для этого должны быть идентйчньЬ1И режимы работы Т 1 и 2, что обеспечивается выбором величины тока токозадающего элемента 8, а также режимы работы Т 3 и 4, ; что обеспечивается ДТ 7. /з.п. ф-лы, 2 ил. (П

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

343 (51) 4 Н 03

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

М ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3843471/24-09 (22) 1 1 .-01. 85 (46) 15.03.86. Бюл. У 10 (72) С.Г. Иванов и В.Ф. Федючок (53) 621.375.024(088.8) (56) Аналоговые интегральные схемы/

Под ред. Дж. Коннели. M.: Мир, 1977, с. 112, фиг. 3.30.

Патент США N 3916331, кл. Н 03 F 3/68, 330-30, 1975 ° (54) УСИЛИТЕЛЬ С КОМПЕНСАЦИЕЙ ВХОДНОГО ТОКА (57) Изобретение относится к радиотехнике и может использоваться во входных каскадах операционных усилителей. Обеспечивается уменьшение входного тока. Структура первого, второго транзисторов (Т) 1 и 2 и дополнительных транзисторов (ДТ) 6 и 7 противоположна структуре третьего и четвертого Т 3 и 4. Коллектор Т 1 соединен с эмиттером Т 2 и базой

„„SU„, 1218445 A

ДТ 6. Эмиттеры Т 1 и ДТ 6 и 7 подключены через источник тока 5 к первой шине источника питания. К второй шине источника питания подключены коллектор Т 2, эмиттеры Т 3, 4 и через токозадающий элемент 8 — коллектор ДТ 6 и база ДТ 7. Базы Т 3 и 4 объединены и подключены к коллектору ДТ 7. К базам Т 1 и 2 подключены коллекторы соответственно Т 4 и 3.

Входной сигнал подается на базу Т 1.

С его эмиттера снимается выходной сигнал. Степень компенсации входного тока определяется равенством базового тока Т 1 и коллекторного тока

Т 4. Для этого должны быть идентич- Э ньяи режимы работы Т 1 и 2, что обес- g печивается выбором величины тока токозадающего элемента 8, а также С режимы работы Т 3 и 4, что обеспечивается ДТ 7. f з.п. 5 ф-лы, 2 ил.

1 12

Изобретение относится к радиотех= нике и может использоваться в радис- электронной аппаратуре различного назначения, в частности во входных каскадах операционных усилителей.

Цель изобретения — уменьшение входного тока.

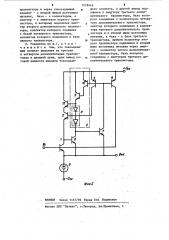

На фиг. 1 представлена принципиальная электрическая схема усилителя с компенсацией входного тока; на фиг. 2 — принципиальная электрическая схема одной из реализаций усилителя с компенсацией входного тока.

Усилитель с компенсацией входно го тока (фиг. 1) содержит первый, . второй, третий и четвертый транзисторы 1-4, источник тока 5,. первый и второй дополнительные транзисторы б и 7, токозадающий элемент 8, выполненный (фиг. 2) на третьем и четвертом дополнительных транзисторах

9 и 10, диодной цепи 11, а также пятый дополнительный транзистор 12. !

Усилитель с компенсацией входного тока работает следующим образом.

Степень компенсации входного тока определяется точностью равенства базового тока первого транзистора 1 и коллекторного тока четвертого транзистора 4, а это, в свою очередь, определяется идентичностью режимов работы первого и второго транзисторов

1 и 2; а также третьего и четвертого транзисторов 3 и 4. Последняя пара транзисторов находится практически в идентичных условиях (бтличие эмиттерно-коллекторных напряжений этих транзисторов. на падение напряжения базаэмиттер второго транзистора 2 может быть ликвидировано включением в коллекторную цепь четвертого транзистора 4 одного прямосмещенного диода); следовательно, если обеспечить идентичность режимов первого и второго транзисторов 1 и 2, можно достигнуть полной компенсации входного тока усилителя с компенсацией входного тока. Равенство коллекторно-эмиттерных напряжений этих транзисторов может быть достигнуто выбором величины положительного (для данного рисун,ка) напряжений источника питания и обеспечением (внешними цепями) изменения этого напряжения синхронно входному сигналу, либо использованием в качестве вспомогательного транзистора каскадной схемы (второй и пятый дополнительный транзисторы 2, 12

18445 2

55 и диодная цепь 11). Равенство эмиттерных токов первого и второго транзисторов 1 и 2 обеспечивается выбором величины тока токозадающего элемента 8, равным эмиттерному току первого транзистора 1, так чтобы базовый ток первого дополнительного транзистора б был равен базовому току первого транзистора 1. Это может быть обеспечено использованием в качестве токозадающего элемента 8 схемы на третьем и четвертом дополнительных транзисторов 9 и 10. Базовые токи третьего и четвертого транзисторов

3 и 4 обеспечиваются вторым дополнительным транзистором 7, чей режимный ток подстраивается под эти базовые токи с помощью внутренней отрицательной обратной связи по току. Таким образом, в данной схеме выбором; величины тока токозадающего элемента 8 может быть обеспечена полная идентичность режимов работы первого и второго транзисторов 1 и 2, что обеспечивает равенство их базовых токов и, следовательно, полную компенсацию входного тока схемы.

Формула изобретения

1. Усилитель с компенсацией входного тока, содержащий первый транзис тор, база которого является входом, а эмиттер — выходом усилителя с компенсацией входного тока и через источник тока соединен с первой шиной источника питания, коллекторс эмиттером второго транзистора, коллектор которого соединен с второй ., шиной источника питания, база — с коллектором третьего транзистора, база и эмиттер которого подключены соответственно к базе и эмиттеру четвертого транзистора, эмиттеры третьего и четвертого транзисторов подключены к второй шине источника питания, при этом структура первого и второго транзисторов противоположна структуре третьего и четвертого транзисторов, о т л и ч а ю щ и й— с я тем, что, с целью уменьшения входного тока в усилитель, введены токозадающий элемент, а также первый и второй дополнительные транзисторы, структура которых соответствует структуре первого транзис-, тора, при этом коллектор первого дополнительного транзистора соединен с базой второго дополнительного

3 1218445 4 транзистора и через токозадающий, .щего элемента, а другой вывод подэлемент — с второй шиной источника ключен к эмиттеру третьего дополпитания; база — с коллектором, а кительного транзистора, база котоэмиттер — c эмиттером первого тран- рого соединена с коллектором четверзистора, к которому подключен эмит- 5 того дополнительного транзистора, тер второго дополнительного транзис- эмиттер которого подключен к коллектора, коллектор которого соединен тору третьего дополнительного транс.базой четвертого транзистора, „ зистора и к второй шине источника коллектор которого подключен к базе питания, а база — к базе третьего первого транзистора. 1р транзистора, причем коллектор вто2. Усилитель по п.1, о т л и— рого транзистора подключен к второй ч а ю шийся тем, что токозадаю- шине источника питания через эмитщий элемент выполнен на третьем .,тер — коллектор пятого дополнитель- .

Г и четвертом дополнительных транзис- ного транзистора, база которого торах и диодной цели, один вывод ко- 15 соединена с эмиттером третьего доторой является выходом токозадаю- полнительного транзистора. фиа2

ВНИИПИ Заказ 1137/59 Тираж 818, Подписное

Филиал ППП "Патент", г.Ужгород, ул.Проектная, 4