Импульсный частотно-фазовый детектор

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и является дополнительным к авт. св. № 1124424. Цель изобрете-:.; ния - увеличение быстродействия. Сигнал частоты о постзшает на С-вход D-триггера (ДТ) 1, ;на R-вход ДТ 2 и на блок задержки (fis) 5, Сигнал частоты F поступает на С-вход ДТ 2, R-вход ДТ 1 и на БЗ 6. БЗ 5 и 6 обес- 1печивают время задержки , равное длительности входного импульса. Когда FO F , фронтом импульса частоты FO ДТ 1 устанавливается в единичное состояние. ДТ 3 устанавливается в

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) 21710 A (5!) 4 Н 03 Э 13 00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ с--,, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВР ДЕТЕЛЬСТБУ (61) !124424 (21) 3759894/24-09 (22) 21.06.84 (46) 30.03.86. Бюл. 1(12 (72) И.В.Колосов и А.В.Колосов (53) 62!.376.6 (088.8) (56) Авторское свидетельство СССР

11 1124424, кл. Н 03 D 13/00, 1983. (54) ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР (57) Изобретение относится к радио. технике и является дополнительным к авт. св. У 1124424. Цель изобрете-::. ния — увеличение быстродействИя, Сигнал частоты постуцает на С-вход

D-триггера (ДТ) 1,;на R-вход ДТ 2. и на блок задержки (БЗ) 5. Сигнал частоты F„ поступает на С-вход ДТ 2, R-вход ДТ 1 и на БЗ 6. БЗ 5 и 6 обес/ печивают время задержки, равное длительности входного импульса. Когда Р, ) F,, Фронтом импульса частоты

F ДТ 1 устанавливается в единичное состояние. ДТ 3 устанавливается в

1221710 тает с большей скоростью. В момент, когда опережают по фазе импульсы

1 частоты F, первый же импульс частоты F» поступая с ДТ 2 íà R-вход, ничный уровень с его выхода через единичное состояние инвертированчым импульсом частоты F с БЗ 5, поступающим на его С-вход, и самоблокируется. С выхода ДТ 1 импульсы длительностью, пропорциональной разности фаэ импульсов частот Г и F через элемент ИЛИ 7 поступают на интегратор 9, на D-вход ДТ 3 и на

К-вход ДТ 4. Выходное напряжение интегратора 9 нарастает со скоростью, определяемой его постоянной времени, Когда ДТ 3 находится в единичном состоянии, напряжение с его инверсного выхода через элемент И-НЕ 10 поступает на управляющий вход интегратора 9, В результате полоса пропускания интегратора 9 увеличивается и его выходное напряжение нарас1

Изобретение относится к радиотехнике, может использоваться в быстродействующих схемах фаэовой автоподстройки частоты с малым уровнем частот, кратных частоте сравнения в выходнрм сигнале, и является усовершенствованием изобретения по авт. св. СССР У 1124424.

Цель изобретения — увеличение быстродействия.

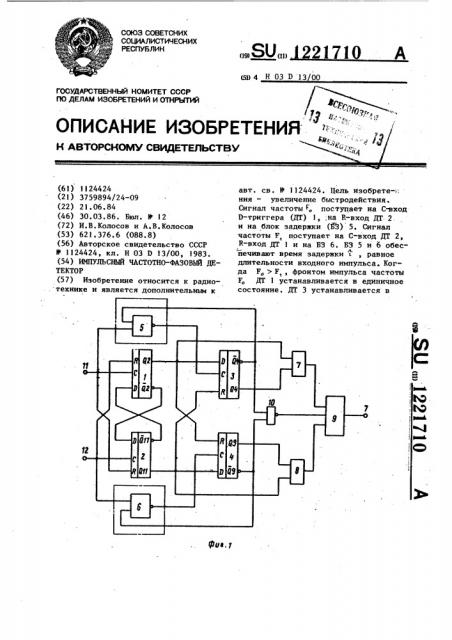

На фиг. 1 приведена структурная электрическая схема предложенного

I импульсного частотно-фазового детектора; на фиг. 2 — диаграммы, поясняющие его работу..

Импульсный частотно-фазовый детектор Содержит первый, второй, третий и четвертый D-триггеры 1 — 4, первый и второй блоки 5 и 6 задержки, первый -и второй элементы ИЛИ 7 и 8, интегратор 9, элемент И-НЕ 10.

Импульсный частотно-фазовый детектор работает следующим образом.

С источника 11 входного сигнала поступает, например, частота Р; (фиг. 2а), а с источника 12 — частота Р (фиг. 28).

В исходном состоянии на выходах

D"òðèããåðîâ 1 — 4 и выходах элеменУтов ИЛИ 7 и 8 присутствует напряжеtete логического "0". Пусть частота

F > Г„. Когда разность фаз между л

F, и F, станет больше P.-- = 2%, 5

ЗО

ДТ 3, устанавливает: его в нулевое состояние. Импульсы, длительность которых определяется разностью фаз импульсов частот F» и Fo, с ДТ 2 через элемент ИЛИ 8 поступают на интегратор 9, разряжая его, и íà D-вход

ДТ 4. При поступлении на С-вход

ДТ 4 импульса частоты F с БЗ 6, едиэлемент И-HE 10 поступает на управляющий вход интегратора 9, уменьшая его постоянную времени. В результате скорость изменения напряжения становится больше. I з.п. ф-лы, 2 ил.

2 где — аремя задержки в блоке 5 задержки, например, при произвольном использовании в качестве блока задержки элемента И-НЕ 10 л о где, — длительность входного импульса; Т, — период следования импульсов опорной частоты, to фронтом импульса частоты F D-триггер 1 переключается в единичное состояние (фиг. 2 ь) в момент времени t« a в момент t фронтом инвертированного импульса частоты Г, блока 5 в единичное состояние переключается

D-триггер.3 (фиг. 2a),который самоблокируется в этом состоянии, поскольку напряжение логического "0" с инверсного выхода D-триггера 3 запрещает прохождение импульсов частоты F., на синхровход D-триггера

3. Таким образом, в интервале времени t, — t, и — t на выходе D-триггера 1 (фиг. 2е) имеются импульсы с длительностью, пропорциональной разности фаз входных частот

Р, и Г „ в результате на выходе интегратора 9 в интервале происходит нарастание выходного напряжения со скоростью, определяемой постоянной времени интегратора 9 в этом интервале времени (фиг. 2о).

В интервале,й„ вЂ” t на выходе элемента ИЛИ 7 логический "0" — ин.тегратор 9 находится в режиме хранения. выходе элемента И-НЕ 10 также появляется напряжение логической "1", под воздействием которой постоянная времени интегратора 9 уменьшается, а скорость изменения напряжения становится больше, чем на интервалах 6 7 и 8 9 °

Таким образом, за счет самоблокировки D-триггеров 3 или 4, в зависимости от знака частотной расстройки, в импульсном частотно-фазовом детекторе отсутствуют паузы при pasности фаз 6 Y с(- 2li) в частотном режиме и за счет коммутации постоян-. ной времени интегратора 9 получают более высокую скорость нарастания выходного напряжения, что позволяет сократить время достижения режима синхронизации, т.е. увеличить быстродействие.

Формула изобретения

1 . Импульсный частотно-фазовый детектор по авт. св. У 1124424, о тл и ч а ю шийся тем, что, с целью увеличения быстродействия, введен элемент И-НЕ, первый вход которого соединен с инверсным выходом третьего Р-триггера, а второй вход соединен с инверсным выходом четвертого D òðèããåðà, выход элемента

И-НЕ подключен к управляющему входу интегратора, инверсный выход третьего D-триггера подключен к второму входу первого блока задержки, а инверсный выход четвертого D-триггера подключен к второму входу второго блока задержки, прямой выход перво го D-триггера соединен. с R-входом четвертого D-триггера, а прямой выход второго D-триггера соединен с R-входом третьего D-триггера.

2. Детектор по п. 1, о т л ич а ю шийся тем, что каждый блок задержки выполнен на элементе

И-HE.

3 1221710

8 момент t 0-триггер 1 переключается в единичное состояние (фиг,2g) на выходе элемента ИЛИ 7 также появляется уровень логической "1", при этом напряжение на выходе интегратора 9 начинает нарастать с той же ско, ростью, что и в интервале t - t „ .

В момент t разность фаз между импульсами частот F, и Г„ становится больше ь и фронтом инвертированного 1и импульса частоты F, блока 5 D-триггер 3 переключается в единичное сос: тояние (фнг. 2а). Одновременно на выходе элемента И-НЕ 10 также появляется уровень логической "1", под воздействием которого полоса пропускания интегратора 9 увеличивается и напряжение на выходе интегратора 9 нарастает с большей скоростью. В момент времени „ начинают опережать по фазе импульсы частоты F, . Таким образом, первый же опережающий импульс частоты Р„ сбрасывает по

R-входу D-триггер 3 в нулевое состояние в момент и (фиг.2i).

Таким образом D-триггер 2 переключается в единичное состояние (фиг. 2е), а интегратор 9 начинает разряжаться с той же скоростью, что и в интервалы t — t u t

30 поскольку в момент tц на выходе элемента И-НЕ 1О логический "0" и полоса пропускания интегратора 9 меньше.

В момент t фронтом импульса частоты F D-триггер 2 сбрасывается в нулевое состояние. В интервале

5 — режим хранения напряжения на интеграторе 9. В момент времени t

D-триггер 2 снова переключается в единичное состояние, а в момент t единичное состояние с входа 9-триг- 4О гера 4 переписывается на его выход фронтом инвентированного импульса частоты F, (фиг. 2 ), поскольку разность фаз между импульсами частот F л.

М и F стала больше i . При этом на 45

Составитель И. Гра билни

Редактор Л.Повхан Техред О.Сопко Корректор А.Зимокосов

Заказ 1618/57 - Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Óæãoðîä, ул.Проектная,4