Устройство задержки

Иллюстрации

Показать всеРеферат

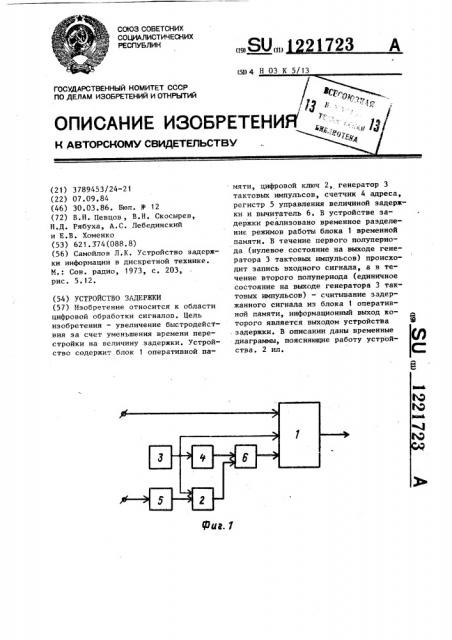

Изобретение относится к области цифровой обработки сигналов. Цель изобретения - увеличение быстродействия за счет уменьшения времени перестройки на величину задержки. Устройство содержит блок 1 оперативной памяти , цифровой ключ 2, генератор 3 тактовых импульсов, счетчик 4 адреса, регистр 5 управления величиной задержки и вычитатель 6. В устройстве задержки реализовано временное разделение режимов работы блока 1 временной памяти. В течение первого полупериода (нулевое состояние на вЕаходе генератора 3 тактовых импульсов) происходит запись входного сигнала, а в течение второго полупериода (единичное состояние на выходе генератора 3 тактовых импульсов) - считывание задержанного сигнала из блока 1 оперативной памяти, информационный выход которого является выходом устройства задержки. В описании даны временные диаграммы, пояснякицие работу устройства . 2 ил. 9 1C ГС tsS OQ Фиг, 1

ЮФ ю \

9 (21) 3789453/24-21 (22) 07.09.84 (46) 30.03.86. Бюл. У 12 (72) В.Н. Певцов, В.Н. Скосырев, Н.Д. Рябуха, А.С. Лебединский и Е.В. Хоменко (53) 621.374(088.8) (56) Самойлов Л.К. Устройство задержки информации в дискретной технике.

M.: Сов. радио, 1973, с. 203, рис. 5.12. (54) УСТРОЙСТВО ЗАДЕРЖКИ (57) Изобретение относится к области цифровой обработки сигналов. Цель изобретения — увеличение быстродействия за счет уменьшения времени перестройки на величину .задержки. Устройство содержит блок 1 оперативной памяти, цифровой ключ 2, генератор 3 тактовых импульсов, счетчик 4 адреса, регистр 5 управления величиной задержки и вычитатель 6. В устройстве задержки реализовано временное разделение режимов работы блока 1 временной памяти. В течение первого полупериода (нулевое. состояние на выходе генератора 3 тактовых импульсов) происходит запись входного сигнала, а в течение второго полупериода (единичное состояние на выходе генератора 3 тактовых импульсов) — считывание задержанного сигнала из блока 1 оперативной памяти, информационный выход которого является выходом устройства . задержки. В описании даны временные диаграммы, поясняющие работу устройства. 2 ил.

5 !

О

1 12

Изобретение относится к цифровой обработке сигналов, в частности к устройствам задержки информации в дискретной технике.

Цель изобретения — повышение быстродействия эа счет уменьшения времени перестройки величины задержки.

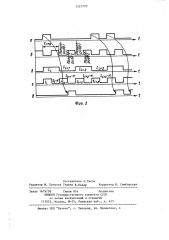

На фиг; 1 показана структурная схема устройства задержки; на фиг.2— временные диаграммы, Устройство задержки содержит блок 1 оперативной памяти, информационный вход и информационный выход которого являются входом и выходом устройства соответственно, цифровой ключ 2 и соединенные последовательно генератор 3 тактовых импульсов и счетчик 4 адреса. Устройство содержит также регистр 5 управления величиной задержки, вход которого является входом управления устройства, а выход соединен с информационным входом цифрового ключа 2, ;вычитатель 6, выход которого соединен с адресным входом блока 1 оперативной памяти,.а первый и второй входы соединень1 с выходом счетчика 4 адреса и выходом цифрового ключа 2 соответственно, выход генератора 3 тактовых импульсов соединен с управляющим входом цифрового ключа 2 и входом управления чтением-записью блока 1 оперативной памяти.

Устройство задержки работает следующим образом.

На информационный вход блока 1 оперативной памяти, который является входом устройства задержки, поступает входной сигнал в виде параллельного двоичного кода (в частном случае это может быть одноразрядный код), согласованного по напряжению с уровнями логики, на которой реализовано устройство.

На выходе генератора 3 тактовых импульсов формируется напряжение тактовых импульсов в виде меандра с некоторым периодом t, „ (фиг. 2б).

Период тактовых импульсов определяется требуемым шагом задержки или требуемым периодом временной дискретизации входного сигнала и равен меньшему из них.

Период тактовых импульсов состоит иэ первого полупериода (нулевое состояние на выходе генератора 3 тактовых импульсов), в течение которого происходит запись входного сигнала (фиг. 2а) в устройство задержки, и

21723 2 второго полупериода (единичное состояние на выходе генератора 3 тактовых импульсов), в течение которого происходит считывание задержанного сигнала из блока 1 оперативной памяти (фиг. 2д), информационный выход которого является выходом устройства задержки, Таким образом, в устройстве задержки реализовано временное разделение режимов работы блока 1 оперативной памяти.

Число ячеек N в блоке 1 оперативной памяти и число разрядов п счетчика 4 адреса зависит от требуемого максимального времени задержки

3.макс которое должно обеспечивать устройство задержки.

Счетчик 4 адреса имеет период повторения равный N и, соответственно, и выходов,,подключенных к первому входу п -разрядного двоичного вычитателя 6. При вычитании из большего числа меньшее на выходе вычитателя 6 формируется дополнительный код разности.

К второму входу вычитателя 6 подключен выход цифрового ключа 2. Последний под действием тактовых импульсов, поступающих на его управляющий вход, во втором полупериоде разрешает прохождение кода величины задержки от информационного входа на выход, а в первом полупериоде блоки-рует распространение кода величины задержки и формирует нулевое значение выходного кода.

Под действием тактовых импульсов счетчик 4 адреса периодически формирует на своих выходах возрастающий от О до (М-1) и-разрядный двоичный код адреса записи (фиг. 2в). В каждом периоце тактовых импульсов в первом полупериоде выходной код счетчика 4 адреса поступает без изменений через вычитатель 6 на адресный вход блока 1 оперативной памяти. По заданному адресу производится запись текущего кода входного сигнала в блок 1 оперативной памяти.

Во втором полупериоде блок 1 оперативной памяти работает в режиме считывания сигнала.

Задержка сигнала в устройстве происходит за счет того, что в каждом периоде тактовых импульсов имеется разность между адресом записи сигнала в блок 1 оперативной памяти и адресом .считывания сигнала. Указанная раз1723 4

Время записи г. „„кода задержки К в регистр 5 управления величиной задержки составляет доли периода тактовых импульсов

Так как в момент записи кода задержки в устройстве задержки не синхронизирован с тактовыми импульсами, считывание задержанного сигнала из устройства задержки можно начинать в следующем периоде тактовых импульсов.

Время перестройки величины задержки

t » будет равно периоду тактовых импульсов гти

15 Таким образом, в предлагаемом устройстве при организации задержки сигнала в каждом периоде тактовых импульсов записи входного сигнала в блок 1 оперативной памяти и считыва20 ния производятся по разным адресам, величина разности которых пропорциональна времени задержки t, что позволяет уменьшить время перестройки величины задержки и тем самым повы25 сить быстродействие устройства.

3 122 ность адресов пропорциональна величине задержки t устройства задержки и постоянна при неизменной величине задержки t .

Настройка устройства задержки на определенную величину задержки производится путем помещения в регистр 5 управления величиной задержки п-разрядного двоичного кода задержки К, который связан с величиной задержки t> следующим соотношением: к = — з- .

t гти

Полученный указанным способом п-разрядный двоичный код задержки К поступает на вход управления устройства задержки и заносится в регистр 5 управления величиной задержки. Источником кода задержки К может служить любое электронное устройство, управляемое как вручную, так и работающее в автоматическом режиме и сопряженное с устройством задержки.

Величину задержки сигнала t на

Ь выходе устройства задержки можно определить» как

=(К+0» ) гти

На фиг. 2г показан фрагмент циклограммы изменения на выходе вычитателя 6 кода адреса записи, начиная 30 с некоторого кода 1;, и кода адреса считывания К „ при постоянном значении кода задержки К. При вычитании во втором полупериоде из кода адреса записи 1,(0<1; М-1) кода задержки К на 35 выходе вычитателя 6 образуется и-разрядный двоичный код адреса считывания (состояние выхода заема в (п+1)-м разряде вычитателя 6 не учитывается).

К „=1; -К.

На фиг. 2а показан входной сигнал устройства задержки, а на фиг. 2д— задержанный входной сигнал на выходе устройства задержки при = гт гти

В предлагаемом устройстве задержки

45 функционирование может начинаться с произвольного состояния выходного кода счетчика 4 адреса (т.е. начальный адрес записи в ячейки блока 1 оперативной памяти может принимать любое значение от О до N-1), поэтому в устройстве задержки отсутствуют цепи начальной установки.

Формула изобретения

Устройство задержки, содержащее блок оперативной памяти, информационный вход и информационный выход которого являются входом и выходом устройства соответственно

» цифровои ключ и соединенные последовательно генератор тактовых импульсов и счетчик адреса, о т л и ч а ю— щ е е с я тем, что, с целью повышения быстродействия sa счет уменьшения времени перестройки величины задержки, в него введены регистр управле ния величиной задержки, вход которого является входом управления устройства, а выход соединен с информационным входом цифрового ключа, вычитатель» выход которого соединен с адресным входом блока оперативной памяти, а первый и второй входы соединены с выходом счетчика адреса и выходом цифрового ключа соответственно, выход генератора тактовых импульсов соединен с управляющим входом цифрового ключа и входом управления записыосчитыванием блока оперативной памяти.

1221723

Составитель А.Титов

Редактор М. Петрова Техред В.Кадар Корректор М. Самборская

Заказ 1619/58 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4