Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной и цифровой измерительной техники и может быть использовано для преобразования аналоговых величия в цифровые. Изобретение позволяет повысить точность аналого-цифрового преобразования за счет использованияизбыточных измерительных кодов, которые обеспечивают отсутствие разрьтов в «въпсодной характеристике устройства при больших отклонениях весов разрядов цифроаналогового преобразователя (ЦАП) от требуемых значений. При изготовлении устройства предварительно измеряют реальные значения весов разрядов ЦАП, которые в виде двоичных кодов фиксируют в блоке памяти. В процессе поразрядного аналого-цифрового преобразования по мере формирования значащих разрядов на входе ЦАП, соответствующие коды весов этих разрядов извлекаются КЗ блока памяти и суммирз/ются при помощи блока суммирования и регистра. После суммирования кода веса последнего значащего разряда преобразование заканчивается. Результат преобразования представлен в обычном двоичном коде. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК д) g Н 03 М 1 26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТБУ

В

° 7® э ф

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

r1O ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3782076/24-24 (22) 15..08.84 (46) 30.03.86. Бюл. Ф 12 (72) А.П.Стахов, В.И.Мойсеев, А.Д.Азаров, В.Я.Стейскал и Т.Н.Ва-, сильева (53) 681.325(088.8) (56) Швецкий Б.И. Электронные цифровые приборы. Киев.: Техника, 1981, с. 46, рис. 16.

Гитис Э.И., Пискулов Е.А. Аналого-цифровые преобразователи. М.:

Энергоиздат, 1981, с, 235, рис. 67а. (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЭОВАТЕЛЬ (57) Изобретение относится к области вычислительной и цифровой измерительной техники и может быть использовано для преобразования аналоговых величин в цифровые. Изобретение позволяет повысить точность аналого-цифрового преобразо„„SU„„1221?50 А вания засчет использованияизбыточных измерительных кодов, которые обеспечивают отсутствие разрывов в <выходной характеристике устройства при больших отклонениях весов разрядов цифроаналогового преобразователя (ЦАП) от требуемых значений.

При изготовлении устройства предварительно измеряют реальные значения весов разрядов ЦАП, которые в виде двоичных кодов фиксируют в блоке памяти. В процессе поразрядного аналого-цифрового преобразования по мере формирования значащих разрядов на входе ЦАП, соответствующие коды весов этих разрядов из" влекаются иэ блока памяти и суммируются при помощи блока суммирования и регистра. После суммирования кода веса последнего значащего разряда преобразование заканчивается.

Результат преобразования представлен в обычном двоичном коде. 1 ил.

1221750 изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования аналоговых величин в цифровые.

° Цель изобретения — повышение точности .аналого-цифрового преобразования;

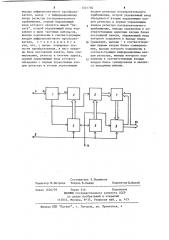

На чертеже представлена структурная схема аналого-цифрового преобразователя (АЦП).

АЦП содержит блок 1 сравнения, цифроаналоговый преобразователь (ЦАП) 2, регистр 3 последовательного приближения (РПП), входную шину 4, шину 5 "Запуск", блок 6 постоянной памяти, блок 7 суммирования, регистр 8, счетчик 9 адреса, .выходные шины 10, шину ll тактовых импульсов.

Погрешности аналого-цифрового преобразователя в значительной мере зависят от точности изготовления . цифроаналогового преобразователя в цепи обратной связи. При этом, если ЦАП реализован на основе неизбыточного двоичного кода, то наличие определенных отклонений весов разрядов цифроаналогового преобразователя от требуемых значений может привести к "разрывам" выходной характеристики устройства. Применение цифроаналогового преобразователя на основе избыточного измерительного кода (ИИК) позволяет устранить этот недостаток.

Одним из избыточных измерительных кодов является код Фибоначчи.

При изготовлении предлагаемого устройства предварительно измеряют реальные значения весов разрядов цифроаналогового преобразователя 2, которые представляют в виде двоичных кодов К: и фиксируют в блоке 6 памяти. В процессе поразрядного аналого-цифрового преобразования по мере формирования значащих, разрядов на входе ЦАП 2 коды К; весов этих разрядов извлекаются из блока 6 памяти и суммируются при помощи блоков 7 и 8. После суммирования кода веса последнего значащего разряда преобразование заканчивается. При этом сумма кодов К" всех значащих разрядов является результатом аналого-цифрового преобразования.

Работа устройства начинается при поступлении импульса запуска по шигде аф0, 1 ) цифра i-го разряда кода, сформированного на входе ЦАП 2 в процессе поразрядного уравновешивания, код двоичного эквивалента реального веса i-го разряда

ЦАП 2.

К

Формула изобретения

55 Аналого-цифровой преобразователь, содержащий блок сравнения, первый вход которого является входной шиной, второй вход подключен к н е 5 запуска, устанавливающего регистр 3 последовательного нриближения в исходное состояние, обнуляющего регистр 8 и счетчик 9 адреса.

5 В процессе преобразования входного аналогового сигнала А „ в выходной код К » производится уравновешивание

А» выходным компенсирующим сигналом

А ЦАП 2. Процесс уравновешивания производится устройством 3 управления последовательно от старших разрядов к младшим по методу поразрядного кодирования. При этом на каждом

i-м такте на выходе ЦАП 2 формируется аналоговый сигнал А1,. С помощью схемы 1 сравнения производится сравнение А„ с А „;. Выходной сигнал Y схемы 1 сравнения удовлетворяет < следующему условию:

1» если A» Ак,, О, если A„>A ..

Сигнал Y =0 разрешает считывание из

1 блока 6 памяти кода двоичного экви25 валента К реального веса i-го разряда, который подается на блок 7 суммирования, где производится его суммирование содержимым регистра

8. В случае f- ==1 считывание веса

1 из блока 6 постоянной памяти не происходит и содержимое регистра 8 не изменится.

В конце преобразования входной аналоговый сигнал А „ уравновешива35 ется выходным компенсирующим сигналом Ак„ЦАП 2 с точностью до младшего кванта.

Результат преобразования А„ в код К», сформированный в регистре

8, определяется по формуле

К„-Qa ° К;, 1 1

1221750

Составитель В.Першиков

Редактор M.Ïåòðoâà Техред В. Кадар Корректор Л.Патай

Заказ 1620/59

Тираж 81:6- Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, МоскВа, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 выходу цифроаналогового преобразователя, выход — к информационному входу регистра последовательного приближения, первый управляющий вход которого является шиной "3aпуск", второй управляющий вход подключен к шине тактовых импульсов, выходы подключены к соответствующим входам цифроаналогового преобразователя, отличающийся тем, что, с целью повышения точности преобразования, в него введены блок постоянной памяти, блок суммирования, регистр и счетчик адреса, первый управляющий вход которого объединен с первым управляющим входом регистра и вторым управляющим входом регистра последовательного приближения, второй управляющий вход объединен с вторым управляющим входом регистра и первым управляющим входом регистра последовательного приближения, выходы подключены к соответствующим адресным входам блока постоянной памяти, управляющий вход которого подключен к выходу блока

1п сравнения, выходы — к соответствующим первым входам блока суммирования, выходы которого подключены к соответствующим информационным входам регистра, выходы которого подключены к соответствующим вторым входам блока суммирования и являются выходными шинами.