Преобразователь двоичного кода в двоично-десятичный

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники, предназначено для преобразования двоичных кодов нескольких операндов в двоично-десятичные коды с вьщачей их параллельнопоследовательным кодом и может быть использовано в устройстве отображения информации (УОИ) метеорологической радиолокационной станции (МРЛ). Целью изобретения является расширение функциональных возможностей за счет обеспечения возможности преобразования разноформатных кодов и упрощение преобразователя. Это достигается за счет того, что в преобразователь, реализующий метод последовательного вычитания эквивалентов, введен блок оперативной памяти, первый и второй регистры адреса и два элемента ИЖ, причем адресные входы блоков постоянной и оперативной памяти соединены соответственно с выходами первого и второго регистров адреса, входы которых соединены соответственно с входами выбора режима преобразования и выбора режима регистрации преобразователя , оперативная память используется для хранения отдельных рчзрядов двоично-десятичного кода, а допустимость очередного вычитания эквивалента определяется по сигналу переноса накопительного сумматора, 1 з.п. ф-лы. 4 ил. i (О С

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 4 Н 03 M 7/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3699437/24-24 (22) 09.02.84 (46) 30.03.86. Бюл. ¹ 12 (72) Е.Ф. Киселев и О.А. Кузина (53) 681.325(088.8) (56) Авторское свидетельство СССР № 451996, кл. G 06 F 15/20, 1972.

Авторское свидетельство СССР № 864278, кл. G С6 F 5/02, 1978. (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА

s gaomHo-ДЕСЯТИЧНЫЙ (57) Изобретение относится к области вычислительной техники, предназначено для преобразования двоичных кодов нескольких операндов в двоично-десятичные коды с выдачей их параллельнопоследовательным кодом и может быть использовано в устройстве отображения информации (УОИ) метеорологической радиолокационной станции (ИРЛ).

Целью изобретения является расширение функциональных возможностей за счет обеспечения возможности преобразова-. ния разноформатных кодов и упрощение преобразователя. Это достигается за счет того, что в преобразователь, реализующий метод последовательного вычитания эквивалентов, введен блок оперативной памяти, первый и второй регистры адреса и два элемента ИЛИ, причем адресные входы блоков постоянной и оперативной памяти соединены соответственно с выходами первого и второго регистров адреса, входы которых соединены соответственно с входами выбора режима преобразования и выбора режима регистрации преобразователя, оперативная память используется для хранения отдельных разрядов двоично-десятичного кода, а допустимость очередного вычитания эквивалента определяется по сигналу переноса накопительного сумматора.

1 з.п. ф-лы. 4 ил.

1221757

Регистры 1 и 2 адреса выполнены в виде счетчиков, входы установки и счетные входы которых являются входами сброса и разрешения записи регистров адреса соответственно. 50

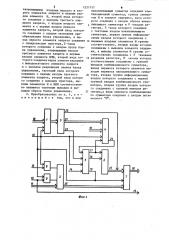

Накапливающий сумматор 4 содержит (фиг. 2) комбинационный сумматор 27, регистр 28, группу элементов И 29 и элемент 30 задержки.

Блок 5 управления содержит (фиг.3) триггер 31, элементы 32 и 33 запрета, элемент И 34, элемент 35 запрета, элемент 36 задержки и элемент ИЛИ 37.

Изобретение относится к вычислительной технике, предназначено для преобразования двоичных кодов нескольких операндов в двоично-десятичные коды с выдачей их параллельно- 5 последовательным кодом и может быть использовано в устройстве отображео ния информации (УОИ) метеорологической радиолокационной станции (MPJI) .

Цель изобретения — расширение 10 функциональных возможностей преобразователя за счет обеспечения возможности преобразования разноформатных кодов и упрощение преобразователя.

На фиг. 1 приведена структурная схема преобразователя; на фиг. 2— блок-схема накапливающего сумматора, на фиг. 3 — схема блока управления; на фиг. 4 — схема блока оперативной 20 памяти.

Преобразователь двоичного кода в двоично-десятичный (фиг. 1) содержит регистры 1 и 2 адреса, блбк

3 постоянной памяти, накапливающий 25 сумматор 4, блок 5 управления, счетчик 6, блок 7 оперативной памяти, первый 8 и второй 9 элементы ИЛИ, вход 10 выбора режима преобразования вход 11 выбора режима регистрации„ 30 вход 12 пуска,. вход 13 сброса, первый и второй тактовые входы 14 и 15, информационный вход 16 преобразователя, тактовый выход 17 блока управления, выход 18 сброса блока управления, выход 19 разрешения записи блока управления, группы выходов 20 и 21 второго и первого регистров адреса, выход 22 признака наличия запятой, выход 23 признака окончания преобра- 40 эования блока постоянной памяти, выход 24 переноса сумматора, группу выходов 25 счетчика, группу выходов 26 преобразователя.

Блок 7 оперативной памяти (фиг.4) содержит оперативное запоминающее устройство (ОЗУ) 38, шинный формирователь 39 и элемент НЕ 40.

Преобразователь работает в двух режимах: в режиме преобразования и в режиме потетрадной выдачи двоичнодесятичных кодов.

В режиме преобразования на вход

10 преобразователя поступает адрес

Ф10 старшего из набора двоично-десятичных эквивалентов, соответствующего данному операнду, на вход 11 адрес старшей тетрады двоично-десятичного кода данного операнда в блоке 7, на вход 12 — импульс И12 запуска, на вход 14 — тактовые импульсы ТИ14, на вход 16 — преобразуемый двоичный код Ф16.

Преобразование и --разрядногодвоичного кода операнда Ф16 основано на последовательном сложении положительного кода Ф16 с отрицательными значениями двоичных эквивалентов десятичных разрядов меры, соответствующей цанному операнду.

Дополнительный код Ф21 двоичного эквивалента комбинационно вырабатывается на выходе 21 блока 3, с выхода

22 которого снимается признак П22 наличия запятой, а с выхода 23— признак П23 останова.

Число сложений в дополнительном коде до получения переноса в (h+1)-й разряд подсчитывается счетчиком 6, с выхода которого тетрада двоичнодесятичного кода заносится в блок 7 по адресу, формируемому счетчиком 2.

До начала преобразования на преобразователь поступают коды Ф10,Ф11, Ф16. Цикл преобразования начинается с поступлением И12, по которому коды Ф10 и Ф11 заносятся в регистры

1 и 2 соответственно, а код Ф16 — в регистр 28 накапливающего сумматора

4 ° Триггер 31 блока 5 переходит в единичное состояние, а с выхода 18 блока 5 поступает импульс И 18 обнуления счетчика 6.

С приходом ТИ14 значения (Ф16+Ф21} с выхода сумматора 27 заносится в регистр 28 по окончании импульса

И1?, поступающего с выхода 17 блока

5. На выходе сумматора 27 формируется новое значение суммы (Ф16+Ф21), а содержимое счетчика 6 увеличивается на 1. Сложения продолжаются до тех пор, пока на выходе 24 суммато1221757 4

55 ра 4 сохраняется признак переноса

П24-1. Если в промежутке между тактами возникает П24=-0, то в новом такте передачи значения (Ф16+Ф21) в регистр

28 не происходит, а на выходе 19 блока 5 вырабатывается импульс И19, по которому полученная в предыдущем такте тетрада двоично-десятичного кода совместно с признаком П22 заносится в блок 7 по адресу, определяемому регистром 2. По окончании И19=1 содержимое регистров адреса 1 и 2 увеличивается на 1, а через задержку

C счетчик 6 обнуляется по И18.

Если полученная тетрада не последняя для данного операнда, то на выходе 23 блока 3 сохраняется П23=0 и по ТИ14 содержимое регистра 28 суммируется с новым кодом Ф21 до возникновения П24=0. При П23=1 триггер 31 блока 5 переходит в нулевое состояние, запрещая формирование И17 и И19.

Входы-выходы шинного формирователя

39 при И19=0 переходят в третье состояние и отключаются от входоввыходов ОЗУ. 38, которое таким образом активизируется на считывание.

В режиме выдачи триггер 31 находится в нулевом состоянии, на вход

13 преобразователя поступаст импульс сброса И13, на. вход 11-начальный адрес Ф11 выдаваемой последовательности тетрад двоично-десятичных кодов, а на вход 15- тактовые импульсы ТИ15.

По И13 код Ф11 заносится в регистр 2, и с частотой ТИ15 с выхода

26 блока 7 снимается требуемая послецовательность двоично-десятичных кодов. При этом ТИ15 выдаются в качестве импульсов считывания.

Формула изобретения

Преобразователь двоичного кода в двоично-десятичный, содержащий блок постоянной памяти, накапливающий сумматор, блок управления и счетчик, счетный вход которого соединен с тактовым выходом блока управления и тактовым входом накапливающего сумматора, первая группа информационных входов которого соединена с группой информационных входов преобразователя, вход пуска которого соединен с входом пуска блока .управления и входом сброса накапливающего сумматора, вторая группа информационных входов которого соеди5

45 иена с группой кодовых выходов блока постоянной памяти, а выход переноса накапливающего сумматора соединен с входом готовности тетрады блока управления, тактовый вход которого соединен с первым тактовым входом преобразователя, выход сброса блока управления соединен с входом сброса счетчика, о т л и ч а ю— шийся тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности преобразования разноформатных кодов и упрощения преобразователя, в него введены первый и второй регистры адреса, первый и второй элементы

ИЛИ и блок оперативной памяти, а блок управления содержит триггер, три элемента запрета, элемент И, элемент ИЛИ и элемент задержки, причем .адресные входы блоков постоянной и оперативной памяти соединены соответственно с выходами первого и второго регистров адреса, информационные входы которых соединены соответственно с входом выбора режима преобразования и входом выбора режима регистрации преобразователя, вход пуска которого соединен с входом сброса первого регистра адреса и первым входом. первого элемента ИЛИ, второй вход которого соединен с входом сброса преобразователя, второй тактовый вход которого соединен с первым входом второго элемента ИЛИ и с тактовым выхоцом преобразователя, группа информационных выходов которого соединена с группой выходов блока оперативной памяти, вход разрешения записи которого соединен с выходом разрешения записи блока управления, с входом разрешения записи первого регистра адреса и вторым входом второго элемента ИЛИ, выход которого соединен с входом разрешения записи второго регистра адреса, вход сброса которого соединен с выкодом первого элемента ИЛИ, вход признака окончания преобразования блока управления соединен с выходом признака останова блока постоянной памяти, выход признака наличия запятой которого соединен с входом старшего разряда группы числовых входов блока оперативной памяти, остальные разряды, группы числовых входов которых соединены с группой выходов счетчика, вход готовности тетрады блока управления соединен с

5 12 запрещающими входами первого и второго элементов запрета и первым входом элемента И, второй вход которого соединен с выходом третьего элемента запрета, с входом второго элемента и с первым входом первого элемента запрета, второй вход которого соединен с входом окончания преобразования блока управления, а выход первого элемента запрета соединен с синхровхадом триггера, 6 -вход которого соединен с входом пуска блока управления, запрещающим входом третьего элемента запрета и первым входом элемента ИЛИ, второй вход которого соединен через элемент задержки с выходомвторого элемента запрета и с выходом разрешения записи блока управления, тактовый вход которого соединен с первым входом третьего элемента запрета, второй вход которо

ro соединен с выходом триггера, выходы элементов И и ИЛИ соответственно являются тактовым выходом и вы.ходом сброса блока управления.

2. Преобразователь по п. 1, о т— л и ч а ю шийся тем, что в нем

21757 6 накапливающий сумматор содержит комбинационный сумматор, группу элементов И и элемент задержки, вход которого соединен с входом сброса накап ливающего сумматора и Я -входом регистра, С -вход которого соединен с тактовым входом накапливающего сумматора, первая группа информационных входов которого соединена с

10 первыми входами элементов И группы соответственно, вторые входы которых соединены с выходом элемента задержки, а выходы элементов И группы соответственно соединены с 8 -входами

15 разрядов регистра, D -входы которых соответственно соединены с группой выходов комбинационного сумматора, выход переноса которого является выходом переноса накапливающего сумма20 тора, вторая группа информационных входов которого соединена с первой группой входов комбинационного сумматора, вторая группа входов которого соединена с группой выходов ре25 гистра,а вход переноса комбинационно. го сумматора соединен с входом логического "О".

1221757

1221757

Со ст ав ит ель N. Аршав ский

Техред Л.Олейник Корректор А.Ференц

Редактор И. Касарда

Филиал ППП "Патент", r. Ужгород, ул.Проектная, 4

) Заказ 1621/60 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5