Устройство для извлечения корня @ -й степени

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, является дополнительным к основному авт. св. № 883898 и отличается введением анализатора аргумента, что обеспечивает повышение быстродействия устройства . Анализатор позволяет без проведения вычислений определять значения разрядов искомого корня вплоть до первой значащей цифры аргумента включительно. Информационный и управляющие входы анализатора подключены соответственно к выходу регистра аргумента и к щестому выходу блока микропрограммного управления . Выход анализатора подключен к третьему входу коммутатора результата и к входу признака перехода к подпрограмме вычисления блока микропрограммного управления , вход установки показателя степени корня анализатора является одноименным входом устройства. 13 п. ф-лы, 4 ил. ю to со to IN:) ел

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1223225 A ш 4 G 06 F 7 552

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 883898 (21) 3798879/24-24 (22) 08.10.84 (46) 07.04.86. Бюл. № 13 (72) Г. А. Руденко, В. Н. Панасюк, А. В. Либерман и Н. В. Белинский (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 883898, кл. G 06 F 7/552, !979. (54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ

КОРНЯ и-й СТЕПЕНИ (57) Изобретение относится к вычислительной технике, является дополнительным к основному авт. св. № 883898 и отличается введением анализатора аргумента, что обеспечивает повышение быстродействия устройства. Анализатор позволяет без проведения вычислений определять значения разрядов искомого корня вплоть до первой значащей цифры аргумента включительно.

Информационный и управляющие входы анализатора подключены соответственно к выходу регистра аргумента и к шестому выходу блока микропрограммного управления. Выход анализатора подключен к третьему входу коммутатора результата и к входу признака перехода к подпрограмме вычисления блока микропрограммного управления, вход установки показателя степени корня анализатора является одноименным входом устройства. 13 п. ф-лы, 4 ил.

)223225!

Изобретение относится к цифровой вычислительной технике и может быть использовано в специализированных вычислительных устройствах, цифровых измерительных приборах, функциональных преобразователях и является дополнительным к основному устройству по авт. св. № 883898.

Цель изобретения — повышение быстродействия устройства за счет исключения вычислений при наличии нулевых значений в группе разрядов аргумента.

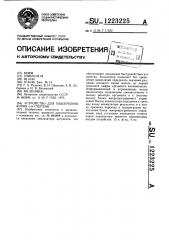

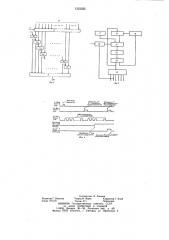

На фиг. 1 представлена структурная схе, ма предлагаемого устройства; на фиг. 2— функциональная схема одного из возможных вариантов выполнения анализатора аргумента; на фиг. 3 — функциональная схема одного из возможных вариантов выполнения блока микропрограммного управления; на фиг. 4 — временная диаграмма работы блока микропрограммного управле ния.

Устройство содержит (фиг. 1) блок 1 микропрограммного управления, регистр 2 начального коэффициента, регистр 3 аргумента, регистр 4 результата, коммутатор 5 младшего коэффициента, коммутатор 6 результата, формирующий коммутатор 7, сдвиговый регистр 8, сумматор 9, анализатор

10 аргумента, Анализатор 10 аргумента содержит сдвиговый регистр 11, параллельный информационный вход и вход сдвига которого являются информационным и управляющим входами 12 и 13 анализатора 10, и элементов ИЛИ 14, коммутатор 15, выход которого является выходом анализатора 16, управляющий вход коммутатора 15 (не показан) является входом установки показателя степени корня анализатора 10 и устройства.

Блок микропрограммного управления содержит регистр 17 начального адреса, мультиплексор 18, счетчик 19 переходов, элемент

И 20, коммутатор 21 адреса, счетчик 22 адреса, блок 23 памяти, дешифратор 24 микрокоманд.

Устройство работает следующим образом.

Определение искомого корня производится с точностью до m двоичных разрядов и длится m циклов, в каждом из которых определяется значение одного разряда корня. Работа устройства начинается занесением аргумента в регистр аргумента, после чего в счетчике 22 адреса блока 1 устанавливается начальный адрес микропрограммы анализа аргумента, и анализатор 10 аргумента производит его анализ следующим образом.

Если р- и разрядов аргумента (где р=О, I, 2, ..., m), начиная с первого справа после запятой, имеют нулевые значения, то р разрядов после запятой значения корня тоже равны нулю.

Если (р.1+1)-й разряд аргумента (где f.=0, 1, 2, ..., п) равен единице, то (р+1)-й

35 и

35 разряд после запятой значения корня тоже ра вен еди н и це.

Таким образом, в результате анализа, не выполняя никаких вычислений, определяются значения разрядов корня вплоть до первой значащей цифры (единицы) включительно, т. е. путем вычисления определяются значения только m — (р + 1) оставшихся разрядов корня.

Предположим, извлекается корень четвертой степени п=4. В этом случае к выходу коммутатора 15 будет подключен четвертый информационный вход. Содержимое регистра 3 аргумента через входы анализатора 12 аргумента записывается в сдвиговый регистр I I, Разряды аргумента будут анализироваться по четыре разряда, начиная с первого справа после запятой. Выходы сдвигового регистра 11 подключены к. входам и элементов ИЛИ !4, ..., 14,. Элементы ИЛИ 14 соединены между собой так, что при появлении единицы на выходе одного из элементов, выходы всех последующих элементов тоже устанавливаются в единичное состояние. Кроме того, выходы элементов ИЛИ 14i, ..., 14. соединены с входами коммутатора 15, который коммутирует один из п входных сигналов (в нашем случае четвертый) на выход.

Если первые четыре разряда аргумента равны нулю, то на выходе четвертого элемента ИЛИ 144 тоже будет ноль, который через коммутатор 15 и выход анализатора

l6 аргумента поступает на третий вход коммутатора 6 результата, и через него устанавливает первый разряд регистра 4 результата в состояние «О», а также поступает на вход блока 1, не оказав воздействия на его работу. После этого под воздействием управляющего сигнала с шестого выхода блока 1 информация в сдвиговом регистре II сдвигается влево на п= 4 разряда и дальше аналогичным образом анализируются следующие четыре разряда аргумента. Если и они все равны нулю, то второй разряд регистра 4 результата тоже принимает значение «О>. И только если очередные четыре разряда аргумента содержат хотя бы одну единицу, то на выходе элемента ИЛИ 144 появляется единица, под воздействием которой очередной разряд регистра 4 результата принимает единичное значение. Эта же единица поступает на вход блока 1 и под ее воздействием в счетчик 22 адреса блока 1 заносится начальный адрес микропрограммы вычисления по основному алгоритму, блок I прекращает выдачу управляющих сигналов на анализатор 10 аргумента и устройство переходит к вычислению остальных разрядов искомого корня.

Вход блока управления предназначен для осуществления перехода устройства от анализа аргумента на вычисление корня по основному алгоритму.!

223225

Второй выход блока управления наряду с занесением данных в разряды регистра

4 результата при вычислении корня по основному алгоритму осуществляет также занесение данных в разряды регистра 4 ре. зультата и при анализе аргумента.

При анализе аргумента блок работает следующим образом.

После занесения аргумента в соответствующий регистр в счетчике 22 адреса устанавливается начальный адрес микропрограммы анализа аргумента, которая размещена в блоке 23 памяти. Под воздействием тактовых импульсов счетчик 22 адреса последовательно перебирает адреса блока 23 памяти, с выхода которого микрокоманды поступают на вход дешифратора 24 микрокоманд. Шестой выход дешифратора 24 микрокоманд (шестой выход блока управления) формирует импульсы адреса для сдвигового регистра 11 анализатора аргумента.

После сдвига аргумента на и разрядов влево второй выход дешифратора 24 микрокоманд (второй выход блока управления) формирует импульс занесения, определенных в результате анализа нуля либо единицы в очередной разряд регистра 4 результата.

Этот же импульс с второго выхода дешифратора 24 микрокоманд поступает на первый вход элемента И 20, на второй вход которого поступает сигнал с выхода анализатора 10 аргумента. После завершения анализа очередных разрядов аргумента импульс с второго выхода дешифратора 24 микрокоманд открывает элемент И 20, и на его выход проходит сигнал с выхода анализатора !О аргумента, который своим нулевым значением, поданным на первый вход коммутатора 21 адреса, не оказывает влияния на коммутатор 21 адреса, а единичным значением подключает к его выходу регистр 17 начального адреса, в результате чего в счетчик 22 адреса заносится начальный адрес микропрограммы вычисления корня по основному алгоритму (фиг. 4).

Быстродействие предлагаемого устройства, например при m=8, при условии определения в результате .анализа в самом неблагоприятном случае только одного разряда искомого корня будет в !,14 раза выше, а в самом благоприятном случае определения в результате анализа семи разрядов корня быстродействие будет выше в 8 раз по сравнению с известным устройством.

Формула изобретения

1. Устройство для извлечения корня п-й степени по авт. св. № 883898, отличающееся тем, что, с целью повышения быстродействия за счет исключения вычислений при наличии нулевых значений в группе разрядов аргумента, в него введен анализатор аргумента, информационный и управляющий входы которого соединены соответственно с выходом регистра аргумента и шестым выходом блока микропрограммного управления, выход анар лизатора аргумента соедин"н с третьим входом коммутатора результата и с входом признака перехода к подпрограмме вычисления блока микропрограммного управления, вход установки показателя степени корня анализатора аргумента является одно именным входом устройства.

2. Устройство по п. 1, отличающееся тем, что анализатор аргумента содержит сдвиговый регистр, и элементов ИЛИ и коммутатор, параллельный информационный вход и вход сдвига сдвигового регистра являются информационным и управляющим входами анализатора аргумента, выход которого соединен с выходом коммутатора, выходы разрядов сдвигового регистра соединены с первыми входами соответствующих элементов

З5 ИЛИ, выход i-го элемента ИЛИ (i 1, ..., и-1) подключен к второму входу i+ 1-го . элемента ИЛИ, второй вход первого элемента ИЛИ подключен к шине логического нуля устройства, выходы элементов

ИЛИ подключены к информационным вхо40 дам коммутатора, управляющие входы которого являются входом установки показателя степени корня анализатора аргумента;

1223225 (1д

Фиг Е

ЦЪг Х донесение данесен

t-йбы блока

v tp егиста г-и бык. блока упр.

ОФис аргумента на и- рагрлдоб бледа б-й бььч блока упр. дыл бл рлр быг ало»ис.орлу мента) дьмод олень и блока упр

Пролбпение,. г л при Л оналиге аргумента данесение бсчетиип адреса начального адреса уиссг. Ф

Составитель А. Ушаков

Редактор Г. Волкова Техред И. Верес Корректор Т. Колб

Заказ 1714/51 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4