Устройство для контроля логических блоков

Иллюстрации

Показать всеРеферат

Устройство относится к вычислительной технике и может быть использовано при тестовом диагностировании блоков. Цель изобретения - повышение достоверности контроля. Устройство содержит генератор .тестов, образован- ;ный генератором тактовых импульсов и счетчиком, эталонный блок, блоки обнаружения входов/выходов, блоки анализа, коммутаторы, регистр, блок индикации. Устройство работает по принципу сравнения эталонных реакций и реакций с выходов контролируемого блока. Длительность вероятных несовпадений выходных реакций определяется коэффициентом деления частоты калиброванного генератора тактовых импульсов и коэффициентом пересчета блоков анализа. При несовпадении значений реакций по длительности на одном или нескольких выходах контролируемого логического блока,блок анализа , соответствующий каждому выходу, формирует сигнал, который запоминается регистром и вьгоодится из индикации . 3 ил. с сл

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

09) (21) А 1)4 G 06 F 11/26

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТ0РСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3802275/24-24 (22) 10.10.84 (46) 07.04.86. Бюл. У 13 (72) А.Н.Пархоменко, В.В.Голубцов и И.О.Воинов (53) 681.3 (088.8) (56) Авторское свидетельство СССР

Ф 1038947, кл. G 06 F 11/22, 1982.

Авторское свидетельство СССР

У 633019, кл. G 06 F 11/00 .1976. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ (57) Устройство относится к вычислительной технике и может быть использовано при тестовом диагностировании блоков. Цель изобретения — повьппение достоверности контроля. Устройство содержит генератор .тестов, образованный генератором тактовых импульсов и счетчиком, эталонный блок, блоки обнаружения входов/выходов, блоки анализа, коммутаторы, регистр, блок индикации. Устройство работает по принципу сравнения эталонных реакций и реакций с выходов контролируемого блока. Длительность вероятных несовпадений выходных реакций определяется коэффициентом деления частоты калиброванного генератора тактовых импульсов и коэффициентом пересчета блоков анализа. При несовпадении значений реакций по длительности на одном или нескольких выходах контролируемого логического блока, блок анализа, соответствующий каждому выходу, а формирует сигнал который запоминается регистром и выводится из ин; икации. 3 ил.

Ф 12

Изобретение .относится к автоматике и вычислительной технике и может быть использовано для автоматизированной проверки работоспособности логических блоков ЭВМ.

Цель изобретения — повышение достоверности контроля.

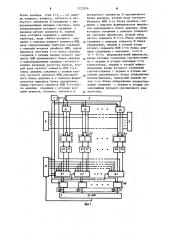

На фиг. 1 показана структурная схема предлагаемого устройства; на фиг. 2 — схема блока анализа; на фиг. „,: .3 — схема блока управления.

Устройство содержит генератор 1 тактовых имПульсов, счетчик 2, и блоков обнаружения входов/выходов 3.1

З.п, (где n — число входов/выходов контролируемого логического блока), контролируемый логический блок 4, эталонный блок 5, и коммутаторов 6. 16.п, 2п формирователей 7.1 - 7,п и

8.1 - 8.п импульсов, и блоков 9.1

9.п анализа, регистр 10 памяти, блок

11 индикаций, элемент ИЛИ 12, блок 13 управления.

Блок анализа (фиг.2) содержит формирователь 14 импульсов, элементы

ИЛИ 15 †. 17, триггер J8, элементы

И 19 — 23, счетчик 24.

Блок управления (фиг.3) содержит генератор 25 тактовых импульсов, делитель 26 частоты, элеменг И 27, формирователь 28 импульса, триггер 29, шифратор 30, переключатель 31.

Блоки обнаружения входов/выходов выполнены как в известном устройстве.

Сигнал для управления коммутаторами

6,1 — 6,п, выполненными на элементах

И, снимается с прямого выхода D-триггера.

Устройство работает следующим образом.

После включения питания на единичный вход триггера 29 подается высокий уровень, который переводит триггер.29 в единичное состояние. Передним фронтом положительный потенциал поступает с выхода триггера 29 на вход формирователя 28 импульсов, этот импульс устанавливает в исходное состояние счетчик 2, блоки 3 обнаружения входов/выходов (Р-триггер), блоки 9 анализа и регистр 10 памяти.

Положительный: потенциал с выхода триггера 29 поступает на вход элемента И 27 и на входы элементов ИЛИ 16 и 17, на вход пуска генератора 1 тактовых импульсов и на входы разрешения блоков 3 обнаружения входов/выходов. Калиброванная частота генератора 25 тактовых импульсов через дели23234 2

55 тель 26 частоты и открытый элемент

И 27 поступает на вход элемента И 19 в каждый из блоков 9 анализа.

При определении входов/выходов блоки 3 обнаружения входов/выходов разрешают прохождение входных воздействий от счетчика 2 на входы контролируемого блока 4 и эталонного блока 5, и запрещают прохождение этих сигналов через коммутаторы 6 низким уровнем с первого и второго выхода блоков обнаружения входов/выходов.

На выходные контакты контролируемого

4 и эталонного 5 блоков логические уровни с разрядных выходов счетчика 2 не оказывают влияния, так как на выходах блоков 3 обнаружения входов/выходов расположены элементы И с открытыми коллекторными выходами, Одновременно с прямого выхода Э-триггера поступает потенциал на управляющие входы коммутаторов 6, который открывает коммутаторы для прохождения выходных реакций контролируемого 4 и эталонного 5 блоков.

Устройство работает по принципу сравнения выходных реакций контролируемого и эталонного блоков. Длитель- ность возможного несовпадения выходI ных реакций определяется коэффициентом деления частоты калиброванного генератора тактовых импульсов 25 и коэффициентом пересчета блоков анали- за 9.

При несовпадении значения логических уровней одного или нескольких выходов по длительности выше установленного предела на нулевом выходе счетчика 24 появляется сигнал, который поступает на информационные входы соответствующего разряда регистра 10 памяти и через элемент ИЛИ 12 на нулевой вход триггера 29, что переводйт триггер 29 в нулевое состояние. В этом случае устройство останавливает свою работу и на блоке индикации высвечивается номер или номера несовпадающих выходных контактов. При совпадении логических уровней выходных реакций эталонного 5 и контролируемого 4 логических блоков на всех состояниях счетчика 2 контролируемый логический блок признается работоспособным.

Двоично-десятичный счетчик 24 устанавливается в исходное состояние (заносится коэффициент пересчета) при каждом изменении состояния счетчика 2 с помощью имульса от генера3 12 тора 1 тактовых импульсов через формирователь 14 импульсов и элемент

ИЛИ 17. Поэтому счет допустимых интервалов несовпадения производится блоками 9 анализа на каждом новом состоянии счетчика 2.

Отсчет интервалов несовпадения производится следующим образом.

Формирователи 7 и 8 импульсов по фронту и срезу входного сигнала вырабатывают импульсы при любом изменении выходных реакций эталонного 5 и контролируемого 4 логических блоков. При изменении выходной реакции эталонного логического блока 5 формирователь 7.импульсов вырабатывает импульс, который через элемент ИЛИ 15 поступает на счетный вход триггера

18 и устанавливает его в единичное состояние, разрешая тем самым поступление калиброванной частоты генератора 25 тактовых импульсов через элемент И 19 на двоично-десятичный счетчик 24. Изменение выходной реакции на соответствующем выходе контролируемого логического блока 4 приводит к выработке аналогичного импульса формирователем 8, в результате чего триггер 18 установится в нулевое. состояние, которое запрещает прохождение калиброванной .частоты на счетчик 26 через элемент И 19. Если интервал несовпадения изменений выход,ных реакций контролируемого и эталонного логических блоков не превышает . допустимую величину, то сигнал несовпадения на выходе двоично-десятичного счетчика 24 не появляется, а счетчик устанавливается в исходное состояние для проведения контроля несовпадений на следующем тестовом наборе °

При помощи переключателя 31 с шифратора 30 снимается код, поступающий через коммутатор, образованный элементами И 20 — 23, на информационные входы счетчика 24. Применение делителя 26 в блоке 13 управления предоставляет воэможность расширить диапаэоч частоты измерения,,что, в свою очередь, позволяет проводить контроль более широкой номенклатуры логических блоков, Формула изобретения

Устройство для контроля логических блоков, содержащее генератор тактовых импульсов, счетчик, и блоков обнаружения входов/вьмодов (где п —число входов/вв|ходов контролируемого

23234 4 логического блока), эталонный блок, регистр памяти, блок индикации и блок управления, содержащий формирователь импульса, причем первые выходы всех блоков обнаружения входов/выходов соединены с. соответствующими входами/

/выходами эталонного блока, синхровходы и блоков обнаружения входов/выходов соединены с соответствующими разрядными выходами счетчика, вход сброса которого соединен с выходом формирователя импульсов блока управления, с входами сброса и блоков обнаружения входов/выходов и входом сброса регистра памяти, входы разрешения каждого блока обнаружения входов/выходов соединены с выходом форми. рователя импульсов и установочными входами соответствующих разрядов регистра памяти, вторые выходы и блоков обнаружения входов/выходов соединены с соответствующими входами/выходами контролируемого логического блока, выходы регистра памяти соединены с соответствующими информационными входами блока индикации, о т— л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, оно содержит и коммутаторов, 2п

30 формирователей импульсов, элемент ИЛИ и и блоков анализа, а блок управления содержит генератор тактовых импульсов, переключатель, делитель частоты, триггер, шифратор и элемент И, а каждый блок анализа содержит формироваЗ5 тель импульсов, переключатель, первый, второй и третий элементы ИЛИ, первый, второй, третий, четвертый и пятый элементы И и счетчик, причем

I вход пуска устройства соединен с

40 единичным входом триггера, нулевой вход которого соединен с выходом элемента ИЛИ, выход триггера соединен с входом формирователя импульсов блока управления, с первым входом

5 элемента И и входом пуска генератора тактовых импульсов, второй вход элемента И соединен с выходом делителя частоты, вход которого соединен с выходом генератора тактовых импуль5О сов блока управления, информационные входы шифратора соединены с неподвижными контактами переключателя, подвижный контакт которого подключен к шине единичного потенциала устройст55 ва, выходы шифратора соединены с первыми входами первого, второго, третьего и четвертого элементов И каждого блока анализа, в каждом i-м

1223234 блоке анализа (где i=1,...,n) выходы первого, второго, третьего и четвертого элементов И соединены с информационными входами счетчика, вход . синхронизации которого соединен. с выходом пятого элемента И, первый вход которого соединен с выходом триггера, вход сброса которого соединен с выходом первого элемента ИЛИ, вход синхронизации триггера соединен с выходом второго элемента ИЛИ, выход переноса счетчика i-го блока анализа соединен с первым входом первого элемента ИЛИ одноименного блока анализа и информационными входами соответствующих разрядов регистра памяти, второй вход первого элемента ИЛИ i-го блока анализа соединен с первым входом третьего элемента ИЛИ одноименного блока анализа и с выходом формирователя импульса блока управления, выход третьего элемента ИЛИ i-го блока анализа соединен с вторыми вхо-. дами первого, второго, третьего и четвертого элементов И одноименного блока анализа, второй вход третьего элемента ИЛИ i-го блока анализа сое5 динен с выходом формирователя импульсов одноименного блока анализа, вход которого соединен с выходом генератора тактовых импульсов, второй вход пятого элемента И i-го блока анализа

10 соединен с выходом элемента И блока управления, первый и второй входы второго элемента ИЛИ i-ro блока анализа соединены с выходами i-ro u (i + 1)-го формирователей импульсов, 15 входы которых соединены соответственно с первым и вторым выходами i-го коммутатора, первый и второй информационные входы которого соединены соответственно с первым и вторым вы о ходами одноименного блока обнаружения входов/выходов, инверсный первый выход -го блока обнаружения входов/выходов соединен с первым и вторым управляющими входами одноименного.коммутатора, 1223234

1223234

)

1715/52 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Заказ филиал ППП "Патент", r.Óæãîðoä, ул.Проектная,4

Составитель А. Сиротская .

Редактор А.Шандор Техред Л.Олейник Корректор М,Демчик