Устройство для отображения графической информации

Иллюстрации

Показать всеРеферат

Изобретение относится к устройствам отображения информации и предназначено для воспроизведения графиков на индикаторных (плазменных) панелях. Устройство содержит индикаторную панель, блоки ключей, блок памяти, формирователь, дешифратор, счетчики, преобразователи кодов, управляемый делитель частоты. Устройство обеспечивает высокое качество воспроизведения графической информации за счет устранения эффекта изменения вида изображения, возникающего при воспроизведении изображения в масштабе уменьшения. 1 ил. ю 1C со ю ас со

СОКИ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (Ю 4 G 09 G 3 28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3743814/24-24 (22) 22.05.84 (46) 07.04.86. Бюл. № 13 (71) Рязанский радиотехнический институт (72) А. М. Зимин и А. Н. Шестеркин (53) 681.327 (088.8) (56) Авторское свидетельство СССР № 636644, кл. G 09 G 3/28, 1978.

Авторское свидетельство СССР № 640288, кл. G 06 F 3/14, 1978.

„„SU„„1223283 А (54) УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ

ГРАФИЧЕСКОЙ ИНФОРМАЦИИ (57) Изобретение относится к устройствам отображения информации и предназначено для воспроизведения графиков на индикаторных (плазменных) панелях. Устройство содержит индикаторную панель, блоки ключей, блок памяти, формирователь, дешифратор, счетчики, преобразователи кодов, управляемый делитель частоты. Устройство обеспечивает высокое качество воспроизведения графической информации за счет устранения эффекта изменения вида изображения, возникающего при воспроизведении изображения в масштабе уменьшения. 1 ил.

1223283

50

Изобретение относится к устройствам отображения информации и предназначено для воспроизведения графических данных на индикаторных панелях.

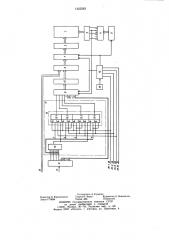

На чертеже представлена структурная схема предлагаемого устрйства.

Устройство содержит газоразрядную индикаторную панель 1, блок 2 анодных ключей, блок 3 катодных ключей, дешифратор 4, счетчик 5 развертки, блок 6 оперативной памяти, формирователь 7 импульсов, счетчик 8 адреса, задатчик 9 смещения по координате Х, генератор 10 тактовых импульсов, первый преобразовател ь 11 кодов, управл яем ый делитель 12 частоты, второй преобразователь 13 кодов, пороговый элемент 14, элементы И вЂ” ИЛИ

15i — 154, первый и второй информационные входы 16 и 17 устройства, первый, второй, третий и четвертый управляющие входы 18—

21 устройства.

Устройство работает следующим образом.

По срезу импульса, формируемого на первом выходе управляемого делителя 12, счетчик 5 развертки устанавливается в очередное L-e состояние. При этом íà L-м выходе дешифратора 4 столбцов вырабатывается активный уровень сигнала который поступает на блок 3 катодных ключей и обеспечивает подключение L-го столбца газоразрядной индикаторной панели 1. Синхронно с изменением состояния счетчика 5 развертки на выход формирователя 7 выдаются сигналы управления блоком 2 анодных ключей, сформированные во время подключения (1=1)-го столбца панели. Для формирования этих сигналов во время подключения каждого столбца панели при воспроизведении изображения в масштабе 15К на первом выходе управляемого делителя 12 генерируется последовательность из К импульсов,которая поступает на формирователь 7 и двоично-десятичный счетчик 8 адреса. Выходной код счетчика 8 адреса через преобразователь 13 двоично-десятичного кода в двоичный поступает в блок 6 оперативной памяти, обеспечивая последовательную выборку очередных К кодов ординат отображаемого графика, которые формирователем 7 преобразуются в сигналы управления блоком

2 анодных ключей. Временные характеристики работы устройства определяются генератором 10 тактовых импульсов.

Смещение изображения в устройстве осуществляется путем периодической записи в счетчик 8 адреса кода начального адреса опроса блока памяти. Запись кода производится перед началом формирования каждого кадра изображения. Поскольку формирование сигналов для воспроизведения изображения в первом столбце панели осуществляется в течение времени подключения ее последнего столбца, то принудительная

10 !

35 установка счетчика 8 адреса производится по срезу импульса с предпоследнего выхода дешифратора 4 столбцов. Начальный адрес опроса блока 6 памяти определяется задатчиком 9 смещения и преобразователем 11 кодов, который служит для получения кодов, кратных К, где 1:К вЂ” масштаб отображения информации по координате X.

При использовании рекомендуемых масштабов отображения 1:1,1:2, 1:5,1:10 целесообразно использование двоично-десятичных кодов, кратных 1, 2, 5, 10, в этом случае достаточно преобразовать только его младшую тетраду.

При масштабе отображения 1:1 формирование кода начального адреса опроса блока памяти осуществляется непосредственно задатчиком 9 смещения. При этом сигналы с входов его младшей тетрады проходят через преобразователь 13 кодов без изменений, что обеспечивается уровнем логической «1» сигнала Ml:1.

Условие того, что двоично-десятичный код кратен 2, — постоянное наличие логического «О» в его младшем разряде. При масштабе отображения 1:2 независимо от выходного кода задатчика 9 смещения на выходе элемента И вЂ” ИЛИ 15.1 постоянно формируется сигнал логического «О», так как сигнал

Ml:2 не подключен к входам элемента И—

ИЛИ 15.1. Остальные сигналы младшей тетрады задатчика проходят через преобразователь кодов без изменений. Двоично-десятичный код кратен 5, если значение кода его младшей тетрады равно либо О, либо 5. Для получения таких кодов сигнал Ml:5 поступает только на третий вход элемента И вЂ” ИЛИ

15.1 и пятый вход элемента И вЂ” ИЛИ 15.3.

При этом на входе элементов И вЂ” ИЛИ 15.2 и 15.4, независимо от входного кода задатчика смещения, формируются сигналы логического «О». Если значение кода младшей тетрады задатчика 9 смещения изменяется в пределах Π— 4, то на входе элемента 14 образуется сигнал логического «О». Это приводит к образованию сигналов логического

«О» и на входах элементов И вЂ” ИЛИ 15.1 и 15.3, т.е. значение кода младшей тетрады на выходе преобразователя кодов равно О.

Если значение кода младшей тетрады задатчика 9 смещения изменяется в пределах 5 — 9, то на выходе порогового элемента 14 образуется сигнал логической «1».

На выходах элементов И вЂ” ИЛИ 15.1 и 15.3 также сформируются сигналы логической «1» т.е. значение кода младшей тетрады на выходе преобразователя 13 кода равно 5.

Двоично-десятичный код кратен 10 при условии, что сигналы с выходов его младшей тетрады равны нулю. Для этого сигнал

М l:10 не поступает на входы элемента

И вЂ” ИЛИ 15, и на его выходе независимо от состояния задатчика смещения формируются сигналы логического «О».

1223283

1. Устройство для отображения графической информации, содержащее газоразрядную индикаторную панель, горизонтальные шины которой соединены с выходами блока анодных ключей, последовательно соединенные счетчик развертки, дешифратор и блок катодных ключей, выходы которых соединены с вертикальными шинами газоразрядной индикаторной панели, блок памяти, выход которого соединен с первым входом формирователя импульсов, второй и третий входы которого соединены со счетными входами счетчика адреса и счетчика развертки соответственно, а выход — с входом блока катодных ключей, управляющий вход счетчика адреса соединен с предпоследним вы40

Таким образом, при дискретности изменения значений выходного кода задатчика

9 смещения, равной единице младшего разряда, с помощью преобразователя 11 кодов обеспечивается формирование значения кодов смещения, кратных К, что исключает эффект искажения изображения.

При необходимости использования масштабов уменьшения с большими значениями

К (К=20, 50, ...) преобразователь 11 кодов должен быть построен для большего количест- 10 ва разрядов.

Использование двоично-десятичного задатчика смещения позволяет упростить схему преобразователя кодов, поскольку преобразованию подвергается меньшее число разрядов по сравнению с двоичным кодом, и преобразование производится по более простому алгоритму.

В предлагаемом устройстве при формировании адреса опроса блока 6 памяти используется двоично-десятичный счетчик, а двоичный код опроса блока памяти образуется с помощью преобразователя 13 двоично-десятичного кода в двоичный. Необходимость использования двоично-десятичного счетчика 8 адреса обусловлена применением двоично-десятичного задатчика 9 смещения 25 по координате Х. Использование разнотипных счетчика 8 адреса и задатчика 9 смещения приводит к скачкообразному смещению изображения при некоторых значениях выходного кода задатчика 9 смещения.

Таким образом, техническая эффективность изобретения заключается в повышении качества изображения при воспроизведении информации в масштабах уменьшения и смещении его по координате Х.

Формула изобретения ходом дешифратора, задатчик смещения по координате Х, выходы старших разрядов которого соединены с входами старших разрядов счетчика адреса, генератор тактовых импульсов, первый вход бока памяти и вход задатчика смещения по координате

Х являются первым и вторым информационными входами устройства соответственно, отличающееся тем, что, с целью повышения качества отображения за счет устранения искажений формы графиков при воспроизведении изображения в масштабе уменьшения, в устройство введены два преобразователя кодов и управляемый делитель частоты, первый вход которого соединен с вторым входом формирователя импульсов и счетным входом счетчика адреса, а второй выход — с третьим входом формирователя импульсов и счетным входом счетчика развертки, входы первого преобразователя кодов и управляемого делителя частоты являются первым, вторым и третьим управляющими и входам и устройства, четвертый вход управляемого делителя частоты является четвертым управляющим входом устрйства, входы группы первого преобразователя кодов соединены с выходами младших разрядов задатчика смещения по координате Х, а выходы — с входами младших разрядов счетчика адреса, выход которого соединен с входом второго преобразователя кодов, выход которого соединен с вторым входом бока памяти, пятый вход управляемого делителя частоты соединен с входом генератора тактовых импульсов.

2. Устройство по и. 1, отличающееся тем, что первый преобразователь кодов содержит пороговый элемент и четыре элемента И вЂ” ИЛИ, первые входы которых являются первым входом преобразователя, вторые входы элементов И вЂ” ИЛИ соединены с входами порогового элемента, третьи входы второго, третьего и четвертого элементов

И вЂ” ИЛИ являются вторым входом преобразователя, четвертые входы второго, третьего и четвертого элементов И вЂ И соединены с соответствующими входами порогового элемента, третий вход первого элемента

И вЂ” ИЛИ и пятый вход третьего элемента

И вЂ” ИЛИ являются третьим входом преобразователя, четвертый вход первого элемента И вЂ” ИЛИ и шестой вход третьего элемента И вЂ” ИЛИ соединены с входом порогового элемента, входы которого являются входами группы преобразователя кодов, выходы элементов И вЂ” ИЛИ являются выходами преобразователя кодов.

1223283

Редактор О. Юрковецкая

Заказ 1718(54

1 ВНИИП

Составитель А. Кулиева.

Техред И. Верес Корректор А. Зимокосов

Тираж 455 Подписное

И Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. - 4/5

Филиал ППП <Патент», г. Ужгород, ул. Проектная, 4