Многопороговый логический элемент

Иллюстрации

Показать всеРеферат

Изобретение относитсяк автоматике и вычиcлитeл нoй технике. Цель изобретения - расширение функциональных возможностей и повьппение надежности . Устройство содержит для каждого входа ключи на транзисторах 1 и 2 h -p-fi- и p-h-p-проводимости, резисторы 3 и весовой резистор 4. Резистивный делитель на резисторах 5. Многопороговый дискриминатор 9, состоящий из двзгхвходовых логических элементов И-НЕ 10, имеет порог срабатывания Т 1. Пороги срабатьшания последующих дискриминаторов возрастают на единицу. Количество однопороговых дискриминаторов в элементе равно количеству весовых резисторов -4.1 ил. (Л с f2 N9 tNP 00 са. ел ;о

СОЮЗ СОВЕТСНИХ социАлистичесних

РЕСПУБЛИН (19) (11) (S1) 4 Н 03 К 1 9/23

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ СССР по делдм изоБРетений и отнР1ытий

ОПИСАНИЕ ИЗОБРЕТЕНИЯ @,.;К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (9 (2i) 3747115/24-21 (22) 30,05.84 (46) 07,04.86. Бюп. 13 (71) Омский политехнический институт (72) И.А.Пальянов (53) 621.374(088 ° 8) (56) Авторское. свидетельство СССР

Ф 928653, кл. Н 03 К 19/20, 1982.

Авторское свидетельство СССР

В 790341, кл. Н 03 К 19/23, 1980. (54) МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ (57) Изобретение относится. к автоматике и вычислительной технике. Цель изобретения — расширение функциональных возможностей и повьппение надежности. Устройство содержит для каж- дого входа ключи на транзисторах 1 и 2 и -р-и- и р-н-р-проводимости, резисторы 3 и весовой резистор 4. Резистивный делитель на резисторах 5.

Многопороговый дискриминатор 9, состоящий иэ двухвходовых логических элементов И-НЕ 10, имеет порог срабатывания Т =1. Пороги срабатывания

1 последующих дискриминаторов возрастают на единицу. Количество однопороговых дискриминаторов в элементе равно количеству весовых резисторов

-4. 1 ил.

1223359

20

30 ры 2 открыты. Через цепь резисторов 1

" 5 и резистор 4, включенный в цейь

Изобретение относится к автоматике и вычислительной технике, в частности к пороговым логическим элементам.

Цель изобретения — расширение функциональных возможностей и повышение надежности.

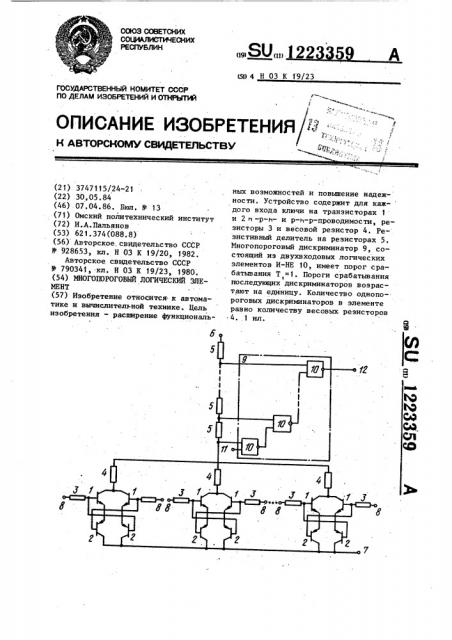

Введение изменения в структуре многопорогового логического элемента позволит уменьшить в два раза число резисторов, определяющих веса входов, На чертеже приведена принципиальная схема многопорогового логического элемента.

Многопороговый логический элемент содержит для каждого входа ключи на транзисторах 1 и 2 h --р-и и р-е-рпроводимости, резисторы 3 и для каждой пары входов весовой резистор 4.

Коллекторы «-р-и-транзисторов 1 каждой пары входов соединены и че. рез резисторы 4 подсоединены к выходу резистивного делителя на резисторах 5, вход которого соединен с положительным полюсом 6 источника питания. Эмиттеры -р-и-транзисторов f,êàëäoé пары входом соединены с эмиттерами р-ь-р транзисторов 2, коллекторы которых подключены к отрицательному полюсу ? источника питания. Базы второго и первого и-р-и-транзисторов 1 каждой пары соединены соответственно с базами первого и второго р-н-р-транзисторов

2 и через резисторы 4 подключены к входным клеммам 8 многопорогового логического элемента. Многопороговый дискриминатор 9 состоит из двухвходовых логических элементов И-НЕ

10, образующих однопороговые дискриминаторы. Вход 1 I порогового элемента И-НЕ подключен к положительному полюсу источника питания, а выход

12 является выходом многопорогового логического элемента (источник питания на чертеже не показан) . Однопо

1 роговый дискриминатор на элементе

И-НЕ 10, один из входов которого соединен с клеммой 11, имеет порог срабатывания Т,=1. Пороги срабатывания последующих дискриминаторов возрастают на единицу по сравнению с каждым предыдущим. Количество однопороговых дискриминаторов в элеме те должно быть равно количеству весо вых резисторов 4.

3S

55 н

Многопороговый логический элемент работает следующим образом.

Пусть количество входов элемента равно восьми. В этом случае он содержит четыре однопороговых дискриминатора с порогами срабатывания Т =1, Т =2, Т =З, Т„=4. Если входные сигналы элемента равны логическому нулю, то все и -р-о-транзисторы 1 являются закрытыми, потенциалы точек соединения резисторов 5 равны напряжению источника питания. На выходе однопорогового дискриминатора с наименьшим порогом срабатывания присутствует уровень логического нуля. На выходе

12 многопорогового логического элемента присутствует уровень логической единицы.

Пусть на один иэ входов многопорогового логического элемента поступает значение переменной, равной единице, а на остальные входы — значения переменных, равные нулю. В этом случае h -р-h-транзистор 1 и р- -ртранзистор 2, базы которых через резистор 3 подключены к клемме 8, на которую поступает единичное значение переменной, будут находиться соответственно в открытом и закрытом состояниях. Все остальные и --р-и-транзисторы 1 закрыты, а р-q-p-транэистопоследовательно включенных открытых и-р- и р-h р-транзисторов 1 и 2 протекает ток, уменьшающий потенциал в точках соединения резисторов 5.

Это приводит к срабатыванию дискриминатора с порогом Т„ =1. На входах всех остальных дискриминаторов, свя-, занных с резистивным делителем, присутствует высокий уровень напряжения.

На выходе дискриминатора с порогом

Т, устанавливается единичное значение логической функции, а на выходе

12 многопорогового логического элемента четности — нулевое.

Если на клеммы 8, принадлежащие различным парам входов многопорогового логического элемента, поступают единичные значения логических переменных, то для каждой пары входов, имекицей единичное и нулевое значения входных переменных, существует цепь из последовательно включенных открытых и-р-е и р-h р-транзисторов 1 и 2.

В этом случае через цепь резисторов

5 и резисторы 4, включенные в цепи

1223359

ВНИИПИ Заказ 1723/58 Тираж 816 Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 коллекторов открытых л-р-h-транзисторов 1, протекает ток, определяемый числом единиц, поступивших на входы многопорогового логического элемента.

Напряжения на выходах резистивного делителя из резисторов 5 уменьшаются, что приводит к срабатыванию дискриминаторов на элементах И-НЕ 10. Количество сработавших дискриминаторов на элементах И-HE 10 в данном случае 1О равно числу единичных значений переменных, поступивших на входы многопорогового логического элемента четности. Если на входы многопорогового логического элемента четности посту- 15 пает нечетное число переменных, то срабатывает нечетное число дискриминаторов и на выходе 12 устанавливается низкий уровень напряжения, соответствующий логическому нулю. При 20 четном числе единичных входных переменных срабатывает четное число дискриминаторов и на выходе )2 устанавливается высокий уровень напряжения, соответствующий еди- 25 ничному значению логической функции е

В случае, когда единичные значения переменных поступают в клеммы

8, принадлежащие одной паре входов многопорогового логического элемента, оба р-л-р-транзистора 2 данной пары входов многопорогового логического элемента закрыты, ток через

35 резистор 4 отсутствует, а выходная функция элемента определяется комбинациями переменных на других входах. Например, на входы многопорогового логического элемента четности поступает три переменных, равных единице, причем две единицы поступают в клеммы 8, относящиеся к одной паре входов элемента. Следовательно, ток через резистор 4, относящийся к этой паре входов отсутствует и выходная функция многопорогового логического элемента четности равна нулю, так как ток через резисторы 5 определяется только одной па- 50 рой последовательно включенных открытых -р-w и р — л-р-транзисторов

1и2.

Формула изобретения

Многопороговый логический элемент, содержащий резистивный делитель, вход которого подключен к положительному полюсу источника питания, выходы соединены с одними входами логических элементов И-НЕ, образующих многопороговый дискриминатор, второй вход каждого из которых

Ф кроме имеющего наименьший порог срабатывания, соединен с выходом последующего логического элемента И-HE

Э л-р-л-транзисторы и весовые резисторы, первые выводы которых объединены, второй вход логического элемента

И-НЕ, имеющего наименьший порог срабатывания, соединен с положительным полюсом источника питания, выход логического элемента H-НЕ, имеющего наибольший порог срабатывания, является выходом устройства, о т л ич а ю шийся тем, что, с целью расширения функциональных возможностей и повышения надежности, он дополнительно содержит для каждой пары входов два резистора и два р-h-р-транзистора, коллекторы которых соединены с отрицательным полюсом источника питания, эмиттер первого р-л-р-транзистора соединен с эмиттером w-р-л-транзистора, эмнттер второго р-л-р-транзистора соединен с эмнттером второго -р-h-òðàí3Hñ-. тора, базы второго и первого р-л-ртранзисторов соединены соответственно с базами первого и второго ь-р-ьтранзисторов и через первый и второй резисторы подключены к соответствующим входным клеммам многопорогового логического элемента, коллекторы первого и второго л -р-и-транзисторов каждой пары входов объединены и подключены к второму выводу весового соответствующего резистора, первые выводы которых подключены к первому входулогического элемента И-НЕ, имеющего наименьшийпорог срабатывания.