Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использова АйгГ но при построении БИС обработки и хранения информации. Изобретение позволяет повысить точность аналогоцифрового преобразователя за счет введения четырех токовых повторителей на р-и-р-транзисторах 7 и 8 и h-p-h-транзисторах 9 и 10 в устройство , содержащее управляемый источник тока, выполненный на р-и-р-транзисторе 1, компараторы на триггерах с непосредственными связями , выполненных на h-p-h-транзисторах соответственно старшего 2 и младшего 3 разрядов, на п-р-к-транзисторах 4 и 5, входной элемент, выполненный на р-ъ-р-транзисторе 6. 2 ил. (Л IND to оо 00 Од N9

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) {1!) 362

15ц H 03 Y. 1/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО делАм изОБРетений и ОтнРытий

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3679825/24-24 (22) 27.12.83 (46) 07.04.86. Бюл. ¹ 13 (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) Л.К.Самойлов, IO.È;Ðîãoçîâ, А.В.Глоба и О.Э.Цапко (53) 681.325(088.8) (56) Авторское свидетельство СССР № 600729, кл. Н 03 К 13/20, 1977.

Авторское свидетельство СССР

¹ 809558, кл. Н 03 К 13/20, 1979. (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к импульсной технике и может быть использовано при построении БИС обработки и хранения информации. Изобретение по- . зволяет повысить точность аналогоцифрового преобразователя за счет введения четырех токовых повторителей на р-н-р-транзисторах 7 и 8 и

h-р-н-транзисторах 9 и 10 в устройство, содержащее управляемый источник тока, выполненный на р-п-р-транзисторе 1, компараторы на триггерах с непосредственными связями, выполненных на и -р-л-транзисторах соответственно старшего 2.и младшего 3 разрядов, на -р-а-транзисторах 4 и 5, входной элемент, выполненный на р-h-p-транзисторе 6. 2 ил.

1223362

Изобретение относится к импульсной технике и может быть использовано при построении БИС обработки и хранения информации.

Цель изобретения — повышение точ- 5 ности аналого-цифрового преобразователя.

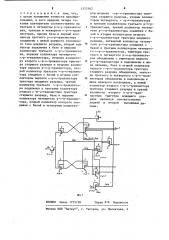

На фиг. 1 представлена принципиальная электрическая схема аналогоцифрового преобразователя; на фиг.2 — 10 вариант функционально-топологической ее реализации.

Устройство содержит управляемый источник тока, выполненный на,первом р-а-р-транзисторе 1, компараторы — 15 на триггерах с непосредственными связями, выполненные на первых -р-итранзисторах соответственно старшего

2 и младшего 3 разрядов, вторых -р-и-транзисторах 4 и 5 триггеров компараторов, входной элемент, выполненный на втором р-ti-р-транзисторе 6, токовые повторители на третьем 7 и четвертом 8 р-н-р-транзисторах, 1 третьем 9 и четвертом 10 > -р-й-тран-.

25 зисторах.

Эмиттер транзистора 6 соединен с входной шиной, эмиттеры транзисто- . ров 1,7 и 8 объединены и соединены с шиной питания, вторые коллекторы

30 транзисторов 4 и 5 являются выходами устройства, эмиттеры транзисторов

2,3,4,5,9 и 10 объединены с базами транзисторов 1 и 6 и с шиной нулевого потенциала, а база и первый кол- 35 лектор транзистора 7 соединены с шиной внешнего эталонного тока младшего разряда.

Устройство работает следующим образом. 40

Предположим, что „" 4/2, в этом случае транзистор 2 открыт (насыщен), а транзистор 4 соответственно закрывается. Запирание транзистора 4 приводит к тому, что входной 45 ток транзистора 9 равен 1,/2 (т.е. транзистором 4 не отбирается входной ток транзистора 9). В этом случае из входного тока транзистора 3 вычитается коллекторный ток транзистора 9, 50 равный 1„/2, и, кроме того, коллекторный ток (!, 4) транзистора 9 вызывает появление такого же значения коллекторных токов транзистора 8, выходной вытекающий ток которого преобразуется во втекающий с помо-. щью транзистора 10 и сравнивается со значением эталонного тока младшего разряда АЦП (монтажная связь коллектора транзистора 7 с коллектором транзистора 10).

Результатом сравнения является алгебраическая разность между эталонным током (1„ - коллекторный ток транзистора 7) и током обратной связи (1„ — коллекторный ток транзистора 10)

dI= !„-1, Если выполняется неравенство «!„ то к значению входного тока I./2 добавляется ток 5 который вызывает увеличение выходных токов транзисторов 8 и 10,,а соответственно и уменьшение значения разности.d I . Если выполняется неравенство а !, то

ЗТ оЯ из входного тока транзистора 9 вычитается значение d !, что приводит к уменьшению выходных токов транзисторов 8 и 10, а соответственно и уменьшению значения разности между сигналами Е, и !„

Еслй „(! /2, то транзистор 4 открывается и полностью отбирает входной ток транзистора 9. В этом случае функцию формирования эталонного тока для младшего разряда AIUI выполняет транзистор 4, который работает в линейном режиме. Соответственно, транзистор 4 участвует в режиме стабилизации. В этом режиме транзистор 10 отбирает в свой коллектор ток, равный J /2.

Аналогичным образом можно проследить за работой устройства при других комбинациях входных сигналов.

Формула изобретения

Аналого-цифровой преобразователь, содержащий два компаратора на триггерах с непосредственными связями, каждый иэ которых выполнен на первом и втором ь -р-ь-транзисторах, управляемый источник тока, выполненный на первом р-п-р-транзисторе, входной элемент на втором р-а-р-тра 1Листоре, эмиттер которого подключен к входной шине, коллекторы — к базам первых л-р-и-транзисторов триггеров, а база объединена с эмиттерами и --р-итранзисторов триггеров и базой первого р- -р-транзистора и соединена с шиной нулевого потенциала, первый коллектор первого р-и-р-транзистора соединен с базой второго w-p-h-транзистора триггера старшего разряда, 1223362 ираж 816 Подписное

ВНИИПИ Заказ 1723/58 филиал ППП "Патент", r, Ужгород, ул. Проектная, 4 отличающийся тем, что, с целью повышения точности преобразования, в него введены четыре токовых повторителя соответственно на третьем и чЕтвертом р-h-р-транзисторах, третьем и четвертом -р- -транзисторах, причем база и первый коллектор третьего р-h-р-транзистора соединены с шиной внешнего эталонного тока младшего разряда, второй коллектор подключен к базе и первому коллектору. третьего h -р-h-транзистора, первому коллектору четвертого

e-p-h-транзистора, второму коллектору второго -р-h-транзистора триггера старшего разряда и второму коллектору первого р-h-р-транзистора, второй коллектор третьего h-p-h-транзистора соединен с базой и вторым коллектором первого h-р-а-транзистора триггера младшего разряда, третий коллектор третьего h --р-h-транзистора подключен к третьему коллектору второго >-р-h-транзистора триггера старшего разряда, базе и первому коллектору четвертого р-ь- р-транзис тора, второй коллектор которого соединен с базой и,четвертым коллекто" ром второго h" p- -транзистора триггера старшего разряда, вторым коллектором четвертого h -р-w-транзистора и третьим коллектором третьего р-h-p5 транзистора, третий коллектор четвертого р- -р-транзистора соединен с базой и вторым коллектором второго -р-h-транзистора триггера младшего разряда, четвертый коллектор четвертого р- -р-транзистора соединен с базой и третьим коллектором четвертого a-p-h-транзистора, эмиттеры третьего и четвертого р-е-р-транзисторов объединены с эмиттером первого р-h-р-транзистора и подключены к шине питания, база и второй коллектор первого h -р-h-транзистора триггера старшего разряда объединены, эмиттеры третьего и четвертого h-p-h-тран20 зисторов объединены и подключены к шине нулевого потенциала, а пятый коллектор второго -р- -транзистора триггера старшего разряда и третий коллектор второго h -р-Ь-транзистора триггера младшего разряда являются соответственно первой и второй выходными шинами.