Устройство для контроля проводных каналов связи

Иллюстрации

Показать всеРеферат

Изобретение м.б. использовано для контроля и испытаний переключаемых каналов связи. Цель изобретения - увеличение точности контроля проводных каналов связи и повышение надежности устройства. Устрой (Л с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (И) (51) 4 H 04 В 3/46

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬГП4Й!

ОПИСАНИЕ ИЗОБРЕТЕНИЯ/ ::: „,, -!

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ (61 ) 1135012 (21 ) 3755427/24-09 (22) 13.06.84 (46) 07 ° 04.86. Бюл. № 13 (72) В.А.Мясоедов и И.М.Букин (53) 621.396(088.8) (56) Авторское свидетельство СССР

¹ 1135012, кл. Н 04 В 3/46, 1981. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПРОВОДНЫХ КАНАЛОВ СВЯЗИ (57) Изобретение м.б. использовано для контроля и испытаний переключаемых каналов связи. Цель изобретения — увеличение точности контроля проводных каналов связи и повышение надежности устройства. Устрой1 ство содержит 1-й задающий приемопередатчик (ПП) 1.1 команд, 2-й задающий ПП 1.2 команд, исполнительный

ПП 2 команд, коммутаторы 3, блок 4 выбора направления передачи, 1-й анализатор временных интервалов (АВИ) 5, 2-й АВИ 6. 2-й АВИ 6 содержит 1-й блок,55 сравнения, 2-й блок

56 сравнения и элемент ИЛИ 57. Обмен информацией между задающим и -исполнительным ПП произзодится по каналу связи, в заданную точку которого включен переключатель без дополнительных контрольных линий. В устройстве могут быть реализованы следующие направления: a) от задающего ПП

223377

1.1/1.2 к исполнительному ПП 2 и на-оборот; б) от задающего ПП 1.1/l. 2 к задающему и исполнительному ПП 1.2/

/1.1 и 2; в) от исполнительного ПП 2 к задающим ПП 1.1 и 1.2. Выбор направления производит задающий ПП 1.1/

/l.2. Контроль производится одновременно с обменом информацией..Поскольку обмен производится четными (Hp четными) кодами, предварительного контроля не требуется. Обмен может быть произведен как в параллельном, Г так и в последовательном коде. Изобретение дополнительное к авт. св.

Ф !135012, 2 з.п. ф-лы, 1 ил.

Изобретение относится к электросвязи, может быть применено для контроля и испытаний переключаемых ка— налов связи и является усовершенствованием устройства по основному авт. св. 1! - 1135012.

Цель изобретения — увеличение глубины контроля и повышение надежности устройства.

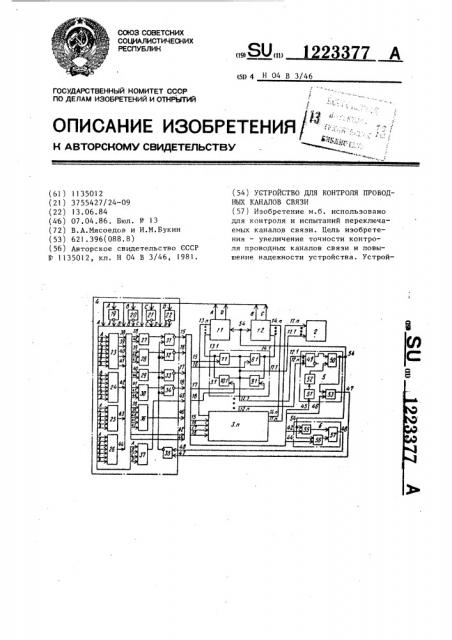

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство для контроля проводных каналов связи содержит первый задающий приемопередатчик 1.1 команд, второй задающий приемопередатчик

1.2 команд, исполнительный приемопередатчик 2 команд, коммутаторы 3, блок 4 выбора направления передачи, первый анализатор 5 временных интервалов, второй анализатор 6 временных интервалов.

0

t5

Каждый коммутатор 3 содержит логические элементы 7 — 10, шину первого информационного выхода 11, шину

25 второго информационного выхода 12, шину первого информационного входа

13, шину второго информационного входа 14, шины управляющих входов 15-18.

Блок 4 выбора направлений передачи содержит первый !9, второй 20, третий 21 и четвертый 2Z элементы

НЕ, первый 23, второй 24, третий 25 и четвертый 26 дешифраторы, первый

27, второй 28 третий 29 и четвертый 30 элементы ИЛИ, первый 3! второй 32, третий 33 и четвертый 34 элементы И-НЕ, элемент ИЛИ-НЕ 35, пятый элемент ИЛИ 36, элемент И 37, шины выходов 38-46 и шины управляющих входов 47 и 48.

Первый анализатор 5 временных интервалов содержит сумматор 49 по модулю два, блок 50 памяти, счетчик 51 импульсов, формирователь 52, блок 53 сравнения и шину управляющего выхода 54.

Второй анализатор 6 временных интервалов содержит первый 55, второй

56 блоки сравнения и элемент ИЛИ 57.

Устройство для контроля проводных каналов связи работает следующим образом, Обмен информацией между задающим и исполнительным приемопередатчиками производится по каналу связи, в заданную точку которого включен переключатель, без дополнительных контрольных линий.

В устройстве для контроля проводных каналов связи могут быть реализованы следующие направления . от задающего приемопередатчика 1.1 (l.2) к исполнительному приемоепе12 3377

С17

Т

3 где д )

i1)

cong/ момент приема исполнительным приемопередатчиком 2сигнала; момент прохождения переключателя (заданной точки г канала, в который включен переключатель, посланным сигналом); время обработки сигнала исполнительным приемопередатчиком 2;

77(лат шку 2, и наоборот, от задав— к11иего приемопередатчика 1. 1 (1. 2) к задавщему и исполнительному приемопередатчикам 1.2 (1.1) и 2; от исполнительного приемопередатчика 2 к задающим приемопередатчикам 1.1 и

1. 2.

Инициатива в выборе направления принадлежит задающему приемопередатчику 1.1 (1,2), который реализует выбор направления обмена. Кроме того, задающий приемопередатчик 1.1 (1,2) может передать инициативу другому задающему приемопередатчику

1.2 (1.1). Контроль производится одновременно с обменом информацией.

Поскольку обмен производится четнь7ми (нечетными) кодами, предварительного контроля не требуется, Обмен может производиться как в параллельном, так и в последовательном коде. Пример реализации представлен для параллельного п-разрядного кода. В случае применения последовательного кода для обмена информацией нужна только одна переключае— мая линия канала и, соответственно, один коммутатор.

Сущность контроля состоит в том, что в переключателе, включенном в заданную точку i канала связи, запоминают моменты прохождения посланного от задающего приемопередатчика

1.1 (1.2) сигнала и сигнала (подтвер" ждения), посланного от исполнительного приемопередатчика 2 или от задающего приемопередатчика 1.2 (1.1).

По указанным моментам в переключателе формируют временной интервал, который сравнивают с заданным интервалом. Заданный интервал выбирается, из соответствующего соотношения.

Для контооля участка переключатель — канал связи — исполнительный приемопередатчик 2 точка проводного к:111;1и;1 связи, в которув вклвч 11 коммутатор.

Для контроля участка переклвча5 тель — канал связи — задающий приемопередатчик 1. 2 (к7 <О (27

<1 СОП 1?

127

10 где t„ момент приема сигнала задающим приемопередатчиком 1.2.

Ю вЂ” момент прохождения комму1 таторов сигналом от задающего приемопередатчика 1.1; (z7

< — время обработки сигнала з адающим приемопередатчиком

1 . 2, Для контроля участка и ереклвч атель — канал связи — задающий приемо20,)передатчик 1.1

<М (S1 (М т =с„— + (М где t — момент приема

25 щим приемопере устройство для контроля проводных каналов связи работает в трех режимах. Работа блока 4 выбора направления происходит в соответствии с приведенной функциональной таблицей. сигнала задаюдатчиком

1.1;

М

t — момент прохождения коммута1 торов сигналом от задающего приемопередатчика 1.2;

1 „ - время обработки сигнала задающим приемопередатчиком

1.1.

Если сформированный в переключателе временной интервал меньше заданного, канал исправен, если больше— канал неисправен и автоматически отключается. Повторное включение канала осуществляется задающим приемопередатчиком 1.1 (1.2) путем снятия, а затем повторной подачи сигнала выбора направления. В случае отказа задающий приемопередатчик 1.1 (1.2) (процессор) можетпо желанию или повторить контроль, вторично установив то же направление, или установить

45 новое направление, или по программе начать диагностику переключаемых каналов, выдавая, например, последовательно в каждую линию канала, начиная с первой, контрольную информацию (при отсутствии ее в других разрядах) и локализуя таким образом отказавшую переключаемую линию канала.

1?23377

A В С 1) Г

44 ь

10

1 О О О О

2 () О О 1

3 О О 1 О

4 О, l О О

5 О 1 1 О

6 О 1 1 1

7 1 О О О

8 1 О О 1 О

9 1 О 1

i0 1 1 О 1

11 1 1 1 О 0

В функциональной таблице приведе30 ны порядковые номера используемых в блоке 4 наборов (комбинаций) логических переменных (логические "О" или ."1") A,В,С и D, характеризующих состояние управляющих выходов задающих приемопередатчиков 1.1 и 1.2.

Каждая логическая переменная принимает одно из двух значений А — (аa), В = (bЬ), С = (сс), D =(а,а .

При этом в блоке 4 приняты следующие соотношения значений логических переменных и их физических эквивалентов. a = b = с = d логическая

"1" низкий уровень напряжения (О B); a = b = ñ c= d. 4 †логический 45

"О" 4 Высокий уровень напряжения (=5 В).

142 44 и F4 — функции седьMoro

1 восьмого и шестого выходов блока 4.

Под индексами функций записан тот за- 0 (z) (y) данный временной интервал (Т>, Т>, 8)

Т соответственно), на формйрование которого функция дает разрешение (разрешение выдается высоким уровнем напряжения, что соответствует логиче- 55 ск™ 0 функций F, 4 и F

F,5, F,z, Fy и Гш — функции выходов

15-18 блока 4 соответстненно под инО О О О

О О О О 1

О О О 1 О

0 О 1 О О

О О 1 l

О О 1 О 1

О 1 О О О

1 1 О О

О О 1 1

О 0 l О 1

1 1 О О дексами функций указаны позиции логических элементов 7-10 коммутаторов

3 соответственно).

Режим 1. B исходном состоянии задающие приемопередатчики 1.1 и 1.2 не выбрали направления. На линии выбора сигнал подается с высоким уров= нем (значения логических переменных

А = а В = b, С = с, D = d) на выходах 38-44 дешифраторов 23-26 блока 4 выбора направления передачи сигнал низкого уровня.

Покажем для примера как формируется этот сигнал на выходе 42, для чего, подставив в выражение 1" ука42 занные значения, логических переменных и олучим

F4 — АВСБ АВСЭ --+ аЬсЙVabcd †. низкий уровень.

Независимо от сигналов на первом

47 и втором 48 управляющих входах блока 4 выбора направления передачи на управляющие входы 15-18 коммута-. ° торов 3 через элементы И-HE 31-34 подается сигнал высокого уровня ° Все линии разомкнуты, пока задающий приемопередатчик, например 1.1, не выберет направление, для чего, на- .

1 .. 23377

15

25

45

7 ( пример, по линии на сигнальный вход

А передает сигнал низкого уровня в блок 4 выбора направления передачи (значения логических переменных А =

Ф а, В =Ь, С = с, D=d, комбинация 7 таблицы). В этом случае с выхода 38 первого дешифратора 23 сигнал с высоким уровнем поступает через элемент ИЛИ 27 на первый вход элемента И-НЕ 31, на втором входе которого присутствует сигнал с высоким уровнем с выхода элемента ИЛИНЕ 35. Тогда по совпадению сигналов высокого уровня на входах элемента

И-НЕ 31 на его выходе и далее на первом выходе блока 4 выбора направления передачи появляется сигнал низкого уровня, который поступает на I управляющий вход 15 коммутаторов

3.1-3.п. В последних открываются логи ческие элементы 7 и линии (информационный вход 13) переходят в замкнутое состояние. При этом открывается направление от задающего приемопередатчика 1.1 к исполнительному приемопередатчику 2. Одновременно на выходы 45 и 46 блока 4 выбора направления передачи с выходов элемента

И 37 и элемента ИЛИ 36 поступают соответственно сигнал низкого и сигнал высокого уровня, которые проходят на первый и второй управляющие входы ана лизатора 5 временных интервалов. Сигнал низкого уровня с первого управляющего входа поступает на вход счетчика 51, с выхода которого он поступает на формирователь 52. С выхода последнего сигнал поступает на вход сброса блока 50 памяти, устанавливая его в нулевое (исходное) состояние.

Сигнал высокого уровня с второго управляющего входа поступает на второй . (разрешающий) вход блока 53 сравнения, подготавливая его к приему сигнала с блока 50 памяти. пает IIa сигнальные входы анализатора 5 временных интервалов и далее на входы сумматора 49 по mod 2. С одн го из выходов последнего (выход выбирается в зависимости от того, четное или нечетное число бит содержит сигнал задающего приемопередатчика) снимается сигнал, поступающий на вход синхронизации блока 50 памяти и устанавливающий его в единичное состояние. Сигнал с выхода блока 50 памяти поступает на вход блока 53 сравнения и, так как на его втором входе имеется разрешающий сигнал, (со,второго управляющего входа 46) включает его в работу. Передав сигнал исполнительному приемопередатчику 2, задающий приемопередатчик 1.1 изменяет направление передачи в линии, для чего сниь ает сигнал низкого уровня с линии (сигнального входа А) и выставляет его на линии .(сигнальный вход D,.çíà÷åíèÿ логических переменных А = а, B = b, С = с, 11 = й; комбинация 2 таблицы).

В соответствии с этим на первом выходе блока 4 выбора направления передачи, соединенном с управляющим входом 15, снимается сигнал выбора направления, а на управляющем входе 18 появляется. Тем самым в коммутаторе

3 логический элемент 7 закрывается, а логический элемент 10 открывается. Одновременно с появлением сигнала выбора указанного направления на пятом выходе 45 блока 4 выбора направления передачи появляется сигнал с выхода элемента И 37. Этот сигнал поступает на первый управляюший вход

45 анализатора 5 временных интервалов и далее на вход счетчика 51.

Поскольку на выходе счетчика 51 сигнал появляется на каждый нечетный сигнал на входе, то в этом случае на входе формирователя 52 сигнала нет и состояние выхода блока 50

55

Далее задающий приемопередатчик

l.1, выбрав направление, посылает сигнал к исполнительному приемопередатчику 2 по замкнутой линии по цепи: задающий приемопередатчик 1.1, канал связи, входы 13 коммутаторов

3.1-3.п логические элементы 7, первые информационные выходы 11.1ll.n коммутаторов 3.1-3.п, канал связи, исполнительный приемопередатчик 2. Одновременно со вторых информационных выходов 12.1-12.п коммутаторов 3.1-3.п этот сигнал поступамяти не изменяется.

Далее исполнительный приемопередатчик 2 посылает сигнал (подтверждения) к задающему приемопередатчику !.1 по цепи: исполнительный приемопередатчик 2, канал связи, первые информационные выходы ll.l-ll.n коммутаторов 3.1-3.п, логические элементы 10, входы 13.1-13.п коммутаторов 3.1-3.п канал связи, задающий приемопередатчик 1.1. Одновременно со вторых информационных выходов

1?233

12.! — 12.п коммутаторов 3.1-3.п этот сигнал поступает на сигнальные входы анализатора 5 временных интервалов и далее на входы сумматора 49 по шой 2, с выхода которого снимается сигнал на вход синхронизации блока

50 памяти, устанавливающий ето в нулевое состояние.

При этом сигнал с выхода блока

50 памяти подается на вход блока 53 10 сравнения с нулевым потенциалом и выключает его из работы. Если же переключаемый канал оказывается неисправным, что соответствует отсутствию сигнала на входе синхро- 15 низации блока 50 памяти, то состояние последнего не изменяется, блок

53 сравнения работает и по истече(г) нии заданного времени Т формиру) ет сигнал высокого уровня, поступающий с второго выхода 47 анализатора

5 временных интервалов на первый управляющий вход блока 4 выбора направления передачи. Этот сигнал через

f элемент ИЛИ-НЕ 35 поступает с низким уровнем на вторые входы элементов И-НЕ 31-34, вследствие чего на первом, втором, третьем и четвертом выходах 15 — 18 блока 4 выбора направления передачи появляется сигнал высокого уровня, который поступает на управляющие входы коммутаторов 3,1-3.п и отключает линии, в том числе и выбранное направление.

Однако, пока не снят сигнал выбора, 35 установленный ранее задающим приемопередатчиком 1.1 на линии (сигнальный вход D), состояние сигнала на выходе 45 блока 4 выбора направления передачи, состояние счетчика

51, формирователя 52 и блока 50 па- . мяти не изменяют ° Для выбора нового направления задающий приемопередат— чик 1,1 долх ен сначала снять сигнал выбора.При этом сигнал на пятом выходе 45 возрастает с низкого до высо45 кого уровня, что не изменяет состояние счетчика 51 (счетчик управляется перепадом из высокого уровня в низкий), следовательно, формирователя

52 и блока 50 памяти. Сигнал на шестом выходе 46 изменяется с высокого уровня на низкий и отключает блок

53 сравнения, который устанавливается в исходное состояние. В результате этого на втором выходе 47 анализатора 5 временных интервалов появляется сигнал низкого уровня, который поступает на первый управляю77 10 щий вход блока 4 выбора направления передачи и далее через элемент ИЛИHF. 35 (единицей) на вторые входы эл ментов И-HF 31-34 и снимает блокировку направлений.

Затем задающий приемопередатчик

1.1 реализует повторное включение на правления. Для этого вновь выставляется сигнал выбора. Аналогично описанному появляется сигнал на пятом выходе 45 блока 4 выбора направления передачи (перепад с высокого уровня в низкий), по которому изменяется состояние счетчика 51 (на его вы ходе происходит изменение сигнала с высокого уровня до низкого), а формирователь 52 вырабатывает импульс, поступающий на вход сброса блока 50 памяти и устанавливающий его в исходное состояние. Одновременно с выхода элемента ИЛИ 36 на второй управляющий вход 46 анализатора 5 временных интервалов и,далее на второй вход блока 53 сравнения поступает (высоким уровнем) сигнал разрешения. Коммутатор 3.1-3.п при этом реализует выбранное направление обмена по каналу. Если при выдаче.сигнала выбора исходное состояние не устанавливается (задающий приемопередатчик 1.1 получает информацию об исходном состоянии по уровню в проводном канале связи и (или) по сигналу с первого выхода 54 анализатора

5 временных интервалов, поступающему через линию связи на управляющий вход), достаточно выставить сигнал выбора вторично. Отсутствие исходного состояния и в этом случае означает отказ данного направления и необходимость выбора другого направления или диагностики.

Работа задающего приемопередатчика 1.2 с исполнительным приемопередатчиком 2 происходит аналогично, только по информационным входам

14.1-14.п и через логические элементы 9 и 8, управляемые по входам

17 и 16 коммутаторов 3.1-3.п.

Режим 2. Этот режим работы устройства осуществляется для проверки канала связи на участке переключатель — задающий приемопередатчик

1.2 и (или) при неисправности однойили сразу двух линий выбора А и Р (не снимается сигнал низкого уровня) задающего приемопередатчика 1.1, а также для прослушивания приемопе12 " 3! 7

40 редлтчиком 1.1 обмепл между задающим ).2 и исполнительным 2 приемопередатчиками.

Инициатива обмена информацией при— надлежит задающему приемопередатчику )..1.

Исходное состояние: нл линиях выбора А, D и С,  — сигнал высокого уровня (значения логических переменных А =- а, B = b, (. = c, D = d).

Задающий приемопередатчик 1.1 выставляет на линиях выбора А и D сигнал низкого уровня (значения логических переменных А = а, В = Ь, С = с, D = d; комбинация 8 таблицы).На вы- 15 ходе 42 второго дешифратора блока 4 выбора направления передачи появляется сигнал высокого уровня, который через первый и второй элементы

ИЛИ 27 и 28 поступает на первые вхо- 70 ды элементов И-HF. 31 и 32, так как на вторых входах последних имеется разрешение (сигнал высокого уровня с выхода элемента ИЛИ-НЕ 35), то инвертированный сигнал (сигнал низкого уров- 25 ня) проходит на выходы )5 и 16 блока

4 выбора направления передачи и далее на соответствующие управляющие входы коммутаторов 3 и логические элементы 7 и 8. Открывается направление задающий приемопередатчик 1.1 задающий приемопередатчик ).2 и исполнительный приемопередатчик 2. Одновременно с седьмого выхода 42 блока 4 выбора направления передачи

35 сигнал высокого уровня поступает на первый вход анализатора 6 временных интервалов и далее на второй (разрешающий) вход блока 55 срагнения.

Также одновременно с пятого выхода

45 сигнал низкого уровня поступает на первый управляющий вход анализатора 5 временных интервалов и далее через счетчик 51 и формирователь 52 на вход сброса блока 50 памяти (ус45 танавливает исходное состояние блока 50 памяти). При этом на втором управляющем входе 46 анализатора 5 временных интервалов сигнал низкого уровня, запрещающий работу блока 53 сравнения. !

Задающий приемопередатчик 1.1, открыв логические элементы 7 и 8 коммутаторов 3, передает информацию в задающий приемопередатчик 1 ° 2 по цепи: задающий приемопередатчик 1.1, информационные выходы 13.1-)3.п, канал связи, первые информационные входь! коммутл торов 3 ° л(гические эле менты 7 и 8, вторые информ !цио!!7Эь! входы коммут; торов 3, клнлл связи, гп!формлционные выход!! )4.)†)4.п, задающий приемопередатчик ).2. Одновременно этот сигнал поступлет нл первый и второй информационные выходы

11.1 †.I7 и !2.1 — 12.п коммутаторов

3, с первого ииформлцнонного выхода которых он передается к исполнительному приемопередатчику 2, а с второго — нл сигнальные входы лнллизлтора 5 временных интервалов и далее на входы сумматора 49 по шой 2. выхода последнего сигнал поступает на вход синхронизации блока 50 памяти и устанавливает его в единичное состояние. С выхода блока 50 памяти сигнал высокого уровня проходит через первый выход 54 анализатора 5 временных интервалов на управляющий вход анализатора 6 временных интервалов и в линию связи на упрлвляюшие входы задающих приемопередатчиков I.l u 1.2. С управляющего входа 54 анализатора 6 временных интервалов единичный сигнал поступает на объединенный вход блоков .55 и 56 сравнения . Но так как на первом входе 42 блока 55 сравнения присутствует сигнал высокого, а на первом входе 44 блока 56 сравнения — сигнал низкого уровня, то начинает работать блок 55 сравнения, осуществляющий контроль временного интервала на участке переключатель — задающий приемопередатчик !.2. Задающий приемопередатчик

1.2, получив информацию от задающего приемопередатчика 1.1, должен за время t обработать ее и выс(г7 сОпб6 тавить сигнал низкого уровня на линию С. Если это условие соблюдено, то на входе 42 появляется сигнал низкого уровня, а если не соблюдено, то время наличия сигнала высокого уровня на входе 42 (при наличии сигнала высокого уровня на входе 54) (27 (17 больше заданного времени Т = t и

+ t „,что вызывает появление сигнала высокого уровня на выходе блока 55, отключение всех каналов передачи и свидетельствует о неисправности участка переключатель — задающий приемопередатчик

1.2.

При выставлении сигнала низкого уровня на линии С логические переl4

13 1223377 менные имеют значения: А = а, В = о, С = с, D = и (комбинация 9 таблицы).

Кодовый сигнал поступает на четвертый дешифратор 26, на его выходе

44 появляется сигнал высокого уровня, который проходит через третий и четвертый элементы ИЛИ 29 и 30 на первые входы элементов И-НЕ 33 и 34, на вторых входах которых имеется сигнал высокого уровня с выхода элемента ИЛИ-НЕ 35. На третий и четвертый выходы 17 и 18 блока 4 выбора направления передачи и далее на соответствующие управляющие входы коммутаторов 3 поступает сигнал низкого уровня, который открывает направле— ние задающий приемопередатчик 1.2— задающий приемопередатчик 1.1 и исполнительный приемопередатчик 2.

Задающий приемопередатчик 1.2, открыв направление, передает сигнал подтверждения в задающий приемопередатчик по цепи: задающий приемопередатчик 1.2,информационные выходы 14.1l4.п, канал связи, вторые информационные входы коммутаторов 3, логические элементы 9 и 10, первые информационные входы коммутаторов 3, канал связи, информационные выходы

13.1-13.п, задающий приемопередатчик 1.1. Аналогично описанному этот же сигнал поступает через первый и второй информационные выходы 11.111.п и 12.1-12.п коммутаторов 3 на исполнительный приемопередатчик 2 и на сигнальные входы анализатора 5 временных интервалов, в котором он проходит через сумматор 49 по шой 2 на вход синхронизации блока 50 памяти и устанавливает последний в нулевое состояние. Поэтому состояние входа 54 изменяется (сигнал низкого уровня), а следовательно, изменяется и состояние управляющих входов задающих приемопередатчиков 1.1 и 1.2, что свидетельствует о нормальной работе участка переключатель — задающий приемопередатчик 1.2 (при условии, что сигнал на входе 42 низкого уровня, а на выходе элемента ИЛИ-НЕ 35 высокого уровня).

Если же проверяемый участок оказывается неисправным (например, неисправен канал переключатель — задающий приемопередатчик 1.2 и(или) приемопередатчик не успел вьк тавить направление для подтверждейия), то по истечении времени Т. на выходе бло(г

55 ка 55 появляется сигнал высокого уровня, кс торый через элемент ИЛИ 57 поступает на выход 48 анализатора 6 и далее на второй управляющий вход блока 4 выбора направления передачи.

С управляющего входа через элемент ИЛИ-HE 35 сигнал с низким уровнем поступает на вторые входы элементов И-НЕ 31-34 и блокирует их выходы

15-18 и„ соответственно, направления передачи, сигнал подтверждения приемопередатчик 1,1 не получает.

В случае неисправности ((не снимается сигнал низкого уровня) одной или двух линий выбора задающий приемопередатчик 1.1 передает инициативу обмена информацией с исполнительным приемопередатчиком 2 задающему приемопередатчику 1.2.

При этом возможны ситуации не сни) мается сигнал низкого уровня с линии выбора А; не снимается сигнал низкого уровня с линии выбора D; на снимается сигнал низкого уровня с линии выбора А и D.

Первая ситуация означает, что задающий приемопередатчик 1.1 передает информацию исполнительному приемопередатчику 2 и должен открыть обратное направление передачи, сняв первоначальное. На управляющем входе приемопередатчика 1.1 при этом сигнал высокого уровня. Однако,так как первоначальное направление не снимается, то задающий приемопередатчик 1.1 повторно выдает информацию приемопередатчику 2 (и этим "со-. общает" о последующей передаче управления задающему приемопередатчику

1,2).

При повторной передаче информации сигнал на управляющем входе задающего приемопередатчика изменяет свое значение с высокого уровня на низкий. Затем задающий приемопередатчик 1.1 выставляет на второй управляющий вход D сигнал низкого уровня (значения логических переменных А = а, В = Ь, С = с, D = cl; комбинация 8 таблицы). При этом на управляющем входе 46 появляется сигнал низкого, а на втором входе 42 — сигнал высокого уровня, вследствие чего разрешение на работу блока 53 снимается. Передача информации задающему приемопередатчику 1.2 от задающего приемопередатчика 1.1 происходит аналогично описанному. Сигнал на

15 1223 управляющем входе 54 при этом изменяется с низкого уровня (установленного ранее при передаче с задающего приемопередатчика 1.1 к исполнительному приемопередатчику 2) на

5 высокий, и выдается разрешение" на работу блока 55. Если участок коммутатор 3 — канал — задающий приемопередатчик 1.2 неисправен, то через время Т на выходе блока 55 появВ ляется сигнал высокого уровня, обеспечивающий отключение направлений передачи (приема).

При нормальной работе задающий приемопередатчик 1.2, выставив сигнал низкого уровня на первый управляющий выход С, передает подтверждение задающему приемопередатчику

l.I (значение логических переменных А = а, В = b, С = с, D = й;ком- 20 бинация 9 таблицы).

При этом на втором входе 42 появляется сигнал низкого, а на втором входе 44 — сигнал высокого уровня. При передаче подтверждения 25 (в момент прохождения им коммутатора 3) сигнал на управляющем входе приемопередатчиков 1 ° 1 и 1.2 изменяется с высокого уровня на низкий, после чего приемопередатчик 1.2 открывает направление исполнительный приемопередатчик 2 — задающий приемопередатчик 1.2 и задающий приемопередатчик 1.1. Открытие указанного направления происходит следующим образом. Задающий приемопередатчик

I.2 по перепаду сигнала на управляющем входе с низкого уровня на высокий снимает сигнал низкого уровня с первого управляющего выхода С (зна40 чения логических переменных А = а, В = Ъ, С = с, D = d; комбинация 8 таблицы).и затем выставляет сигнал низкого уровня на управляющем выхоле В (значения логических переменных

А=а, B=b, C=c, D=d; комбинация 10 таблицы).

При снятии сигнала низкого уровня с управляющего выхода С на входе 44 появляется сигнал низкого уровня, а при выставлении сигнала низкого уровня на выходе В на входе 46 появляется сигнал высокого уровня. Одновременно открываются логические элементы 8 и 10 коммутаторов 3 по цепи: сигнальные входы А, В, D (низкий уровень) блока 4 выбора направления передачи, третий дешифратор

377 16

25 (высокий уровень на выходе 43), элементы ИЛИ 28 и 30, элементы ИНЕ 32 и 34, второй и четвертый выходы 16 и 18 блока 4 выбора направления передачи, соответствующие управляющие входы коммутаторов 3, управляющие входы логических элементов 8 и IО. После того, как открывается направление, исполнительный приемопередатчик 2 посылает в канал связи информацию подтверждения. Далее процесс приемопередачи осущест\ вляется аналогично описанному (описание режима I).

Вторая ситуация означает, что задающий приемопередатчик 1,1 передал ( информацию исполнительному приемопередатчику 2 и уже получил от него подтверждение. В этом случае задающий приемопередатчик 1.1 передает инициативу задающему приемопередатчику 1.2 аналогично описанному, за исключением повторной выдачи информации исполнительному приемопередатчику 2 перед выбором направления обмена с задающим приемопередатчиком

1. 2.

В рассмотренных первой и .второй ситуациях исполнительный приемопередатчик 2 контролирует обмен и передачу управления между задающими приемопередатчиками 1.1 и 1.2. Этот контроль предшедствует посылке им в канал связи информации подтверждения.

В третьей ситуации осуществляется приемопередача между задающим приемопередатчиком 1.2 и исполнительным приемопередатчиком 2. При этом задающий приемопередатчик 1.1 "прослушивает" всю информацию приемопередачи.

Режим 3. Этот режим работы устройства осущесвтляется для проверки канала связи на участке переключатель — задающий приемопередатчик 1.1. и (или) при неисправности (не снимается низкий уровень) одной или сразу двух линий выбора С или В задающего приемопередатчика 1.2, а также для "прослушивания" им зсей информации обмена между задающим приемопередатчиком 1.1 и исполнительньи приемопередатчиком 2.

Работа устройства в режиме 3 производится аналогично работе устройст" ва в режиме 2. При этом для передачи инициативы задающему приемопередатl7!

223377

20

30

40

55

«и .у !.1 используется четвертый дешифратор 26 блока 4 выбора направления передачи (значения логических переменных А = а, В =- Ь, С = с, D =

<1; комбинация .5 таблицы), для получения сигнала подтверждения от за. дающего приемопередатчика 1.1 используется второй дешифратор 24 (значения логических переменных А =

= а, В = Ь, C = с, D = d- комбинация

ll таблицы), а для получения сигнала подтверждения от исполнительного приемопередатчика 2 — третий дешифратор 25 (значения логических пе ременных А = а, В = Ь, С = с, D = д.; комбинация 6 таблицы).

Формула изобретения

l.Óñòðîéñòâî для контроля провоцных каналов связи по авт. св.

1! - 1135012, о т л и ч а ю щ е е с я тем, что,с целью увеличения глубины контроля и повышения надежности устройства, в него введен второй анализятор временных интервалов, выход которого подключен к второму управляющему входу блока выбора направ ления передачи, шестой выход которого подключен к второму входу блока сравнения первого анализатора вре менных интервалов, а седьмой и восьмой выходы подключены соответственно к первому и второму входам второго анализатора временных интервалов, управляющий вход которого соединен с первым выходом первого анализатора временных интервалов, блок выбора направления передачи выполнен в виде первого, второго, третьего и четвертого элементов НЕ, входы которых являются сигнальными входами блока направления передачи, первого, второго, третьего и четвертого дешифраторов, сигнальные входы каждого из которых соединены соответствен но с входами и выходами соответствующих элементов НЕ, первого элемента ИЛИ, первый вход которого соединен с первым выходом первого дешифратора, а второй вход соединен с выходом второго дешифратора, второго элемента ИЛИ, первый вход которого соединен с вторым выходом первого дешифратора, второй вход — с выходом второго дешифратора, а третий вход— с выходом третьего дешифратора, третьего элемента ИЛИ, первый вход которого соединен с третьим выходом первого дешифратора, а второй вход соединен с выходом четвертого дешифратора, четвертого элемента ИЛИ, первый вход которого соединен с четвертым выходом первого дешифратора, второй вход — с выходом третьего дешифратора, а третий вход — с выходом четвертого дешифратора, первого, второго, третьего и четвертого элементов И-НЕ, первый вход которых соединен с выходом соответствующего элемента ИЛИ, элемента ИЛИ-НЕ. выход которого подключен к вторым входам элементов И-НЕ, а первый и второй входы являются соответственно первым и вторым управляющими входами блока выбора направления передачи, пятого элемента ИЛИ, первый, второй, третий и четвертый входы которого соединены соответственно с первым, вторым, третьим и четвертым выходами первого дешифратора, а пятый вход соединен с выходом третьего дешифратора, и элемента И входы которого соединены с входами соответствующих элементов

НЕ, при этом выходы первого, второго, третьего и четвертого элементов

И-НЕ, а также элемента И, выход пятого элемента ИЛИ и выходы второго и четвертого дешифраторов являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым выходами блока выбора направления передачи.

2, Устройство по п.l, о т л и ч аю щ е е с я тем, что второй анализатор временных интервалов содержит элемент ИЛИ первый и второй блоки сравнения временных интервалов, при этом выходы первого и второго блоков сравнения временных интервалов подключены соответственно к первому и второму входам элемента ИЛИ, выход которого является выходом второго анализатора временных интервалов, первые входы первого и второго блоков сравнения временных интервалов объединены и являются управляющим входом второго анализатора временных интервалов, второй вход первого блока сравнения временных интервалов и второй вход второго блока сравнения временных интервалов являются соответственно первым и вторым входами второго анализатора временных интервалов.