Устройство для задержки импульсных сигналов

Иллюстрации

Показать всеРеферат

. Изобретение может быть исполь- ёовано в импульсных цифровых и радиотехнических устройствах для создания линейно изменяющейся задержки опорного импульсного сигнала, при W ff чем скорость нарастания задается цифровым кодом. Цель изобретения - расширение функциональных возможностей и повьшение быстродействия. Устройство содержит буферный регистр 1, накапливающий сумматор 2, счетчик импульсов 3, элемент ИЛИ 4, триггер 5, элементы И 6 и 8, элемент 7 задержки и генератор 9 тактовых импульсов . Введение в устройство буферного регистра, триггера элемента И 8 и элемента задержки позволило обеспечить линейно изменяющуюся задержку входных импульсов со скоростью, задаваемой цифровым кодом. Кроме того, осуществлена синхронизация установки кода задержки входными импульсами устройства.1 ил. (/)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (1П (51) 4 Н 03 К 3/64 5/13.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ и

Уст 0"

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3759003/24-21 (22) 28.06.84 (46) 15.04.86. Бюл. 11 14 (71) Ярославский государственный университет (72) Е.Н.Новиков (53) 621.373(088.8) (56) Важенина З.П. Методы и схемы временной задержки импульсных сигналов. М.: Советское радио, 1971, с. 139, рис. 3.4. (54) УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ ИМПУЛЬСНЫХ СИГНАЛОВ (57). Изобретение может быть использовано в импульсных цифровых и радиотехнических устройствах для создания линейно изменяющейся задержки опорного импульсного сигнала, причем скорость нарастания задается цифровым кодом. Цель изобретения расширение функциональных возможностей и повышение быстродействия.

Устройство содержит буферный регистр

1, накапливающий сумматор 2, счетчик импульсов 3, элемент ИЛИ 4, триггер

5, элементы И 6 и 8, элемент 7 задержки и генератор 9 тактовых импульсов. Введение в устройство буферного регистра, триггера элемента И 8 и элемента задержки позволило обеспечить линейно изменяющуюся задержку входных импульсов со скоростью, задаваемой цифровым кодом. Кроме того, осуществлена синхронизация установки кода задержки входными импульсами устройства.! ил.

1224988

Изобретение относится к импульсной технике и предназначено для использования в импульсных цифровых и радиотехнических устройствах для создания линейно изменяющейся за- $ держки опорного импульсного сигнала, причем скорость нарастания задается цифровым кодом.

Цель изобретения — расширение функциональных возможностей за счет IÎ обеспечения линейно изменяющейся задержки входных импульсов со скоростью, задаваемой цифровым кодом л повышение быстродействия за счет синхронизации установки кода задерж- 15 ки входными импульсами устройства.

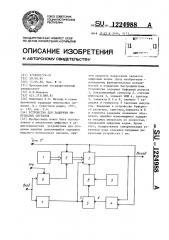

На чертеже представлена функциональная схема устройства для задержки импульсных сигналов.

Устройство для задержки импульс--. 2О ных сигналов содержит последовательно соединенные буферный регистр 1, накапливающий сумматор 2 и счетчик импульсов 3, выход переполнения которого соединен с выходной шиной уст- 25 ройства и через элемент ИЛИ 4 подклю. чен к нулевому входу триггера 5, элемент И 6, элемент задержки 7, элемент И 8, генератор 9 тактовых импульсов, причем входная шина устройства подключена к входу элемента задержки 7 и первому входу элемента

И 6, второй вход которого соединен с шиной управления, а выход элемен-. та И 6 подключен к синхронизирующе35 му входу накапливающего сумматора

2, установочный вход которого соединен с шиной установки исходного сос тояния, вторым входом элемента ИЛИ 4 и с установочным входом счетчика 3, синхронизирующий вход которого соединен с выходом элемента 7 задержки и единичным входом триггера 5, выход которого подключен к первому входу элемента И 8, второй вход которого соединен с выходом генератора 9 тактовых импульсов, а выход

И 8 подключен к счетному (вычитающему) входу счетчика 3.

Устройство для задержки импульсных сигналов работает следующим образом.

Для установки исходного состояния на вход устройства Уст.О" подается импульс, который устанавливает н ноль накапливающий сумматор 2, 55 счетчик 3 и триггер 5. Так как триггер 5 установлен в ноль (низкий уровень), тактовые импульсы с генератора 9 не проходят через элемент И 8 на вычитающий вход счетчика 3 и устройство находится в исходном состоянии. По приходу первого входного импульса накапливающий сумматор 2 изменит свое состояние на величину, хранящуюся в буферном регистре 1.

Эта информация появится на его выходе через время задержки накапливающего сумматора 2 и поступит на предустановочные входы счетчика 3. 3атем импульсом синхронизации, задержанным на время, большее, чем время задержки накапливающего сумматора 2, этот код перепишется в счетчик .3, одновременно этот же задержанный импульс установит в "1" (высокий уровень) триггер 5, что позволит импульсам с генератора 9 через элемент И 8 пройти на вычитающий вход счетчика 3. Время счета счетчика 3 определяется кодом, записанным по предустановочным входам счетчика 3., и периодом тактовых импульсов с генератора 9. По окончании счета с выхода переполнения счетчика 3 появится импульс, задержанный относительно импульса синхронизации на время t,=ïÒ, где n — код, записанный в счетчик 3, Т вЂ” период тактовых импульсов. Этот импульс являет-, ся выходным импульсом устройства.

Одновременно этот импульс через элемент ИЛИ 4 устанавливает триггер 5 в О 1, что запрещает дальнейшее прохождение тактовых импульсов с генератора 9 через элемент И 8 на вычитающий вход счетчика 3. Устройство находится в состоянии ожидания. Второй входной импульс, пройдя через элемент И 6, изменит состояние накапливающего сумматора 2 на величину скачка, хранящегося в буферном регистре 1, и его состояние на выходе будет равно предыдущему плюс код скачка, Эта информация опять через время с запишется импульсом синхронизации в счетчик 3, который установит триггер 5 в "1". Тактовые импульсы через элемент И 8 поступят на вычитающий вход счетчика 3, который будет уже считать время Л .= ь-Т больше, где л — скачок, Т вЂ” период тактовых импульсов. Так повторяется до тех пор, пока не переполнится накапливающий сумматор 2, причем, если в емкости накапливающего сумматора 2 укладывается целое число скач3 1224988

4 сов и первый Элемент И и счетчик им пульсов, отличающееся тем, что, с целью расширения функциональных возможностей и повышения быстродействия, в него введены буферный регистр, триггер, второй элемент И, элемент задержки и элемент

ИЛИ, причем входная шина соединена с входом элемента задержки и первым входом второго элемента И, второй вход которого подключен к шине управления, а выход соединен с входом формула изобретения

Устройство для задержки импульсных сигналов, содержащее накапливающий сумматор, последовательно соединенные генератор тактовых импульСоставитель Б.Кириллов

Редактор И.Стенина Техред Л.Олейник Корректор A.ÇèìîêîñoB

Заказ 1963/57

Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 ков, то переполнение накапливающего сумматора 2 эквивалентно установке исходного состояния, если нет, то он вернется не в нулевое состояние, а в состояние, равное остатку, и работа устройства будет продолжаться.

Если эта ситуация не желательна, то необходимо предусмотреть установку в "О" накапливающего сумматора 2 по

его переполнению. Таким образом, 1О устройство реализует линейно нарастающую задержку выходного импульса относительно импульса синхронизации.

В устройстве предусмотрен режим

"Остановка", когда на шину управления устройства подается низкий уровень "О", что запрещает прохождение входного импульса через элемент И 6 на вход синхронизации накапливающего сумматора 2. В этом режиме состоя- 2б ние накапливающего сумматора 2 остается не змеиным; что эквивалентно фиксированной задержке tqap =n Т, где n — состояние накапливающего сумматора 2. 25 синхронизации накапливающего сумматора, информационные входы которого соединены с выходами буферного регистра, а выходы накапливающего сумматора подключены к информационным входам счетчика импульсов, установочный вход которого соединен с шиной установки исходного состояния, установочным входом накапливающего сумматора и первым входом элемента ИЛИ, второй вход которого соединен с выходом переполнения счетчика импульсов и выходной шиной, а выход элемента ИЛИ подключен к нулевому входу триггера, выход которого соединен с вторым входом первого элемента И, а единичный вход триггера соединен с выходом элемента задержки и входом синхронизации счет- чика импульсов.