Синхронный делитель частоты на 10

Иллюстрации

Показать всеРеферат

Изобретение относится к ци$5йвой технике и может быть использовано при построении хронизаторов, цифровых синтезаторов частоты и т.д. Цель изобретения - расширение функциональных возможностей. Устройство содержит 1К-триггеры 1-А, элемент И 5, шину 6 сброса, тактовую шину 7 и выходную шину 8. Введение в устройство элемента И и образование новых связей между его элементами позволяет получить сигнал переноса и нулевого исходного состояния и сократить число связей, необходимых для сброса устройства. 2 ил.

COI03 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ Ъ

4 ф г

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3796478/24-21 (22) 04.10.84 (46) 15.04.86. Бюл. Р 14 (72) В.И.Мяснов (53) 621.374,44(088.8) (56) Лейнов М.Л. и др. Цифровые дели тели частоты на логических элементах

М,: Энергия, 1975 °

Авторское свидетельство СССР

9 1064478, кл. Н 03 К 23/02, 1.983. (54) GHHxPOHHhlA делительчАстоты HA 10 (57) Изобретение относится к цифровой технике и может быть использо„„SU„„1225009 A (50 4 .Н 03 К 23/24 вано при построении хронизаторов, цифровых синтезаторов частоты и т.д, Цель изобретения — расширение функциональных возможностей. Устройство содержит IK-триггеры 1-4, элемент

И 5, шину 6 сброса, тактовую шину 7 и выходную шину 8. Введение в устройство элемента И и образование новых связей между его элементами позволяет получить сигнал переноса и нулевого исходного состояния и сократить число связей, необходимых для сброса устройства. 2 ил.

1225009.

Изобретение относится к цифровой технике и может бьггь использовано при построении хронизаторов, цифровых синтезаторов частоты, электронных часов и т. п.

Цель изОбретения — расширение функциональных возможностей путем получения сигнала переноса и нулевого исходно"го состояния, при этом сокращается число связей, необходимых для сброса устройства.

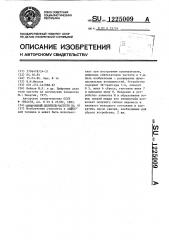

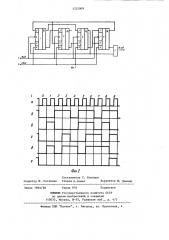

На фиг. 1 приведена функциональная схема синхронного делителя частоты на 10; на фиг, 2 — временные диаграммы работы устройства, где а входные тактовые импульсы на тактовой шине; 3 — сигнал Q в на прямом выходе первого IK-триггера; вв — сигнал

Г2 на прямом выходе Q второго IKтРиггеРа; 2 — сигнал э на пРЯмом выходе Q > третьего IK-триггера; в1 сигнал Q< на прямом выходе Я4 четвертого IK-триггера; 8 — сигнал переноса на выходе устройства.

Синхронный делитель частоты на 10 содержит четыре IK-триггера 1-4 и элемент 5 И, шину сброса 6, тактовую шину 7. Счетные входы .всех IK-триг.геров соединены с тактовой шиной 7 устройства, инверсный выход второго

IK-триггера 2 соединен с К-входом третьего IK-триггера 3, инверсный выход которого соединен с Х и Квходами четвертого ТК-триггера 4, первый и второй входы элемента 5 И соединены соответственно с прямым выходом третьего 3 и инверсным выходом четвертого 4 IK-триггера, а вы-. ход — с выходной шиной 8 устройства, при этом прямой выход четвертого

IK-триггера 4 соединен с I-входом первого IK-триггера 1, прямой выход которого соединен с I-входом третьего

IK-триггера 3, прямой выход которого соединен с К-входом первого IK-триггера 1, инверсный выход которого соединен с I-входом второго IK-триггера 2, К-вход которого соединен с прямым выходом четвертого IK-триггера 4.

При указанной .схеме соединения элементов логические уравнения I- u

К-входов всех IK-триггеров делителя частоты на 10 следующие

Ч е 4 2 вв 3 в в 4

Kg=Q4 в "в в2 в 4 Э".

По импульсу "Сброс" на шине 6 сброса все IK-триггеры устройства устанавливаются в исходное нулевое состояние. При этом состояния выходов равны (фиг. 2 при х=0)

На основании логических уравнений для I- u K-входов устройства состояния входов следующие

I =и -t 0" I =0 =»1» 4 2 ° е

I и =»0» ° Х -0 =«1» вв э y q t

Ф

=q =»1". К -q

1 2 э + Э

На фиг. 1 и 2 принято, что IK20 триггеры переключаются в противопо-. ложное состояние по отрицательному перепаду сигнала на счетном входе.

По первому тактовому импульсу первый ХК-триггер 1 не изменит своего

25 состояния (так как в исходном состоянии при i=p у него Хв =K --ееО»), вто,рой IK-триггер 2 переключится в состояние логической единицы (так как при ь=О Х2= 1, К2= О ) > ретий зп IK-триггер 3 не изменит своего состояния (так как при i=p I =»0» и K=«1", Я и первый тактовый импульс лишь подтвердит его нулевое состояние), четвертый IK-триггер 4 переключится в противоположное, единичное, состояние (так как при х=О I4=K4= 1 ) и состояния выходов (диаграммы на ,фиг. 2 при i=l) станут равны

llPll ° q ll 1 вв ° q tfptt

40 . 2 3 4

Изменяются и состояния входов ев1 вв ° Z II1tt I ееОвв Т tt1 tt °

2 9 в 4 ееQtt ° К вв 1 ее К вЂ” ttQtt ° К

В результате, после дейс гвия второго тактового импульса, устройство перейдет во второе состояние (фиг. 2 при i=2), характеризующееся следую5О щими значениями выходов и входов

=«1и». q =»0»в и =»âp». и цОц

-ееptt, Х иptt, Х «1ве. Х ее1ев

2 9 в 4

55 К =«0« ° К =»0« ° К =»1» ° К =»1»

2 в $ y 4

По третьему тактовому импульсу устройство переключится в третье сос. тояние (фиг. 2 при i.=3):

1225009

15

Q =!!1!! ° Q ="1!!

3 () ="1 ". (="0 ° Ч ="1 "° (Рассматривая и далее таким же образом работу синхронного делителя частоты на 10, получим все его состояния 5 при всех i.

По девятому тактовому импульсу устройство переходит в девятое состояние, в котором и наступает совпадение сигналов на входах элемента И 5, на выходе которого (на выходной шине 8) при

i=9 формируется сигнал переноса

П=qq,="1", уровень логической "1" которого удерживается в течение всего девятого 25 такта работы устройства. По десятому входному тактовому импульсу устройство возвращается в исходное состояние (фиг. 2, при i=O), совпадение нарушается, и на шине 8 формируется отрицательный перепад сигнала П-переноса, под действием которого другой делитель частоты, подключенный входом к шине 8, переключится в свое очередное состояние.

Использование предлагаемого син35 хронного делителя частоты на 10 позволит получить устройство с малым количеством элементов и связей цепей, в котором благодаря элементу И 5 на

40 выходе его можно для повышения коэффициента деления частоты включать И другие делители частоты, а благодаря предложенной схеме соединения выходов и I и К входов IK-тригге3 ров можно использовать IK-триггеры, имеющие только входы R установки триггеров в нулевое состояние, так как в исходном состоянии все IK-триггеры могут находиться в нулевом состоянии, в отличие от известного устройства, где необходима установка триггеров как в нулевое, так и в единичное состояние.

Формула из об ре те ния

Синхронный делитель частоты на 10, содержащий четыре IK-триггера, счетные входы каждого из которых соединены с тактовой шиной устройства, инверсный выход второго ЕК-триггера соединен-с К-входом третьего IK- p>irrepa, инверсный выход которого соединен с I и К- входами четвертого IKтриггера, отличающийся тем; что, с целью расширения функциональных возможностей путем обеспечения возможности получения сигнала переноса и нулевого исходного состояния устройства, в него введен элемент И, первый и второй входы которого соединены соответственно с прямым выходом третьего и инверсным выходом четвертого IK-триггеров, а выход элемента И является выходом переноса устройства, при этом прямой выход четвертого Ж-триггера соединен с К-входом второго IK-триггера и с

I-входом первого IK-триггера, прямой выход которого соединен с 1 -входом третьего IK-триггера, прямой выход которого соединен с К-входом первого

-IK-триггера, инверсный выход которого соединен с I-входом второго IKтриггера.

1225009

0 1 Г,У 4 Х E 7 8 У

Составитель С. Клевцов

Редактор И. Сегляник Техред 0.Сопко Корректор М. демчик

Заказ 1964/58 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4