Синхронный делитель частоты на 16

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой технике и может быть использовано при построении хронизаторов, цифровых синтезаторов частоты. Цель изобретения - повьппение надежности работы устройства. Устройство содержит J К -триггеры 1, 2, 3 и 4, элемент И 5, шину 6 сброса, тактовую шину 7 и выходные шины 8 и 9„ Устройство позволяет снизить вероятность воз-г никновения сбоев путем уменьшения числа элементов и связей при одновременном его упрощении. В описании приведены временные диаграммы работы устройства. 2 ил. 0tfe.f

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

У.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3797600/24-21 (22) 02.10.84 (46) 15.04.86. Бюл. У 14 (72) В.И.Мяснов (53) 621.374.44(088.8) (56) Будинский Я. Логические цепи в цифровой технике.Под ред. Б.А.Калабекова. М.: Связь, 1977.

Лейнов М.Л. и др. Цифровые делители частоты на логических элемен- . тах. М.: Энергия, 1975, с. 58, рис. 3.8 б. (54) СИНХРОННЬЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

НА 16

„„SU„„225010 A (51) 4 Н 03 К 23/24 (57) Изобретение относится к цифровой технике и может быть использовано при построении хронизаторов, цифровых синтезаторов частоты. Цель изобретения — повьппение надежности работы устройства. Устройство содержит 3К -триггеры 1, 2, 3 и 4, элемент

И 5, шину 6 сброса, тактовую шину 7 и выходные шины 8 и 9. Устройство позволяет снизить вероятность воз-. никновения сбоев путем уменьшения числа элементов и связей при одновременном его упрощении. В описании приведены временные диаграммы работы устройства. 2 ил.

12? 5010

Изобретение относится к цифровой технике и может быть использовано при построении хронизаторов, цифровых синтезаторов частоты.

Цель изобретения — повышение надежности работы устройства за счет снижения вероятности возникновения сбоев путем уменьшения числа элементов и связей, что одновременно приводит к упрощению устройства.

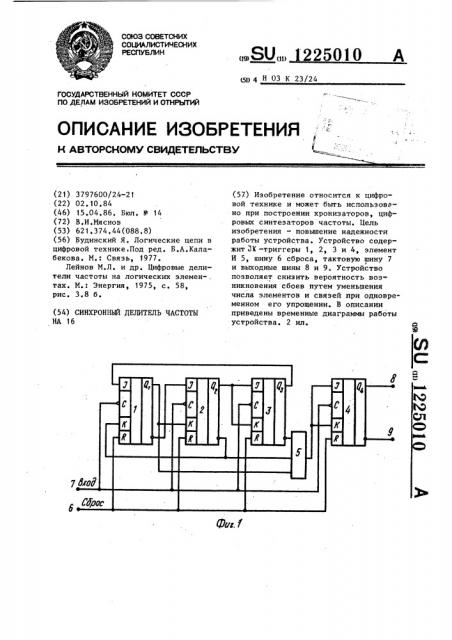

На фиг. 1 приведена функциональная схема синхронного делителя частоты на 16; на фиг. 2 — временные диаграммы работы предлагаемого синхронного делителя частоты на 16, где о — входные тактовые импульсы на тактовой шине; о — сигнал Q на пря- мом выходе Qt первого 3 V -триггера;

Π— сигнал 02 на прямом выходе Я2 второго К вЂ”; 2 -сигнал Q на прямом выходе q> третьего " -три;гера; — сигнал 04 на прямом выходе четвертого 3К -триггера.

Синхронный делитель частоты на

16 содержит четыре Jk -триггера 1-4, элемент И 5, шину сброса, тактовую шину 7, выходные шины 8 и 9. Счетные входы всех 3k -триггеров 1-4 соеди-ены с тактовой шиной 7 устройства, выходы R всех JK -триггеров 1-4 соединены с шиной 6 сброса устройства, выходы четвертого К -триггера 4 являются выходными шинами 8 и 9 уст-. ройства. В предлагаемом устройстве

3 вход первого 3К -триггера 1 соединен с прямым выходом третьего, jt(;òðèãrepa 3, и К. входыкоторого соединены с прямым выходом второго 7 К -триггера 2, 1 вход которого соединен с инверсным выходом первого 1 -триггера 1, инверсный выход второго 3k -триггера 2 соединен со вторым входом элемен- та И 5 и К входом второго. j/(,-триггера 2, инверсный выход третьего lk -триггера 3 соединен .с Э и К входами четвертого dk -триггера 4.

Устройство работает следующим образом.

При указанной схеме соединения элементов логические уравнения для

3 и k входов всех 3К -триггеров синхронного делителя частоты на 16 следующие

Х =О; I = ; ХЭ=О 3 I4=q<0 Оз

Р2, К2 qt Э 2 4 4 2 3

По сигналу "Сброс", поступающему в виде импульса по шине 6 сброса, Ф все К -триггеры 1-4 устанавливаются в исходное нулевое положение. При

5 этом состояния выходов будут равны (фиг. 2 при i 0) О «и0и ° q ttpll ° q ttplt ° q llptl 1 Z 9 4

На основании логических уравнений для 3 и К входов К -триггеров состо. яния входов следующие

I. =Я иОи °

Э Ф

=(1 =" 1" °

15

=и0и °

° 2 э

I =Q О О =иОи

Ю

lt 1 lt ° K, 1 «llptl °

° 2 $ Э 42 У

Ю К =() =и0и ° К =О О О =иОи.

4 2 4 1 ° 2 Э

0 ttptl ° q и 1 tt q llptl ° q llptt

° 2,s Э ю 4 °

4О Изменятся и состояния входов иpи ° I ll1 и ° I «и1 ™ ° f и0и ° в 2 ю Э s 4 э

K =и0и К =иОи К =и1и K =и0и

s 2 э Э s +

В результате по следующему второму, тактовому импульсу устррйство перейдет в свое второе состояние (фиг. 2 при i=2) которое будет характеризоваться следующими значениями выходов и входов 31(-триггеров

Itptt ° д lt 1 ll ° 0 «tl 1 ll ° 2 9 4

I =иОи

1и ° I и1и ° и1и °

2 3

К = 0" ф в при i=3) станут

55 К. =иОи К =и0" K =и1и

2 в Э е

В третьем такте (Лиг. 2 соатояния выходов и входов равны

На фиг. 1 и 2 принято, moJK-триггеры переключаются в противоположное состояние по счетному входу по отри25 цательному перепаду на счетном входе.

По первому тактовому импульсу.на шине 7 изменит свое состояние, т.е. переключится в состояние и1", только второй д" -триггер 2 (так как б2 =и1", 30 а K = иОи), а остальные ЗК -триггеры 1, 2 и 4 не изменят своего состояния (так как в предыдущем так- .

«и0и, K «и1и. т «tlptt, К и0и °

I4- 0; К4 — 0 ) . IIpH этом сОстОЯния выходов станут равны (диаграммы на фиг. 2 при i=1) 1225010

0 !11 !! 0 !!1!! Q !!0 ° 0 !!0 °

0 ° Z — !!0!! ° $ l! f T! ° g О

1 2

К =-"О" К ="1" К ="1" К ="О" э э У 4 Формула изобретения д

Составитель С. Клевцов

Редактор И. Сегляник Техред О.Сопко Корректор С. Черни

Заказ 1964/58 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Рассматривая и далее таким же образом работу синхронного делителя частоты на 16, получим все состояния выходов и входов каждого 3k -триггера

1-4 при всех i согласно фиг. 2. Использование предлагаемого синхронного делителя частоты на 16 по сравнению с известным устройством позволяет уменьшить количество элементов и связей, повысить надежность работы устройства при одновременном его упрощении.

Синхронный делитель частоты на 16 „ содержащий четыре -триггера и элемент И, счетные входы всех !<— триггеров соединены с тактовой шило!! устройства, входы k всех1K -триггеров соединены с шиной сброса устройства, выходы четвертого 3К -триггера являются выходными шинами устройства, причем прямой выход первого

3К-триггера соединен с К входом второго -триггера и первым входом элемента И, выход которого соединен

1р с д и K входами четвертого " -триггера, отличающий ся тем, что, с целью повьш ения надежности работы при с1дновременном упрощении устройства, прямой выход второго 3К -триггера соединен с и К входами третьего 3k -триггера, прямой выход которого соединен с 2 входом первого / -триггера, инверсный выход которого соединен с2 входом второгоУКтриггера, инверсный выход которого соединен с вторым входом элемента!и входом первого 3 -триггера, а инверсный выход третьего 3К -триггера — с третьим входом элемента И.