Устройство микропрограммного управления

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и предназначено для применения в устройствах управления цифровых вычислительных, машин с микропрограммным управлением, в частности в устройствах управления графическими дисплеями.Цель изобретения - сокращение оборудования за счет уменьшения объема памяти при многоуровневом ветвлении. Цель изобретения достигается за счет введения в устройство регистровой памяти ветвлений и группы коммутаторов ветвлений с соответствующими функциональными связями между ними и известными блоками устройства. 1 з.п. ф-лы, 1 ил. I со N: ю 05 4 сл со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPCHOIVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 3742295/24- 24 (22) 17.05.84 (46) 23.04.86. Бюл. 9 15 (71) Киевский научно-исследовательский и конструкторский институт периферийного оборудования (72) В.Ф. Каплун, Ю.M. Омельянчук, С.А. Сергиенко и В.Д. Тукаленко (53) 681.325 (088.8) (56) Авторское свидетельство СССР

У 669984, кл. G 06 F 9/22, 1977.

Авторское свидетельство СССР

В 503240, кл. С 06 F 9/22, 1976.

„.SU„„1226453 Д .цп4 G 06 F 9/22 (54) УСТРОЙСТВО МИКРОПРОГРАММНОГО

УПРАВЛЕНИЯ (57) Изобретение относится к области вычислительной техники и предназначено для применения в устройствах управления цифровых вычислительных машин с микропрограммным управлением, в частности в устройствах управления графическими дисплеями. Цель изобретения — сокращение оборудования за счет уменьшения объема памяти при многоуровневом ветвлении. Цель изобретения достигается за счет введения в устройство регистровой памяти ветвлений и группы коммутаторов ветвлений с соответствующими функциональными связями между ними и известными блоками устройства. 1 з.п. е ф-лы, 1 ил.

1226453

Изобретение относится к области вычислительной техники и предназначено для применения в устройствах управления цифровых вычислительных машин с микропрограммным управлением, в частности в устройствах управления графическими дисплеями.

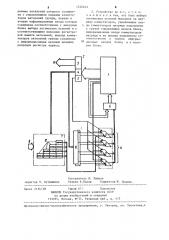

Целью изобретения является сокращение оборудования за счет уменьшения объема памяти при многоуровневом ветвлении, На чертеже приведена структурная схема предлагаемого устройства микропрограммного управления.

Устройство содержит память 1 микрокоманд, регистр 2 микрокоманд,содержащий выход 3 поля микроопераций, выход 4 поля ветвлений и выход 5 кода режима ветвления, регистр 6 адреса, блок 7 выбора логических условий, группу 8 входов логических условий, группу коммутаторов 9 ветвлений, регистровую память 10 ветвлений и группу 11 выходов. Блок 7 содержит матрицу коммутаторов 12 °

Устройство работает следующим образом.

По группе 8 входов в устройство поступают сигналы, от значения которых зависит алгоритм выполняемых в устройстве микропрограмм. Этими сигналами являются: код операции машинной команды, поступающий с регистра числа оперативной памяти, признаки, определяющие результаты выполнения текущей и предыдущих микрокоманд, сигналы состояния процессора, оперативной памяти, внешних устройств, различного спецоборудования, сигналы, поступающйе с панели управления ЦВМ,и т.д.

Цикл выполнения микрокоманды осуществляется путем считывания из памяти 1 микрокоманд кода очередной микрокоманды, которая содержит управляющую и адресную части. В адресной части указывается К -разрядный адрес следующей микракоманды,, причем

i:,ìëàäøèõ разрядов адреса могут модифицироваться в процессе выполнения микрокоманды, а старшие К- разрядов адреса поступают непосредственно на регистр б адреса. Управляющая часть микрокоманды записывается в регистр 2 микрокоманд, при этом код выхода 3 поля микроопераций регистра 2 поступает на выходы 11 устройства и управляет микрооперациями

l5

ЗО

55 в блоках ЦВИ, а выхоцы 4 и 5 управляют формирова.вием млацших разрядов адреса слецуюшей микрокоманды.

После завершения формирования младших разрядов адреса микрокоманды, время которого определяется временем задержки элементов в блоке 7 и в коммутаторах 9,новый адрес заносится в регистр 6 адреса. Через некоторое время, определяемое задержкой сигналов в памяти 1 микрокоманд, на его выходах появляется код следующей микрокоманды, который снова заносится в регистр 2 микрокоманде. Занесение в регистры 2 и 6 осуществляется по сигналам, периодически поступающим с генератора тактовых импульсов (не показан).

При безусловном слецовании последовательности микрокоманд в поле 5 микрокоманды задается такой код, при поступлении которого на управляющие входы коммутаторов 9 на их выходы будут передаваться значения младших разрядов адресной части микрокоманды. Таким образом, адрес следующей микрокоманды будет полностью определяться адресным полем выполняемой микрокоманды.

При необходимости изменения порядка следования микрокоманд в зависимости от значения каких-либо усJIoBHA в поле 5 микрокоманды задается код, который подключает на выходы коммутаторов 9 сигналы с выходов блока 7, а в поле 6 — код, под воздействием которого на выход блока 7 передаются сигналы анализируемых условий, выбранные иэ множества условий, поступающих по группе

8 входов. Таким образом, адрес следующей микрокоманды определяется в зависимости от значения анализируемых условий.

При необходимости обращения к микроподпрограмме выполняется микрокоманда, которая заносит в К -й регистр 10 памяти код, однозначно соответствующий той точке алгоритма, из которой осуществляется переход в микроподпрограмму. Управление записью в регистры ветвления осуществляется кодом в поле 4 микрокоманды, для чего в этом поле выделяется специальный бит, единица в котором вызывает запись в один из регистров (при нулевом его значении состояние регистров не изменяется), а осталь1226453

40 ные разряды поля 4 определяют заносимую информацию и номер регистра,в который производится запись. При этом код в поле 5 микрокоманды задает прохождение в младшие разряды регистра 6 адреса сигналов с адресной части микрокоманды, поэтому состояние сигналов на входах и выходах блока 7 безразлично. В адресном поле

10 данной микрокоманды указывается адрес первой микрокоманды нужной микропрограммы. В конце микропрограммы вводится микрокоманда условного перехода по значению g -го регистра 10 памяти, передача значений которого

15 в младшие разряды регистра 6 адреса задается полем 5 этой микрокоманды.

Таким образом, по коду, предварительно занесенному в.К -й регистр, осуществляется выход иэ микроподпрограммы с возвращением в ту точку алгоритма, из которой произошло к ней обращение. Во время выполнения микроподпрограммы возможен переход к

25 другой микроподпрограмме с использованием какого-либо иного регистра 10 памяти и т.д.

Цикл обработки машинных команд осуществляется следующим образом.

Стробирующие сигналы записи посту— пают на регистр 2 микрокоманд и регистр 6 адреса постоянно, и выборка микрокоманд из памяти 1 осуществляется непрерывно.

После пуска ЦВМ, как правило,вы- 35 полняются микрокоманды условных переходов по сигналам, поступающим с пульта управления ЦВМ, в результате чего выбирается микропрограмма отработки заданного режима работы и формируется адрес начала программы в оперативной памяти. Затем осущеt ствляется выборка команды и выполняется одно или несколько микрокоманд условного перехода по сигналам 45 кода команды, поступающим с регистра числа оперативной памяти по группе

8 входов устройства. B результате выполнения этих микрокоманд выбирается микропрограмма отработки выбранной команды, после завершения которой из оперативной памяти выбирается новая команда.

При отработке команды, которая влияет на выполнение последующих ко- 55 манд, производится занесение в один или несколько регистров 10 памяти кодов, однозначно соответствующих информации данной команды, а перед отработкой команд, зависящих от пре. дыдущих, выполняются микрокоманды условного перехода по значению тех регистров, в которых хранится информация о задающей" команде.

В случаях, когда при отработке какой-либо команды необходимо изменить состояние регистра числа оперативной памяти, а затем снова ветвиться по коду отрабатываемой команды, также производится предварительная запись кодов, определяющих данную команду, в регистры 10 памяти и впоследствии ветвление осуществляется не по сигналам регистра числа памяти, а по значению соответствующих регистров 10 памяти.

Формула изобретения

1. Устройство микропрограммного управления, содержащее память микрокоманд, регистр адреса, блок выбора логических условий и регистр микрокоманд, причем выход поля микроопераций регистра микрокоманд является выходом устройства, группа выходов поля ветвлений регистра микрокоманд соединена с группой управляющих входов блока выбора логических условий, группа информационных входов которого подключена к группе входов логических условий устройства, выход поля операции памяти микрокоманд соединен с информационным входом регистра микрокоманд, адресный вход памяти микрокоманд соединен с выходом регистра адреса, информационные входы старших разрядов которого подключены к выходам поля адреса памяти микрокоманд, о т л и ч а ю щ е е с я тем, что, с целью сокращения оборудования за счет уменьшения объема памяти микрокоманд при многоуровневом ветвлении, оно содержит регистровую память ветвлений и группу коммутаторов ветвлений, причем вы- . ходы кода ветвлений поля ветвлений регистра микрокоманд соединены с информационными входами регистровой памяти ветвлений, адресные входы и вход чтения записи которой соединены соответственно с выходами кода номера уровня ветвления поля ветвления регистра микрокоманд и с выходом признака режима поля ветвлений регистра микрокоманд, выходы кодл

1226453

Составитель 10. Ланцов

Техред В.Кадар Корректор И. Эрдейи,, ецактор Т. Кугрышева

Тираж б71 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35„ Раушская наб., д. 4/5

Заказ 2134/48

Производственно-полиграфическое предприятие„ г. Ужгород, ул . Проектная,4 режима ветвлений которого соединены с управляющими входами коммутаторов ветвлений группы, первые и вторые информационные входы которых соединены соответственно с выходами блока выбора логических условий и с соответствующими выходами регистровой памяти ветвлений, выходы коммутаторов ветвлений группы соединены с информационными входами младших разрядов регистра адреса.

2. Устройство по п.1, о т л ич а ю щ е е с я тем, что блок выбора логических условий выполнен на матрице коммутаторов, управляющие вхо5 ды коммутаторов матрицы подключены к группе управляющих входов блока, информационные входы коммутаторов матрицы и их выходы подключены соответственно к группе информационных входов блока и к выходам блока.